Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## XE8805/05A - SX8805R Sensing

# Machine – Data Acquisition with 16+10 bit ZoomingADC™ and buffered DACs

#### **General Description**

The XE8805A is a data acquisition ultra low-power low-voltage system on a chip (SoC) with a high efficiency microcontroller unit embedded (MCU), allowing for 1 MIPS at 300uA and 2.4 V, and multiplying in one clock cycle.

The XE8805A includes a high resolution acquisition path with the 16+10 bits ZoomingADC and two buffered DACs.

The XE8805A is available with on chip ROM (the SX8805) or Multiple-Time-Programmable (MTP) program memory.

#### **Applications**

- Portable, battery operated instruments

- Current loop powered instruments

- · Wheatstone bridge interfaces

- Pressure and chemical sensors

- HVAC control

- Metering

- · Sports watches, wrist instruments

#### **Key product Features**

- Low-power, high resolution ZoomingADC

- 0.5 to 1000 gain with offset cancellation

- up to 16 bits analog to digital converter

- up to 13 inputs multiplexer

- Low-voltage low-power controller operation

- 2 MIPS with 2.4 V to 5.5 V operation

- 300 μA at 1 MIPS over voltage range

- 22 kByte (8 kInstruction) MTP

- 520 Byte RAM data memory

- RC and crystal oscillators

- 5 reset, 22 interrupt, 8 event sources

- 8 bit and 16 bit buffered DACs

- 100 years MTP Flash retention at 55°C

#### **Ordering Information**

| •              |                       |             |         |

|----------------|-----------------------|-------------|---------|

| Product        | Temperature range     | Memory type | Package |

| XE8805MI028*   | 8* -40°C to 85 °C MTP |             | LQFP64  |

| XE8805AMI000   | -40°C to 85 °C        | MTP         | die     |

| XE8805AMI028LF | -40°C to 85 °C        | MTP         | LQFP64  |

| SX8805Rxxx     | -40°C to 85 °C**      | ROM         |         |

<sup>\*</sup>Not for new designs

Rev 1 January 2006 www.semtech.com

<sup>\*\*</sup>Extended temperature range on request

Chapter 21

Chapter 22

## **TABLE OF CONTENTS**

| Chapter 1  | XE8805/05A Overview                              |

|------------|--------------------------------------------------|

| Chapter 2  | XE8805/05A Performance                           |

| Chapter 3  | XE8805/05A CPU                                   |

| Chapter 4  | XE8805/05A Memory                                |

| Chapter 5  | System Block                                     |

| Chapter 6  | Reset generator                                  |

| Chapter 7  | Clock generation                                 |

| Chapter 8  | Interrupt handler                                |

| Chapter 9  | Event handler                                    |

| Chapter 10 | Low power RAM                                    |

| Chapter 11 | Port A                                           |

| Chapter 12 | Port B                                           |

| Chapter 13 | Port C                                           |

| Chapter 14 | Universal Asynchronous Receiver/Transmitter (UAF |

| Chapter 15 | Universal Synchronous Receiver/Transmitter (USR) |

| Chapter 16 | Acquisition Chain (ZoomingADC™)                  |

| Chapter 17 | Voltage multiplier                               |

| Chapter 18 | Signal D/A (DAS)                                 |

| Chapter 19 | Bias D/A (DAB)                                   |

| Chapter 20 | Counters/Timers/PWM                              |

|            |                                                  |

The Voltage Level Detector

XE8805/05A Dimensions

2ecollinoesi Recollino

© Semtech 2006 www.semtech.com

.

#### WIRELESS AND SENSING PRODUCTS

#### 1. General Overview

#### **CONTENTS**

| <b>1.1</b><br>1.1.1<br>1.1.2 | Top schematic General description XE8805 vs XE8805A | <b>1-2</b><br>1-2<br>1-4 |

|------------------------------|-----------------------------------------------------|--------------------------|

| <b>1.2</b><br>1.2.1<br>1.2.2 | Pin map Bare die LQFP-64                            | <b>1-4</b><br>1-4<br>1-5 |

| 1.3                          | Pin assignment                                      | 1-6                      |

| ,                            |                                                     |                          |

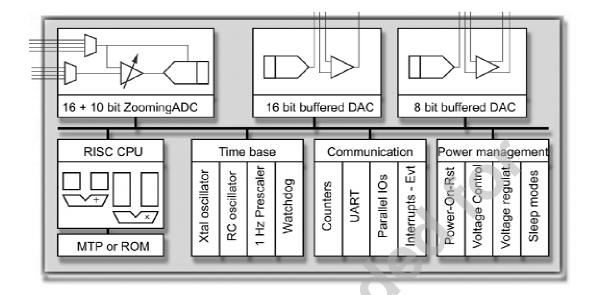

#### 1.1 Top schematic

#### 1.1.1 General description

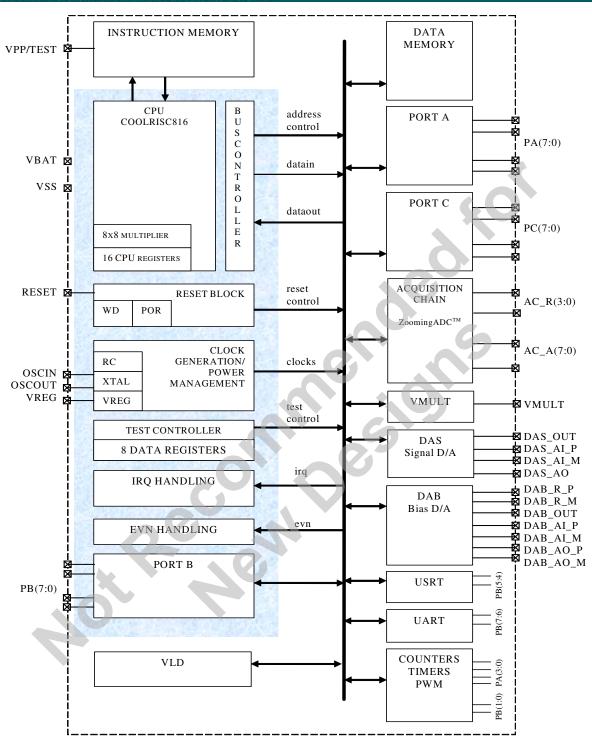

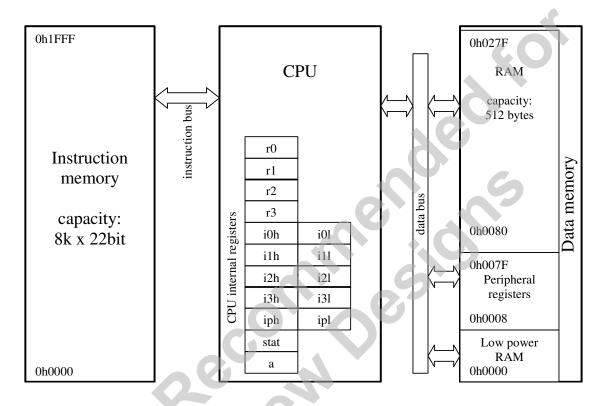

The top level block schematic of the circuit is shown in Figure 1-1. The heart of the circuit consists of the Coolrisc816® CPU core. This core includes an 8x8 multiplier and 16 internal registers.

The bus controller generates all control signals for access to all data registers other than the CPU internal registers.

The reset block generates the adequate reset signals for the rest of the circuit as a function of the set-up contained in its control registers. Possible reset sources are the power-on-reset (POR), the external pin RESET, the watchdog (WD), a bus error detected by the bus controller or a programmable pattern on Port A. Different low power modes are implemented.

The clock generation and power management block sets up the clock signals and generates internal supplies for different blocks. The clock can be generated from the RC oscillator (this is the start-up condition), the crystal oscillator (XTAL) or an external clock source (given on the OSCIN pin).

The test controller generates all set-up signals for different test modes. In normal operation, it is used as a set of 8 low power data registers. If power consumption is important for the application, the variables that need to be accessed very often should be stored in these registers rather than in the RAM.

The IRQ handler routes the interrupt signals of the different peripherals to the IRQ inputs of the CPU core. It allows masking of the interrupt sources and it flags which interrupt source is active.

Events are generally used to restart the processor after a HALT period without jumping to a specified address, i.e. the program execution resumes with the instruction following the HALT instruction. The EVN handler routes the event signals of the different peripherals to the EVN inputs of the CPU core. It allows masking of the interrupt sources and it flags which interrupt source is active.

The Port B is an 8 bit parallel IO port with analog capabilities. The URST, UART, and PWM block also make use of this port.

The instruction memory is a 22-bit wide flash or ROM memory depending on the circuit version. Flash and ROM versions have both 8k instruction memory. The data memory of this product is 512 byte SRAM.

The Acquisition Chain is a high resolution acquisition path with the 16+10 bit fully differential ZoomingADC™. The VMULT (voltage multiplier) powers a part of the Acquisition Chain.

The signal D/A (DAS) is a 16 bit D/A based on sigma-delta modulation. It includes a stand-alone amplifier that can be used for analog output filtering.

The bias D/A (DAB) is an 8 bit low frequency D/A. It includes a stand-alone amplifier that is used to drive large currents. It can be used to bias a sensor.

The Port A is an 8 bit parallel input port. It can also generate interrupts, events or a reset. It can be used to input external clocks for the timer/counter/PWM block.

The Port C is a general purpose 8 bit parallel I/O port.

The USRT (universal synchronous receiver/transmitter) contains some simple hardware functions in order to simplify the software implementation of a synchronous serial link.

Figure 1-1. Block schematic of the XE8805/05A circuit.

The UART (universal asynchronous receiver/transmitter) contains a full hardware implementation of the asynchronous serial link.

The counters/timers/PWM can take their clocks from internal or external sources (on Port A) and can generate interrupts or events. The PWM is output on Port B.

The VLD (voltage level detector) detects the battery end of life with respect to a programmable threshold.

#### 1.1.2 XE8805 vs XE8805A

The XE8805A has a new RESET pin function. The action of the RESET pin of the XE8805A resets the clock registers too and creates an additional short delay. See the RESET chapter for more information.

#### 1.2 Pin map

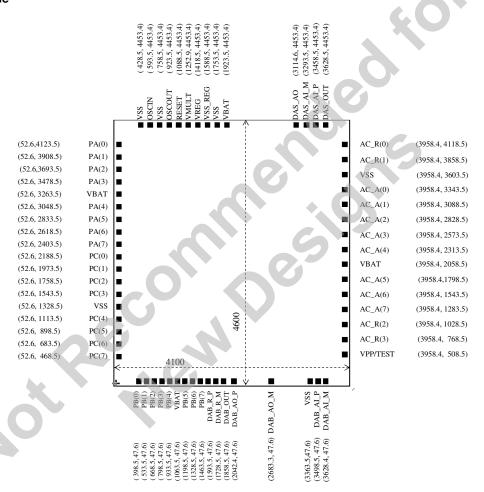

#### 1.2.1 Bare die

Figure 1-2. Die dimensions and pin coordinates (in μm)

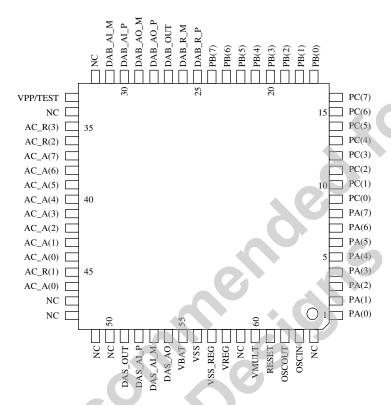

#### 1.2.2 LQFP-64

The XE8805/05A is delivered in a LQFP-64 package. The pin map is given below.

Figure 1-3. LQFP-64 pin map

| Package pin | name  | Package pin | name     |

|-------------|-------|-------------|----------|

| 1           | PA(0) | 33          | VPP/TEST |

| 2           | PA(1) | 34          | NC       |

| 3           | PA(2) | 35          | AC_R(3)  |

| 4           | PA(3) | 36          | AC_R(2)  |

| 5           | PA(4) | 37          | AC_A(7)  |

| 6           | PA(5) | 38          | AC_A(6)  |

| 7           | PA(6) | 39          | AC_A(5)  |

| 8           | PA(7) | 40          | AC_A(4)  |

| 9           | PC(0) | 41          | AC_A(3)  |

| 10          | PC(1) | 42          | AC_A(2)  |

| 11          | PC(2) | 43          | AC_A(1)  |

| 12          | PC(3) | 44          | AC_A(0)  |

| 13          | PC(4) | 45          | AC_R(1)  |

| 14          | PC(5) | 46          | AC_R(0)  |

| 15          | PC(6) | 47          | NC       |

| 16          | PC(7) | 48          | NC       |

| 17          | PB(0) | 49          | NC       |

| 18          | PB(1) | 50          | NC       |

| 19          | PB(2) | 51          | DAS_OUT  |

| 20          | PB(3) | 52          | DAS_AI_P |

| Package pin | name     | Package pin | name     |

|-------------|----------|-------------|----------|

| 21          | PB(4)    | 53          | DAS_AI_M |

| 22          | PB(5)    | 54          | DAS_AO   |

| 23          | PB(6)    | 55          | VBAT     |

| 24          | PB(7)    | 56          | VSS      |

| 25          | DAB_R_P  | 57          | VSS_REG  |

| 26          | DAB_R_M  | 58          | VREG     |

| 27          | DAB_OUT  | 59          | NC       |

| 28          | DAB_AO_P | 60          | VMULT    |

| 29          | DAB_AO_M | 61          | RESET    |

| 30          | DAB_AI_P | 62          | OSCOUT   |

| 31          | DAB_AI_M | 63          | OSCIN    |

| 32          | NC       | 64          | NC       |

Table 1-1. Bonding plan of the LQFP-64 package (LQFP 64L 10x10mm thick 1.6 mm)

### 1.3 Pin assignment

The table below gives a short description of the different pin assignments.

| Pin          | Assignment                                                               |

|--------------|--------------------------------------------------------------------------|

| VBAT         | Positive power supply                                                    |

| VSS VSS_REG  | Negative power supply                                                    |

| VREG         | Connection for the mandatory external capacitor of the voltage regulator |

| VPP/TEST     | High voltage supply for flash memory programming (NC in ROM versions)    |

| RESET        | Resets the circuit when the voltage is high                              |

| OSCIN/OSCOUT | Quartz crystal connections, also used for flash memory programming       |

| PA(7:0)      | Parallel input port A pins                                               |

| PB(7:0)      | Parallel I/O port B pins                                                 |

| PC(7:0)      | Parallel I/O port C pins                                                 |

| AC_A(7:0)    | Acquisition chain input pins                                             |

| AC_R(3:0)    | Acquisition chain reference pins                                         |

| VMULT        | Connection for the external capacitor if VBAT is below 3V                |

| DAB_OUT      | Bias D/A output                                                          |

| DAB_R_x      | Bias D/A reference (x=P: plus, x=M: minus)                               |

| DAB_Ax_y     | Bias D/A amplifier IO (x=1: input, x=0: output; y=P: plus, y=M: minus)   |

| DAS_OUT      | Signal D/A output                                                        |

| DAS_AI_x     | Signal D/A amplifier inputs (x=P: plus, x=M: minus)                      |

| DAS_AO       | Signal D/A amplifier output                                              |

Table 1-2. Pin assignment

Table 1-3 gives a more detailed pin map for the different pins. It also indicates the possible I/O configuration of these pins. The indications in blue bold are the configuration at start-up.

The pins CNTx pins are possible counter inputs, PWMx are possible PWM outputs.

| pin      | function           |         |       | 1/0      | conf              | iaur | ation | 1        |          |       |

|----------|--------------------|---------|-------|----------|-------------------|------|-------|----------|----------|-------|

| Pill     | idilolloll         |         |       | 1/0      | I/O configuration |      |       |          |          |       |

| lqfp-64  | first              | second  | third | ΑI       | AO                | ⊡    | 00    | OD       | PU       | POWER |

| 1        | PA(0)              | CNTA    |       |          |                   | X    |       |          | Χ        |       |

| 2        | PA(1)              | CNTB    |       |          |                   | X    |       |          | Χ        |       |

| 3        | PA(2)              | CNTC    |       |          |                   | X    |       |          | Χ        |       |

| 4        | PA(3)              | CNTD    |       |          |                   | X    |       |          | Χ        |       |

| 5        | PA(4)              |         |       |          |                   | X    |       |          | Χ        |       |

| 6        | PA(5)              |         |       |          |                   | X    |       |          | Χ        |       |

| 7        | PA(6)              |         |       |          |                   | X    |       |          | Х        |       |

| 8        | PA(7)              |         |       |          |                   | X    |       |          | Х        |       |

| 9        | PC(0)              |         |       |          |                   | X    | Χ     |          |          |       |

| 10       | PC(1)              |         |       |          |                   | X    | Χ     |          |          |       |

| 11       | PC(2)              |         |       |          |                   | X    | Χ     |          |          |       |

| 12       | PC(3)              |         |       |          |                   | X    | Χ     |          |          |       |

| 13       | PC(4)              |         |       |          |                   | X    | Χ     |          |          |       |

| 14       | PC(5)              |         |       |          |                   | X    | X     |          |          |       |

| 15       | PC(6)              |         |       |          |                   | X    | Χ     |          |          |       |

| 16       | PC(7)              |         |       |          |                   | X    | X     |          |          |       |

| 17       | PB(0)              | PWM0    |       | Х        | X                 | X    | Χ     | Х        | Χ        |       |

| 18       | PB(1)              | PWM1    |       | X        | X                 | X    | X     | X        | X        |       |

| 19       | PB(2)              |         |       | X        | X                 | X    | Х     | Χ        | X        |       |

| 20       | PB(3)              |         |       | X        | X                 | X    | Χ     | Χ        | X        |       |

| 21       | PB(4)              | USRT_S0 |       | X        | Χ                 | X    | Χ     | X        | Х        |       |

| 22       | PB(5)              | USRT_S1 |       | Х        | Χ                 | X    | Χ     | X        | Х        |       |

| 23       | PB(6)              | UART_Tx |       | X        | X                 | X    | X     | Х        | Х        |       |

| 24       | PB(7)              | UART_Rx |       | X        | Χ                 | X    | Χ     | Χ        | Χ        |       |

| 25       | DAB_R_P            |         |       | X        |                   |      |       |          |          |       |

| 26       | DAB_R_M            |         |       | X        | ```               |      |       |          |          |       |

| 27       | DAB_OUT            | AV      |       |          | X                 |      |       |          |          |       |

| 28       | DAB_AO_P           |         |       |          | X                 |      |       |          |          |       |

| 29       | DAB_AO_M           |         |       | <u> </u> | X                 |      |       |          |          |       |

| 30       | DAB_AI_P           |         |       | X        |                   |      |       |          |          |       |

| 31       | DAB_AI_M           | TEOT    |       | X        |                   |      |       |          |          |       |

| 33       | VPP                | TEST    |       | V        |                   |      |       |          |          | X     |

| 35       | AC_R(3)            |         |       | X        |                   |      |       |          |          |       |

| 36       | AC_R(2)            |         |       | X        |                   |      |       |          |          |       |

| 37<br>38 | AC_A(7)<br>AC_A(6) |         |       | X        |                   |      |       |          |          |       |

|          |                    |         |       |          |                   |      |       |          |          |       |

| 39<br>40 | AC_A(5)            |         |       | X        |                   |      |       |          | <u> </u> |       |

| 41       | AC_A(4)            |         |       |          |                   |      |       |          |          |       |

| 42       | AC_A(3)<br>AC_A(2) |         |       | X        |                   |      |       |          |          |       |

| 43       | AC_A(2)<br>AC_A(1) |         |       | X        |                   |      |       |          |          |       |

| 44       | AC_A(1) AC A(0)    |         |       | Y        |                   |      |       |          |          |       |

| 45       | AC_R(1)            |         |       | X        |                   |      |       |          |          |       |

| 46       | AC_R(1) AC R(0)    |         |       | X        |                   |      |       |          |          |       |

| 51       | DAS OUT            |         |       | ^        | X                 |      |       |          |          |       |

| 52       | DAS AI P           |         |       | X        |                   |      |       |          |          |       |

| 53       | DAS AI M           |         |       | X        |                   |      |       |          |          |       |

| 54       | DAS AO             |         |       | ^        | X                 |      |       |          |          |       |

| 55       | VBAT               |         |       |          | ^                 |      |       |          |          | X     |

|          | 7-71               |         |       |          | ı                 |      |       | <u> </u> |          | - *   |

| pin function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I/O | conf | igur  | ation   |                                         |           |                                         | 1                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-------|---------|-----------------------------------------|-----------|-----------------------------------------|-------------------------------------------|

| 58 VREG X X STREG X X STREG STREG X X STREG STRE | AI  | AO   | IQ    | OQ      | ОО                                      | PU        | POWER                                   |                                           |

| S8   VREG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |      |       |         |                                         |           | X                                       |                                           |

| 60 VMULT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |      |       |         |                                         |           | X                                       |                                           |

| 61 RESET 62 OSCOUT 63 OSCIN  Pin map table legend: blue bold: configuration at start up  Al: analog input AO: analog output DD: digital input DO: nMOS open drain output Pt): pull-up resistor POWER: power supply  Table 1-3. Pin description table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     | X    |       |         |                                         |           |                                         |                                           |

| Pin map table legend: blue bold: configuration at start up  Al: analog input AO: analog output DI: digital input OD: mMOS open drain output PU: pull-up resistor POWER: power supply  Table 1-3. Pin description table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     | X    |       |         |                                         |           |                                         |                                           |

| Pin map table legend: blue bold: configuration at start up  Al: analog input AO: analog output DI: digital input DO: digital output OD: nMOS open drain output PU: pull-up resistor POWER: power supply  Table 1-3. Pin description table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |      | Х     |         |                                         |           |                                         |                                           |

| Pin map table legend: blue bold: configuration at start up  Al: analog input AO: analog output DI: digital input DO: digital output OD: nMOS open drain output PU: pull-up resistor POWER: power supply  Table 1-3. Pin description table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | V   | X    |       |         |                                         |           |                                         |                                           |

| blue bold: configuration at start up  Al: analog input AO: analog output DI: digital input DO: digital output OD: nMOS open drain output PU: pull-up resistor POWER: power supply  Table 1-3. Pin description table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | X   |      |       |         |                                         |           |                                         | 60                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |      |       | 2       | Ç                                       | 2         |                                         | 5                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |      |       | 3       |                                         | C         | 8                                       |                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     | I    | A A X | V X X X | W N N N N N N N N N N N N N N N N N N N | X X X X X | A N N N N N N N N N N N N N N N N N N N | A DO DO X X X DO DO X X X X DO DO X X X X |

Table 1-3. Pin description table

#### 2 XE8805/05A Performance

| 2.1                          | Absolute maximum ratings                          | 2-2                |

|------------------------------|---------------------------------------------------|--------------------|

| 2.2                          | Operating range                                   | 2-2                |

| <b>2.3</b><br>2.3.1<br>2.3.2 | Supply configurations Flash circuit ROM circuit   | <b>2-3</b> 2-3 2-3 |

| 2.4                          | Current consumption                               | 2-5                |

| <b>2.5</b> 2.5.1 2.5.2       | Operating speed Flash version ROM circuit version | <b>2-6</b> 2-6 2-6 |

|                              |                                                   |                    |

#### 2.1 Absolute maximum ratings

Table 2-1. Absolute maximum ratings

|                                                 | Min.     | Max.     |    | Note |

|-------------------------------------------------|----------|----------|----|------|

| Voltage applied to VBAT with respect to VSS     | -0.3     | 6.0      | V  |      |

| Voltage applied to VPP with respect to VSS      | VBAT-0.3 | 12       | V  |      |

| Voltage applied to all pins except VPP and VBAT | VSS-0.3  | VBAT+0.3 | V  |      |

| Storage temperature (ROM device or unprogrammed | -55      | 150      | °C |      |

| flash device)                                   |          |          |    |      |

| Storage temperature (programmed flash device)   | -40      | 85       | °C |      |

Stresses beyond the absolute maximal ratings may cause permanent damage to the device. Functional operation at the absolute maximal ratings is not implied. Exposure to conditions beyond the absolute maximal ratings may affect the reliability of the device.

#### 2.2 Operating range

Table 2-2. Operating range for the flash device

|                                                    | Min. | Max. |    | Note |

|----------------------------------------------------|------|------|----|------|

| Voltage applied to VBAT with respect to VSS        | 2.4  | 5.5  | V  |      |

| Voltage applied to VBAT with respect to VSS during | 3.3  | 5.5  | V  | 1    |

| the flash programming                              |      |      |    |      |

| Voltage applied to VPP with respect to VSS         | VBAT | 11.5 | V  |      |

| Voltage applied to all pins except VPP and VBAT    | VSS  | VBAT | V  |      |

| Operating temperature range                        | -40  | 85   | °C |      |

| Capacitor on VREG (flash version)                  | 0.8  | 1.2  | μF | 2    |

| Capacitor on VMULT                                 | 1.0  | 3.0  | nF | 3    |

- 1. During the programming of the device, the supply voltage should at least be equal to the supply voltage used during normal operation.

- 2. The capacitor on VREG is mandatory.

- 3. The capacitor on VMULT is optional. The capacitor has to be present if the multiplier is enabled. The multiplier has to be enabled if VBAT<3.0V.

Table 2-3. Operating range for the ROM device

|                                                 | Min. | Max. |    | Note |

|-------------------------------------------------|------|------|----|------|

| Voltage applied to VBAT with respect to VSS     | 2.4  | 5.5  | V  |      |

| Voltage applied to all pins except VPP and VBAT | VSS  | VBAT | V  |      |

| Operating temperature range                     | -40  | 125  | °C |      |

| Capacitor on VREG                               | 0.1  | 1.2  | μF | 1    |

| Capacitor on VMULT                              | 1.0  | 3.0  | nF | 2    |

- 1. The capacitor may be omitted when VREG is connected to VBAT.

- 2. The capacitor on VMULT is optional. The capacitor has to be present if the multiplier is enabled. The multiplier has to be enabled if VBAT<3.0V.

All specifications in this document are valid for the complete operating range unless otherwise specified.

Table 2-4. Operating range of the Flash memory

|                              | Min. | Max. |       | Note |

|------------------------------|------|------|-------|------|

| Retention time at 85°C       | 10   |      | years | 1    |

| Retention time at 55°C       | 100  |      | years | 1    |

| Number of programming cycles | 10   |      |       | 2    |

- 1. Valid only if programmed using a programming tool that is qualified

- Circuits can be programmed more than 10 times but after that, the retention time is no longer guaranteed. All qualification tests have been done after 10 cycles.

#### 2.3 Supply configurations

#### 2.3.1 Flash circuit

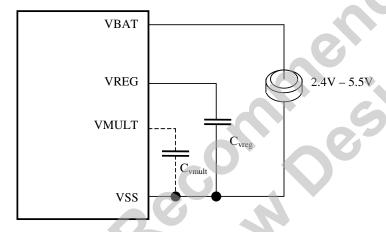

The flash version of the circuit can be run from a supply between 2.4V and 5.5V (Figure 2-1). The capacitor on VREG has to be connected at all times (value in Table 2-2) to guarantee proper operation of the device. The capacitor on VMULT is only required if the circuit is to be operated below 3V.

Figure 2-1. Supply configuration for the flash circuit.

#### 2.3.2 ROM circuit

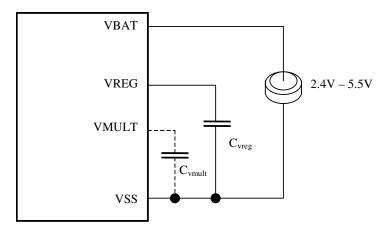

For the ROM version, two possible operating modes exist: with and without voltage regulator. Using the voltage regulator, low power consumption will be obtained even with supply voltages above 2.4V. Without the voltage regulator (i.e. VREG short-circuited to VBAT), a higher speed can be obtained.

#### 2.3.2.1 Low power operation

In this case, the internal voltage regulator is used in order to maintain low power consumption independent from the supply voltage. The capacitor on VREG has to be connected at all times (value in Table 2-3) to guarantee proper operation of the device. The capacitor on VMULT has to be connected only when VBAT<3V.

Figure 2-2. Supply voltage connections for low power operation of the ROM version.

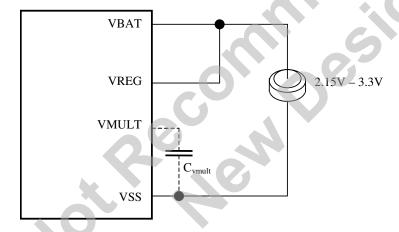

#### 2.3.2.2 High speed operation

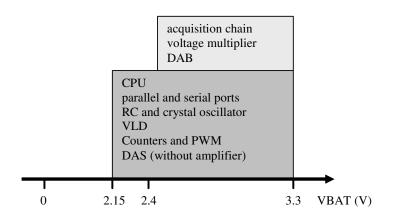

In this case, the internal voltage regulator is not used. The operation speed of the circuit can be increased with increasing supply voltage but the supply current will also increase. The capacitor on VMULT has to be connected only when VBAT<3V. In this case, the supply voltage can decrease down to 2.15V. Beware however that the zoomingADC<sup>TM</sup> will not run below 2.4V (see Figure 2-4). In this configuration, the circuit can not be used above 3.3V.

Figure 2-3. Supply voltage connections for high speed operation of the ROM version.

Figure 2-4. Operation range of the different circuit blocks

#### 2.4 Current consumption

The tables below give the current consumption for the circuit in different configurations. The figures are indicative only and may change as a function of the actual software implemented in the circuit.

Table 2-5 gives the current consumption for the flash version of the circuit. The peripherals are disabled. The parallel ports A and B are configured in input with pull up, the parallel port C is configured as an output. Their pins are not connected externally. The pin RESET is connected to VSS and the pin VPP/TEST is connected to VBAT. The inputs of the acquisition chain are connected to VSS.

| * *                |         | -       |        |             |                   |      |

|--------------------|---------|---------|--------|-------------|-------------------|------|

| Operation mode     | CPU     | RC      | Xtal   | Consumption | comments          | Note |

| High speed CPU     | 1 MIPS  | 1 MHz   | Off    | 310 μΑ      | 2.4V<>5.5V, 27°C  |      |

| Low power CPU      | 32 kIPS | Off     | 32 kHz | 10 μΑ       | 2.4V <>5.5V, 27°C |      |

| Low power time     | HALT    | Off     | 32 kHz | 1.0 μΑ      | 2.4V <>5.5V, 27°C |      |

| keeping            |         |         | `      |             |                   |      |

| Fast wake-up       | HALT    | Ready   | 32kHz  | 1.7 μΑ      | 2.4V <>5.5V, 27°C |      |

| time keeping       |         |         |        |             |                   |      |

| Immediate wake-    | HALT    | 100 kHz | Off    | 1.4 μΑ      | 2.4V <>5.5V, 27°C |      |

| up time keeping    |         |         |        |             |                   |      |

| VLD static current |         |         |        | 15 μΑ       | 2.4V <>5.5V, 27°C |      |

| 16 bit resolution  | HALT    | 2 MHz   | Off    | 190 μΑ      | 3.0V, 27°C        | 1    |

| data acquisition   |         | _       |        |             |                   |      |

| 12 bit , gain 100, | HALT    | 2 MHz   | Off    | 460 μΑ      | 3.0V, 27°C        | 2    |

| data acquisition   |         |         |        | •           |                   |      |

Table 2-5. Typical current consumption of the XE8805 version (8k instructions flash memory)

- 1. PGA disabled, ADC enabled, 16 bit resolution

- 2. PGA 1 disabled, PGA 2 and 3 enabled, ADC enabled, 12 bit resolution

For more information concerning the current consumption of the zoomingADC<sup>TM</sup>, see the chapter power consumption in the acquisition chain documentation which shows the current consumption of this block as a function of temperature and voltage and for different configurations of the PGA and ADC.

The power consumption of the ROM version of the circuit is identical if it is configured as shown in Figure 2-2. In the high speed configuration, the current consumption will increase proportional with VBAT.

#### 2.5 Operating speed

#### 2.5.1 Flash version

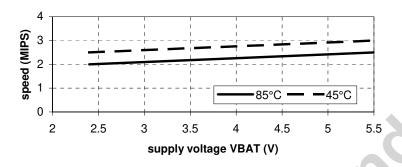

The speed of the devices is not highly dependent upon the supply voltage. However, by limiting the temperature range, the speed can be increased. The minimal guaranteed speed as a function of the supply voltage and maximal temperature operating temperature is given in Figure 2-5.

Figure 2-5. Guaranteed speed as a function of the supply voltage and maximal temperature.

#### 2.5.2 ROM circuit version

#### 2.5.2.1 Low power supply configuration

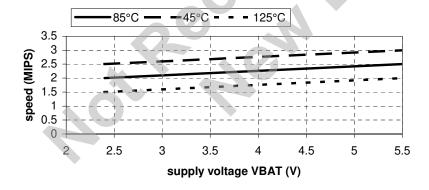

In the low power supply configuration as shown in Figure 2-2, the operating speed does not depend highly on the supply voltage as shown in Figure 2-6.

Figure 2-6. Guaranteed speed as a function of supply voltage and for different maximal temperatures using the voltage regulator.

#### 2.5.2.2 <u>High speed supply configuration</u>

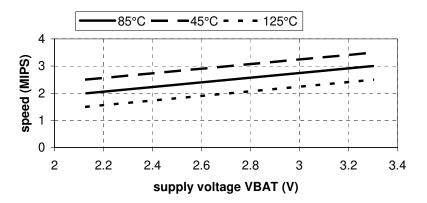

In the high speed supply configuration of Figure 2-3, the guaranteed speed of the circuit is shown in Figure 2-7.

Figure 2-7. Guaranteed speed as a function of supply voltage and for three temperature ranges when VREG=VBAT.

ot Reconstitutions of the second of the seco

#### 3. CPU

#### **CONTENTS**

| 3.1                                   | CPU description                 | 3-2 |

|---------------------------------------|---------------------------------|-----|

| 3.2                                   | CPU internal registers          | 3-2 |

| 3.3                                   | CPU instruction short reference | 3-4 |

|                                       |                                 |     |

|                                       |                                 |     |

|                                       |                                 |     |

|                                       |                                 |     |

|                                       |                                 |     |

|                                       | 60,00                           |     |

|                                       |                                 |     |

|                                       |                                 |     |

|                                       |                                 |     |

| • • • • • • • • • • • • • • • • • • • | 40                              |     |

|                                       |                                 |     |

|                                       |                                 |     |

#### 3.1 CPU description

The CPU of the XE8000 series is a low power RISC core. It has 16 internal registers for efficient implementation of the C compiler. Its instruction set is made up of 35 generic instructions, all coded on 22 bits, with 8 addressing modes. All instructions are executed in one clock cycle, including conditional jumps and 8x8 multiplication. The circuit therefore runs on 1 MIPS on a 1MHz clock.

The CPU hardware and software description is given in the document "Coolrisc816 Hardware and Software Reference Manual". A short summary is given in the following paragraphs.

The good code efficiency of the CPU core makes it possible to compute a polynomial like  $Z = (A_0 + A_1 \cdot Y) \cdot X + B_0 + B_1 \cdot Y$  in less than 300 clock cycles (software code generated by the XEMICS C-compiler, all numbers are signed integers on 16 bits).

#### 3.2 CPU internal registers

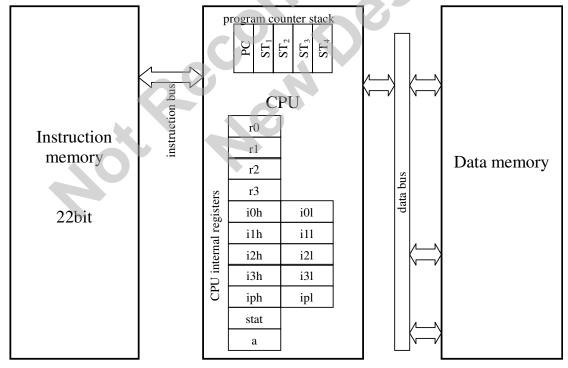

As shown in Figure 3-1, the CPU has 16 internal 8-bit registers. Some of these registers can be concatenated to a 16-bit word for use in some instructions. The function of these registers is defined in Table 3-1. The status register stat (Table 3-2) is used to manage the different interrupt and event levels. An interrupt or an event can both be used to wake up after a HALT instruction. The difference is that an interrupt jumps to a special interrupt function whereas an event continues the software execution with the instruction following the HALT instruction.

The program counter (PC) is a 16 bit register that indicates the address of the instruction that has to be executed. The stack  $(ST_n)$  is used to memorise the return address when executing subroutines or interrupt routines.

Figure 3-1. CPU internal registers

| Register name | Register function                  |

|---------------|------------------------------------|

| r0            | general purpose                    |

| r1            | general purpose                    |

| r2            | general purpose                    |

| r3            | data memory offset                 |

| i0h           | MSB of the data memory index i0    |

| iOl           | LBS of the data memory index i0    |

| i1h           | MSB of the data memory index i1    |

| i1l           | LBS of the data memory index i1    |

| i2h           | MSB of the data memory index i2    |

| i2l           | LBS of the data memory index i2    |

| i3h           | MSB of the data memory index i3    |

| i3l           | LBS of the data memory index i3    |

| iph           | MSB of the program memory index ip |

| ipl           | LBS of the program memory index ip |

| stat          | status register                    |

| а             | accumulator                        |

Table 3-1. CPU internal register definition

|                                     | i2h      | MSB of the data memory index i2                                                          |  |  |  |  |

|-------------------------------------|----------|------------------------------------------------------------------------------------------|--|--|--|--|

|                                     | i2l      | LBS of the data memory index i2                                                          |  |  |  |  |

| i3h MSB of the data memory index i3 |          | MSB of the data memory index i3                                                          |  |  |  |  |

|                                     | i3l      | LBS of the data memory index i3                                                          |  |  |  |  |

|                                     | iph      | MSB of the program memory index ip                                                       |  |  |  |  |

|                                     | ipl      | LBS of the program memory index ip                                                       |  |  |  |  |

|                                     | stat     | status register                                                                          |  |  |  |  |

|                                     | а        | accumulator                                                                              |  |  |  |  |

| Table                               | e 3-1 CF | PU internal register definition                                                          |  |  |  |  |

| Table                               | 0 1. 01  | o internal register definition                                                           |  |  |  |  |

|                                     |          |                                                                                          |  |  |  |  |

| bit                                 | name     | function                                                                                 |  |  |  |  |

| 7                                   | IE2      | enables (when 1) the interrupt request of level 2                                        |  |  |  |  |

| 6                                   | IE1      | enables (when 1) the interrupt request of level 1                                        |  |  |  |  |

| 5                                   | GIE      | enables (when 1) all interrupt request levels                                            |  |  |  |  |

| 4                                   | IN2      | interrupt request of level 2. The interrupts labelled "low" in the interrupt handler are |  |  |  |  |

|                                     |          | routed to this interrupt level. This bit has to be cleared when the interrupt is served. |  |  |  |  |

| 3                                   | IN1      | interrupt request of level 1. The interrupts labelled "mid" in the interrupt handler are |  |  |  |  |

|                                     |          | routed to this interrupt level. This bit has to be cleared when the interrupt is served. |  |  |  |  |

| 2                                   | IN0      | interrupt request of level 0. The interrupts labelled "hig" in the interrupt handler are |  |  |  |  |

|                                     |          | routed to this interrupt level. This bit has to be cleared when the interrupt is served. |  |  |  |  |

| 1                                   | EV1      | event request of level 1. The events labelled "low" in the event handler are routed to   |  |  |  |  |

|                                     |          | his event level. This bit has to be cleared when the event is served.                    |  |  |  |  |

| 0                                   | EV0      | event request of level 1. The events labelled "hig" in the event handler are routed to   |  |  |  |  |

|                                     |          | this event level. This bit has to be cleared when the event is served.                   |  |  |  |  |

Table 3-2. Status register description

The CPU also has a number of flags that can be used for conditional jumps. These flags are defined in Table 3-3.

| symbol | name     | function                                                                               |  |  |  |

|--------|----------|----------------------------------------------------------------------------------------|--|--|--|

| Z      | zero     | Z=1 when the accumulator a content is zero                                             |  |  |  |

| С      | carry    | This flag is used in shift or arithmetic operations.                                   |  |  |  |

|        |          | For a shift operation, it has the value of the bit that was shifted out (LSB for shift |  |  |  |

|        |          | right, MSB for shift left).                                                            |  |  |  |

|        |          | For an arithmetic operation with unsigned numbers:                                     |  |  |  |

|        |          | it is 1 at occurrence of an overflow during an addition (or equivalent).               |  |  |  |

|        |          | it is 0 at occurrence of an underflow during a subtraction (or equivalent).            |  |  |  |

| V      | overflow | This flag is used in shift or arithmetic operations.                                   |  |  |  |

|        |          | For arithmetic or shift operations with signed numbers, it is 1 if an overflow or      |  |  |  |

|        |          | underflow occurs.                                                                      |  |  |  |

Table 3-3. Flag description

#### 3.3 CPU instruction short reference

Table 3-4 shows a short description of the different instructions available on the Coolrisc816. The notation cc in the conditional jump instruction refers to the condition description as given in Table 3-6. The notation reg, reg1, reg2, reg3 refers to one of the CPU internal registers of Table 3-1. The notation eaddr and DM(eaddr) refer to one of the extended address modes as defined in Table 3-5. The notation DM(xxx) refers to the data memory location with address xxx.

| Jump addr[15:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Instruction         | Modification | Operation                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------|--------------------------------------------------------------------------|

| Jump   D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Jump addr[15:0]     |              | PC := addr[15:0]                                                         |

| Joe addr(15:0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                     |              |                                                                          |