Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# XR68C681

CMOS Dual Channel UART (DUART)

September 1999-2

## **FEATURES**

- Two Full Duplex, Independent Channels

- Asynchronous Receiver and Transmitter

- Quadruple-Buffered Receiver, Dual Buffered Transmitter

- Programmable Stop Bits in 1/16 Bit Increments

- Internal Bit Rate Generators with 23 Different Bit Rates

- Independent Bit Rate Selection for Each Transmitter and Receiver

- External Clock Capability

- Maximum Bit Rate: 1X Clock 1Mb/s, 16X Clock - 125Kb/s

- Normal, AUTOECHO, Local LOOPBACK and Remote LOOPBACK Modes

- Multi-function 16 Bit Counter/Timer

- Interrupt Output with Eight Maskable Interrupt Conditions

- Interrupt Vector Output on Acknowledge

- 8 General Purpose Outputs

- 6 General Purpose Inputs with Change of States Detectors on Inputs

- On-chip Oscillator for Crystal

- Standby Mode to Reduce Operating Power

- Compatible with the Motorola MC68681 and the Signetic SCC68692 Devices

- Advanced CMOS Low Power Technology

## **APPLICATIONS**

- Multimedia Systems

- Serial to Parallel/Parallel to Serial Converter

- DTE for Modem Communication Systems

## **GENERAL DESCRIPTION**

The EXAR Dual Universal Asynchronous Receiver and Transmitter (DUART) is a data communications device that provides two fully independent full duplex asynchronous communications channels in a single package. The DUART is designed for use in microprocessor based systems and may be used in a polled or interrupt driven environment.

The XR68C681 device offers a single IC solution for the 68000 family of microprocessors

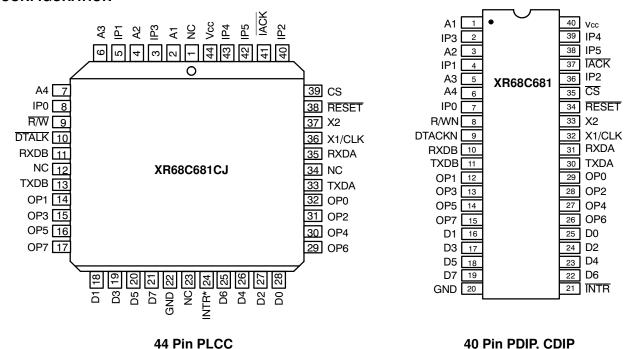

The DUART is fabricated using advanced two layer metal, with a high performance density EPI/CMOS 1.8 process to provide high performance and low power consumption, and is packaged in a 40 pin DIP or a 44 pin PLCC.

## **ORDERING INFORMATION**

| Part No.   | Pin<br>Package | Operating<br>Temperature<br>Range |

|------------|----------------|-----------------------------------|

| XR68C681CJ | 44 PLCC        | 0°C to +70°C                      |

| XR68C681J  | 44 PLCC        | -40°C to +85°C                    |

| Part No.   | Pin<br>Package | Operating<br>Temperature<br>Range |

|------------|----------------|-----------------------------------|

| XR68C681N  | 40 CDIP        | -40°C to +85°C                    |

| XR68C681CP | 40 PDIP        | 0°C to +70°C                      |

| XR68C681P  | 40 PDIP        | -40°C to +85°C                    |

Overbar indicates Non-compliant MIL-STD-883 Product.

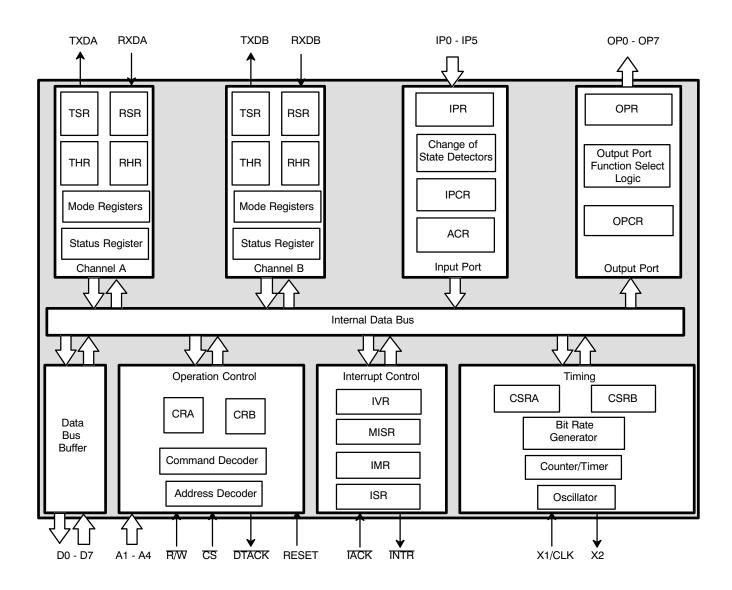

Figure 1. Block Diagram of the XR68C681 DUART Device

(0.600")

# **PIN CONFIGURATION**

## **PIN DESCRIPTION**

| Pin Number<br>(44 pin PLCC) | Pin Number<br>(40 pin DIP) | Symbol                     | Туре | Description                                                                                                                                                                             |

|-----------------------------|----------------------------|----------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                           |                            | NC                         |      | No Connect.                                                                                                                                                                             |

| 2                           | 1                          | A1                         | I    | <b>LSB of Address Input.</b> This input, along with address inputs, A2 - A4 are used to select certain registers within the DUART device during read and write operations with the CPU. |

| 3                           | 2                          | IP3<br>(TXCA)              | I    | Input Port 3. General purpose input or the external clock input for Channel A Transmitter (TXCA)                                                                                        |

| 4                           | 3                          | A2                         | I    | Address Input.                                                                                                                                                                          |

| 5                           | 4                          | IP1<br>( <del>CTSB</del> ) | I    | Input Port 1. General purpose input. This input can be configured to be the Active-low Channel B Clear-to-Send Input (CTSB).                                                            |

| 6                           | 5                          | АЗ                         | l    | Address Input.                                                                                                                                                                          |

| 7                           | 6                          | A4                         | I    | MSB of Address Input. This input, along with Address Inputs, A1 - A3 are used to select certain registers within the DUART device.                                                      |

| Pin Number<br>(44 pin PLCC) | Pin Number<br>(40 pin DIP) | Symbol                             | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------------------|----------------------------|------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8                           | 7                          | IP0<br>(CTSA)                      | I    | Input Port 0. General purpose input. This input can also be configured to be the Active-low channel A Clear-to-Send Input (CTSA).                                                                                                                                                                                                                                                             |

| 9                           | 8                          | R/W                                | I    | Read/Write Input. If this input is high while $\overline{CS}$ is low, then the CPU is performing a READ cycle with the DUART. If this input is low, while $\overline{CS}$ is low, then the CPU is performing a WRITE cycle with the DUART.                                                                                                                                                    |

| 10                          | 9                          | DTACK                              | 0    | Data Transfer Acknowledge. Three State, active low: The DUART asserts DTACK in order to inform the CPU that the present READ or WRITE operation is nearly complete. The 68000 family of CPUs requires this signal from its peripheral devices, in order to quickly and properly complete a READ or WRITE cycle.                                                                               |

|                             |                            |                                    |      | If the DUART asserts DTACK during a READ operation, it indicates (to the CPU) that the requested data is on the data bus. If DTACK is asserted during an Interrupt Acknowledge cycle, the DUART is informing the CPU that the contents of the IVR (Interrupt Vector Register) are available on the data bus.                                                                                  |

|                             |                            |                                    |      | If the DUART asserts the DTACK during a WRITE cycle, it is informing the CPU that the data, on the data bus, has been latched into the data bus buffer of the DUART device.                                                                                                                                                                                                                   |

| 11                          | 10                         | RXDB                               | I    | Receiver Serial Data Input- Channel B. The least significant bit of the character is received first. If an external receiver clock is specified, the received data is sampled on the rising edge of this clock.                                                                                                                                                                               |

| 12                          |                            | NC                                 |      | No Connect.                                                                                                                                                                                                                                                                                                                                                                                   |

| 13                          | 11                         | TXDB                               | 0    | Transmitter Serial Data Output - Channel B. The least significant bit of the channel is transmitted first. This output is held in the marking (high) state when the transmitter is idle, disabled, or operating in the local LOOPBACK mode. If an external clock is specified, the transmitted data is shifted out of the TSR (Transmitter Shift Register) on the falling edge of this clock. |

| 14                          | 12                         | OP1<br>( <del>RTSB</del> )         | 0    | Output 1. A general purpose output. This output can also be configured as the active-low channel B Request-to-Send output (RTSB).                                                                                                                                                                                                                                                             |

| 15                          | 13                         | OP3<br>(TXCB)<br>(RXCB)<br>C/T_RDY | 0    | Output 3. A general purpose output. This output pin can also be configured to be the channel B Transmitter 1X Clock output (TXCB), the channel B Receiver 1X Clock output (RXCB), or as an active-low, open-drain Counter/Timer Ready Output (C/T_RDY).                                                                                                                                       |

| 16                          | 14                         | OP5<br>(RXRDY/<br>FFULL_B)         | 0    | Output 5. A general purpose output. This output pin can also be configured to be the open-drain, active-low channel B RXRDY/FFULL output, active-low.                                                                                                                                                                                                                                         |

| Pin Number<br>(44 pin PLCC) | Pin Number<br>(40 pin DIP) | Symbol                         | Туре | Description                                                                                                                                                                                                                                                                                                           |

|-----------------------------|----------------------------|--------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17                          | 15                         | OP7<br>(TXRDY_A)               | 0    | Output 7. A general purpose output. This output pin can also be configured to be the open-drain active low channel A TXRDY output.                                                                                                                                                                                    |

| 18                          | 16                         | D1                             | I/O  | Three State Data Bus.                                                                                                                                                                                                                                                                                                 |

| 19                          | 17                         | D3                             | I/O  | Three State Data Bus.                                                                                                                                                                                                                                                                                                 |

| 20                          | 18                         | D5                             | I/O  | Three State Data Bus.                                                                                                                                                                                                                                                                                                 |

| 21                          | 19                         | D7                             | I/O  | MSB of Eight Bit Three State Data Bus. All transfers between the CPU and DUART take place over the data bus (consists of pins D0 - D7). The bus is three-stated when the CS input is high, except during an IACK cycle.                                                                                               |

| 22                          | 20                         | GND                            |      | Ground. Reference                                                                                                                                                                                                                                                                                                     |

| 23                          |                            | NC                             |      | No Connect.                                                                                                                                                                                                                                                                                                           |

| 24                          | 21                         | INTR                           | 0    | Interrupt Request. Active Low, Open-Drain. INTR is asserted upon the occurrence of one or more of the chip's maskable interrupting conditions. This signal will remain asserted throughout the interrupt service routine and will be negated once the condition(s) causing the interrupt request has been eliminated. |

| 25                          | 22                         | D6                             | I/O  | Three State Data Bus.                                                                                                                                                                                                                                                                                                 |

| 26                          | 23                         | D4                             | I/O  | Three State Data Bus.                                                                                                                                                                                                                                                                                                 |

| 27                          | 24                         | D2                             | I/O  | Three State Data Bus.                                                                                                                                                                                                                                                                                                 |

| 28                          | 25                         | D0                             | I/O  | LSB of the Eight Bit Three State Data Bus. All transfers between the CPU and QUART take place over this bus. The bus is three-stated when the CS input is high, except during an IACK cycle.                                                                                                                          |

| 29                          | 26                         | OP6<br>(TXRDY_A)               | 0    | Output 6. A general purpose output. This output pin can also be configured to be an active-low, open-drain channel A TXRDY output (TXRDY_A)                                                                                                                                                                           |

| 30                          | 27                         | OP4<br>(RXRDY/<br>FFULL_A)     | 0    | <b>Output 4.</b> A general purpose output. This output pin can also be configured to be an open-drain channel A RXRDY/FFULL output (active-low).                                                                                                                                                                      |

| 31                          | 28                         | OP2<br>(TXCA_1X)<br>(TXCA_16X) | 0    | Output 2. A general purpose output. This output pin can also be configured to be either 1X or 16X clock output for the channel A transmitter.                                                                                                                                                                         |

| 32                          | 29                         | OP0<br>(RTSA)                  | 0    | <b>Output 0.</b> A general purpose output. This output pin can also be configured to be the active-low Channel A Request-to-Send Output (RTSA).                                                                                                                                                                       |

| Pin Number<br>(44 pin PLCC) | Pin Number<br>(40 pin DIP) | Symbol                    | Туре   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------------|----------------------------|---------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 33                          | 30                         | TXDA                      | 0      | Transmitter Serial Data Output. Channel A. The least significant bit is transmitted first. This output is held in the marking (high) state when the transmitter is idle, disabled, or operating in the local LOOPBACK mode. If external clock is specified, the transmitted data is shifted out of the TSR (Transmitter Shift Register) on the falling edge of the clock.                                                                                                                            |

| 34                          |                            | NC                        |        | No Connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 35                          | 31                         | RXDA                      | I      | Receiver Serial Data Input. Channel A. The least significant bit is received first. If an external receiver clock is specified, the received data is sampled on the rising edge of the clock.                                                                                                                                                                                                                                                                                                        |

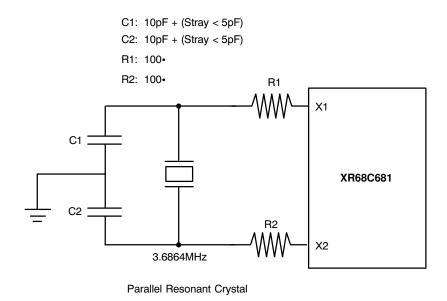

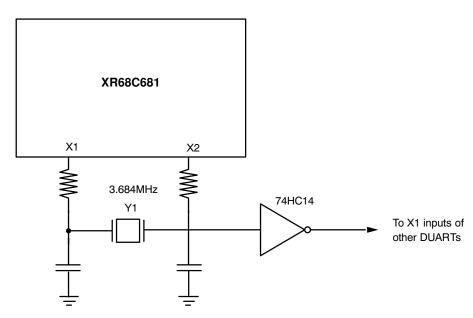

| 36                          | 32                         | X1/CLK                    | I or O | Crystal Output or External Clock Input. This pin is the connection for one side of the crystal and a capacitor to ground when the internal oscillator is used. If the oscillator is not used, an external clock signal must be supplied at this input. In order for the XR68C681 device to function properly, the user must supply a signal with frequencies between 2.0 MHz and 4.0 MHz. This requirement can be met by either a crystal oscillator or by the external TTL-compatible clock signal. |

| 37                          | 33                         | X2                        | I      | <b>Crystal Input.</b> Connection for one side of the crystal (Opposite of X1/CLK). If the oscillator is used, a capacitor must also be connected from this pin to ground. This pin must be left open if an external clock is supplied at X1/CLK.                                                                                                                                                                                                                                                     |

| 38                          | 34                         | RESET                     | I      | <b>Master Reset.</b> A low on this pin clears internal registers (SRA, SRB, IMR, ISR, OPR, OPCR), initializes the IVR to 0F <sub>16</sub> , stops the Counter/Timer, places the output port pins, OP0 - OP7 in the logic "high" state, and places both serial channels in the inactive state with the TXDA and TXDB output marking (high).                                                                                                                                                           |

| 39                          | 35                         | cs                        | I      | Chip Select. Active low. The data bus is three-stated when $\overline{CS}$ is high. Transfers between the CPU and the DUART via D0 - D7 are enabled when $\overline{CS}$ is low.                                                                                                                                                                                                                                                                                                                     |

| 40                          | 36                         | IP2<br>(C/T_EX)<br>(RXCB) | I      | Input 2. General purpose input. This input can also be configured to be C/T external clock input, or the channel B Receiver Clock Input (RXCB).                                                                                                                                                                                                                                                                                                                                                      |

| 41                          | 37                         | IACK                      | ı      | Interrupt Acknowledge. Active Low. This input is the CPU's response to the interrupt request issued by the DUART device. When the CPU asserts this input, it indicates that the DUART's interrupt request is about to be serviced, and that the very next bus cycle will be an interrupt acknowledge cycle. The DUART will respond to the CPU's interrupt acknowledge by placing the contents of the Interrupt Vector Register (IVR) on the data bus (D0 - D7).                                      |

| Pin Number<br>14 pin PLCC) | Pin Number<br>(40 pin DIP) | Symbol        | Туре | Description                                                                                                                        |

|----------------------------|----------------------------|---------------|------|------------------------------------------------------------------------------------------------------------------------------------|

| 42                         | 38                         | IP5<br>(TXCB) | I    | <b>Input 5.</b> General purpose input. This input can also be configured as the channel B transmitter external clock input (TXCB). |

| 43                         | 39                         | IP4<br>(RXCA) | l    | Input 4. General purpose input. This input can also be configured as the channel A Receiver External Clock Input (RXCA).           |

| 44                         | 40                         | Vcc           |      |                                                                                                                                    |

# DC ELECTRICAL CHARACTERISTICS 1, 2, 3

Test Conditions: TA = 0 -  $70^{\circ}$ C, Vcc =  $5V \pm 5\%$  unless otherwise specified.

| Symbol | Parameter                          | Min | Тур | Max | Unit | Conditions               |

|--------|------------------------------------|-----|-----|-----|------|--------------------------|

| VIL    | Input Low Voltage                  | 0.5 |     | 0.8 | V    |                          |

| VIH    | Input High Voltage                 | 2.0 |     | Vcc | V    |                          |

| VIH    | Input High Voltage (Military)      | 2.2 |     |     | V    | TA = -55°C to 125°C      |

| VIHX1  | Input High Voltage (X1/CLK)        | 4.0 |     | Vcc | V    |                          |

| Vol    | Output Low Voltage                 |     |     | 0.4 | V    | I <sub>OL</sub> = 2.4 mA |

| Vон    | Output High Voltage                | 2.4 |     |     | V    | I <sub>OH</sub> = -400μA |

| lı∟    | Input Leakage Current              | -25 |     | 25  | μΑ   | VIN = 0 to VCC           |

| IILSEL | Select Pin Leakage Current         | -30 |     | +30 | μΑ   | VIN = 0 to VCC           |

| IX1L   | X1 Input Low Current               |     | -20 |     | μΑ   | VIN = 0                  |

| IX2L   | X2 Input Low Current               |     | -7  |     | mA   |                          |

| Iхін   | X1 Input High Current              |     | 20  |     | μΑ   | VIN = VCC                |

| Ix2H   | X2 Input High Current              |     | 20  |     | μΑ   | VIN = VCC                |

| ILL    | Data bus Tri-State Leakage Current | -10 |     | 10  | μΑ   | VO = 0 to Vcc            |

| loc    | Open Drain Output Leakage Current  | -10 |     | 10  | μΑ   | VO = 0 to Vcc            |

| ICCA   | Power Supply Current <sup>4</sup>  |     | 6   | 15  | mA   | Active Mode              |

| Iccs   | Power Supply Current <sup>4</sup>  |     | 3   | 10  | mA   | Standby Mode             |

#### Notes

<sup>&</sup>lt;sup>1.</sup> Parameters are valid over the specified temperature and operating supply ranges. Typical values are 25°C, V<sub>CC</sub> = 5V and typical processing parameters.

<sup>&</sup>lt;sup>2</sup> All voltages are referenced to ground (GND). For testing, input signal levels are 0.4V and 2.4V with a transition time of 20ns maximum. All time measurements are referenced at input voltages of 0.8V and 2.0V as appropriate. See Figure 31.

<sup>&</sup>lt;sup>3.</sup> For prime grade N, P, J, L, M, ML,  $V_{CC}$  =  $5V \pm 10\%$

<sup>&</sup>lt;sup>4</sup> Measured operating with a 3.6864MHz crystal and with all outputs open.

# AC ELECTRICAL CHARACTERISTICS 1, 2, 3

Test Conditions: TA = 0 - 70°C, Vcc = 5.0V  $\pm$ 5% unless otherwise specified.

| Symbol                                                                   | Symbol Parameter                                    |     |       | Max        | Unit     | Conditions |  |

|--------------------------------------------------------------------------|-----------------------------------------------------|-----|-------|------------|----------|------------|--|

| Rest Timing (See Figure 32)                                              |                                                     |     |       |            |          |            |  |

| tres                                                                     | RESET Pulse Width                                   | 1.0 |       |            | μS       |            |  |

| Read, Write and Interrupt Cycle Timing (Figure 33, Figure 34, Figure 35) |                                                     |     |       |            |          |            |  |

| tas                                                                      | A1-A4 Setup Time to CS Low                          | 10  |       |            | ns       |            |  |

| tah                                                                      | A1-A4 Hold Time from CS High                        | 0   |       |            | ns       |            |  |

| trws                                                                     | R/W Setup Time to CS Low                            | 0   |       |            | ns       |            |  |

| trwh                                                                     | R/W Setup Time from CS High                         | 0   |       |            | ns       |            |  |

| tcsw                                                                     | CS High Pulse Width 4, 5                            | 90  |       |            | ns       |            |  |

| tcsd                                                                     | CS or IACK High from DTACK Low                      | 20  |       |            | ns       |            |  |

| too                                                                      | Data Valid from CS or IACK Low <sup>6</sup>         |     |       | 175        | ns       |            |  |

| tDF                                                                      | Data Bus Floating from CS or IACK<br>High           | 10  |       | 100        | ns       |            |  |

| tos                                                                      | Data Setup Time to CS Low                           | 0   |       |            | ns       |            |  |

| tDH                                                                      | Data Hold Time from CS Low                          | 125 |       |            | ns       |            |  |

| tDAL                                                                     | DTACK Low from Read Data Valid                      | 0   |       |            | ns       |            |  |

| tdah                                                                     | DTACK High from CS or IACK High                     |     |       | 100        | ns       |            |  |

| tdat                                                                     | DTACK High Impedance from CS or IACK High           |     |       | 125        | ns       |            |  |

| tcsc                                                                     | CS or IACK set up time to "High"7                   | 80  |       |            | ns       |            |  |

| Port Timing                                                              | ( <i>Figure 36</i> )                                |     |       |            |          |            |  |

| tps                                                                      | Port Input Setup Time to CS Low or R/W High         | 0   |       |            | ns       |            |  |

| tрн                                                                      | Port Input Hold Time from CS High                   | 0   |       |            | ns       |            |  |

| tPD                                                                      | Port Output Valid from R/W, CS High                 |     |       | 400        | ns       |            |  |

| Interrupt O                                                              | utput Timing (Figure 37)                            |     |       |            |          |            |  |

| tır                                                                      | INTR or OP3-OP7 when used as Interrupts High from:  |     |       | 300<br>300 | ns<br>ns |            |  |

|                                                                          | Clear of Interrupts Status Bits in ISR or IPCR      |     |       |            |          |            |  |

|                                                                          | Clear of Interrupt Mask in IMR                      |     |       |            |          |            |  |

| Clock Timir                                                              | ng ( <i>Figure 38</i> )                             |     |       |            |          |            |  |

| tclk                                                                     | X1/CLK (External) High or Low Time                  | 100 |       |            | ns       |            |  |

| tclk                                                                     | X1/CLK Crystal or External Frequency                | 2.0 | 3.684 | 7.372      | MHz      |            |  |

| tctc                                                                     | Counter/Timer External Clock High or Low Time (IP2) | 100 |       |            | ns       |            |  |

| tctc                                                                     | Counter/Timer External Clock Frequency              | 0   |       | 7.372      | MHz      |            |  |

|                                                                          |                                                     |     |       |            | _        |            |  |

# AC ELECTRICAL CHARACTERISTICS 1, 2, 3 (CONT'D)

Test Conditions:  $TA = 0 - 70^{\circ}C$ , VCC = 5.0V + 5% unless otherwise specified.

| Symbol     | Parameter                                              | Min | Тур | Max  | Unit | Conditions |

|------------|--------------------------------------------------------|-----|-----|------|------|------------|

| Clock Timi | ng ( <i>Figure 38</i> )                                |     | •   | •    | •    |            |

| trtx       | RXCn and TXCn (External) High or Low Time <sup>8</sup> | 220 |     |      | ns   |            |

| frtx       | RXCn and TXCn (External) Frequency                     |     |     |      |      |            |

|            | 16X                                                    | 0   |     | 16.0 | MHz  |            |

|            | 1X                                                     | 0   | ĺ   | 1.0  | MHz  |            |

| Transmitte | r Timing ( <i>Figure 39</i> )                          |     |     |      |      |            |

| tTXD       | TXD Output Delay - TXC (External)<br>Low               |     |     | 350  | ns   |            |

| trcs       | TXD Output Delay - TXC (Internal) Output Low           |     |     | 150  | ns   |            |

| Receiver T | iming ( <i>Figure 40</i> )                             |     | 1   | •    | •    |            |

| trxs       | RXD Data Setup Time to RXC (External) High             | 240 |     |      | ns   |            |

| trxh       | RXD Data Hold Time from RXC (External) High            | 200 |     |      | ns   |            |

#### Notes

### Specifications are subject to change without notice

# **ABSOLUTE MAXIMUM RATINGS<sup>1</sup>**

<sup>2.</sup> This product includes circuitry specifically designed for the protection of its internal devices from damaging effects of excessive static charge. Nonetheless, it is suggested that conventional precautions be taken to avoid applying any voltage larger than the rated maximum.

<sup>&</sup>lt;sup>1</sup> Parameters are valid over the specified temperature and operating supply ranges. Typical values are 25°C, V<sub>CC</sub> = 5V and typical processing parameters.

<sup>&</sup>lt;sup>2.</sup> All voltages are referenced to ground (GND). For testing, input signal levels are 0.4V and 2.4V with a transition time of 20ns maximum. All time measurements are referenced at input voltages of 0.8V and 2.0V as appropriate. See Figure 31.

<sup>&</sup>lt;sup>3.</sup> AC test conditions for outputs: CL = 50pF,  $RL = 2.7k \cdot to V_{CC}$ .

<sup>4.</sup> Consecutive write operations to the same register require at least three edges of the X1 clock between writes.

<sup>&</sup>lt;sup>5.</sup> This specification imposes a 6 MHz maximum 68000 clock frequency if a read or write cycle follows immediately after the previous read or write cycle. A higher 68000 clock can be used if this is not the case.

<sup>6.</sup> This specification imposes a lower bound on CS and TACK low, guaranteeing that they will be low for at least one CLK period.

<sup>&</sup>lt;sup>7.</sup> This parameter is specified only to insure DTACK is asserted with respect to the rising edge of X1/CLK as shown in the timing diagram, not to guarantee operation of the part. If the specified setup time is violated, DTACK may be asserted as shown or may be asserted one clock cycle later.

<sup>8.</sup> The minimum high time must be at least 1.5 times the X1/CLK period and the minimum low time must be at least equal to the X1/CLK period if either channel's Receiver is operating in external 1X clock mode.

<sup>1.</sup> Stresses above those listed under the Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions above those indicated in the "Electrical Characteristics" section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### SYSTEM DESCRIPTION

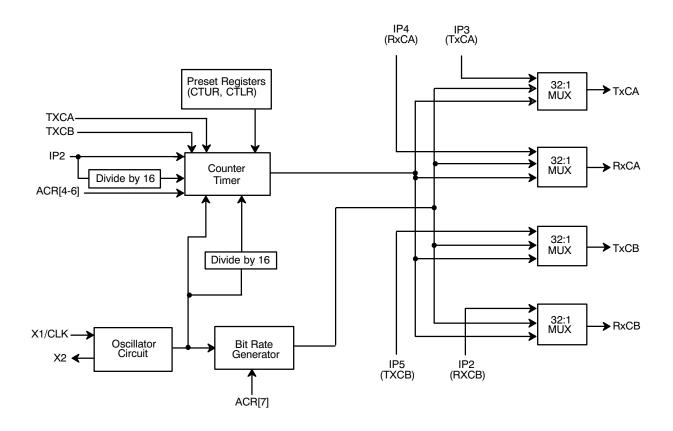

The XR68C681 consists of two independent, full-duplex communication channels; each consisting of their own Transmitter and Receiver. Each channel of the DUART may be independently programmed for operating mode and data format. The DUART is designed to interface with the 68000 Family of microprocessors with minimal external components. The operating speed of each receiver and transmitter may be selected from one of 23 internally generated fixed bit rates, from a clock derived from an internal Counter/Timer, or from an externally supplied 1x or 16x clock. The bit rate generator (the source of the 23 different fixed bit rates) can operate directly from a crystal connected across two pins or from an external clock. The ability to independently program the operating speed of the receiver and transmitter of each channel makes the DUART attractive for split speed channel applications such as clustered terminal systems.

Receiver data is quadrupled-buffered and the Transmitter data is dual-buffered via on-chip FIFOs in order to minimize the risk of receiver overrun and to reduce overhead in interrupt driven applications. The DUART also provides a flow control capability to inhibit transmission from a remote device when the buffer of the receiving DUART is full, thus preventing loss of data.

The DUART also provides a general purpose 16 bit Counter/Timer (which may also be used as programmable bit rate generators), a multi-purpose 6 bit input port and a multi-purpose 8 bit output ports.

#### PRINCIPLES OF OPERATION

Figure 1 presents an overall block diagram of the 68C681 DUART. As illustrated in the block diagram, the DUART consists of the following major functional blocks:

- Data Bus Buffer

- Interrupt Control

- Input Port

- Serial Communications Channels A and B

- Operation Control

- Timing

- Output Port

## A. DATA BUS BUFFER

The data bus buffer provides the interface between the internal (within the chip) and external data buses. It is controlled by the operation control block to allow data transfers to take place between the host CPU and the DUART.

## **B. OPERATION CONTROL BLOCK**

The control logic of the operation control block receives operating commands from the CPU and generates proper signals to the various sections of the DUART. The operation control block functions as the user interface to the rest of the device. Specifically, it is responsible for DUART register address decoding, and command decoding. Therefore all commands to set baud rates, parity, other communication protocol parameters, start or stop the Counter/Timer or reading a "status register" to monitor data communication performance are processed via the operation control block.

The operation control block will control DUART performance based upon the following input signals:

- Address (Register Select) bits: A1 A4

- R/W Input

- CS Input

- RESET

The DUART includes a Data Transfer Acknowledge (DTACK) output which is asserted during data transfer cycles in order to inform the CPU that the requested operation has been completed. An asserted DTACK signal indicates, to the CPU, that the input data has been latched, by the DUART data bus buffer, during a write cycle; that the requested data (from the DUART) is on the data bus and is valid during a read cycle, or that the interrupt vector is on the data bus during an interrupt acknowledge cycle.

When using the 6800 family processor, the XR-88C681 DUART data bus buffer should be used in lieu of this device. For information on how to interface a 6800 Family Processor to the XR-88C681 device, please see the XR-88C681 data sheet.

# **B.1 DUART REGISTER ADDRESSING**

The addressing of the internal registers of the DUART is presented in *Table 1*. Please note that some of the registers are "Read Only" and others are "Write Only". Each channel is provided with the following dedicated (addressable) registers.

- Command Register

- Mode Registers (MR1 and MR2)

- Status Register

- Clock Select Register

- Receiver Holding Register (RHR) and Transmit Holding Register (THR)

Additionally, the DUART contains the following registers that support/control both channel pairs.

- Interrupt Status Register (ISR)

- Interrupt Mask Register (IMR)

- Masked Interrupt Status Register (MISR)

- Interrupt Vector Register (IVR)

- Auxiliary Control Register (ACR)

Finally, the DUART contains additional registers that support functions other than serial data communication, such as the parallel ports and the counters/timers.

- Output Port Control Register (OPCR)

- Input Port Configuration Register (IPCR)

- Counter/Timer Upper Byte Register (CTUR)

- Counter/Timer Lower Byte Register (CTLR)

- Output Port Register (OPR)

|                  | Read Mode Registers                  |            | Write Mode                                        | Registers  |

|------------------|--------------------------------------|------------|---------------------------------------------------|------------|

| Address<br>(HEX) | Register Name                        | Symbol     | Register Name                                     | Symbol     |

| 00               | Mode Register, channel A             | MR1A, MR2A | Mode Register,<br>channel A                       | MR1A, MR2A |

| 01               | Status Register, channel<br>A        | SRA        | Clock Select Register,<br>channel A               | CSRA       |

| 02               | Masked Interrupt Status<br>Register  | MISR       | Command Register,<br>channel A                    | CRA        |

| 03               | Rx Holding Register,<br>channel A    | RHRA       | Tx Holding Register,<br>channel A                 | THRA       |

| 04               | Input Port Change<br>Register        | IPCR       | Auxiliary Control Register                        | ACR        |

| 05               | Interrupt Status Register            | ISR        | Interrupt Mask Register                           | IMR        |

| 06               | Counter/Timer Upper<br>Byte Register | СТИ        | Counter/Timer Upper<br>Byte Register              | СТИ        |

| 07               | Counter/Timer Lower<br>Byte Register | CTL        | Counter/Timer Lower<br>Byte Register              | CTL        |

| 08               | Mode Register, channel B             | MR1B, MR2B | Mode Register, channel B                          | MR1B, MR2B |

| 09               | Status Register, channel<br>B        | SRB        | Clock Select Register,<br>channel B               | CSRB       |

| 0A               | RESERVED                             |            | Command Register,<br>channel B                    | CRB        |

| 0B               | Rx Holding Register,<br>channel B    | RHRB       | Tx Holding Register,<br>channel B                 | THRB       |

| 0C               | Interrupt Vector Register            | IVR        | Interrupt Vector Register                         | IVR        |

| 0D               | Input Port                           | IP         | Output Port Configuration<br>Register (OP0 - OP7) | OPCR       |

| 0E               | Start Counter/Timer<br>Command       | SCC        | Set Output Port Bits<br>Command                   | SOPBC      |

| 0F               | Stop Counter/Timer<br>Command        | STC        | Clear Output Port Bits 1<br>Command               | COPBC      |

Table 1. DUART Port And Register Addressing

#### Note:

The shaded blocks are not Read/Write registers but rather, "Address-Triggered" Commands.

Table 1 indicates that each channel is equipped with two "Mode Registers". Associated with each of these "Mode Register" pairs is a "Mode Register" pointer or MR pointer. Upon chip/system power up or RESET each MR pointer is "pointing to" the channel MR1n register. (Please note that the suffix "n" is used at the end of many of these register symbols in order to refer, generically, to either channels A or B). However, the contents of the MR pointer will shift from the address of the MR1n register to that of the MR2n register, immediately following any read or write access to the MR1n register. The MR pointer will continue to "point to" the MR2n register until a hardware reset occurs or until a "RESET MR POINTER" command has been invoked. The "RESET MR POINTER" command can be

issued by writing the appropriate data to the appropriate channel's command register. Therefore, both mode registers, within a given channel, have the same logical address. The features and functions of the DUART that are controlled by the mode registers are discussed in detail in *Section G.3*.

## **B.2 COMMAND DECODING**

Each channel is equipped with a command register. In general, the role of these command registers are to enable/disable the transmitter, enable/disable the receiver, along with facilitating a series of other miscellaneous commands. The bit format for each command register is presented below.

| Bit 7                  | Bit 6     | Bit 5     | Bit 4 | Bit 3                                               | Bit 2                         | Bit 1                          | Bit 0   |  |

|------------------------|-----------|-----------|-------|-----------------------------------------------------|-------------------------------|--------------------------------|---------|--|

| Miscellaneous Commands |           |           |       | Enable/Disab                                        | e Transmitter                 | Enable/Disable Receiver        |         |  |

|                        | See Follo | wing Text |       | 00 = No<br>01 = En<br>10 = Dis<br>11 = No<br>(Do no | able Tx<br>able Tx<br>t Valid | 01 = Er<br>10 = Dis<br>11 = No | able Rx |  |

Table 2. Command Register - CRA, CRB

The function of the lower nibble of the command registers is fairly straight-forward. This nibble is used to either enable or disable the transmitter and/or receiver.

The upper nibble of the command register is used to invoke a series of miscellaneous commands. *Table 3* defines the commands associated with the upper nibble of the command registers. Please note that the upper nibble commands 116 through  $B_{16}$  effects only the performance of command register's channel. However, commands C16 through  $F_{16}$  effects system (or chip) level operation.

|   | Bit 6 | Bit 5 | Bit 4 | Description                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|---|-------|-------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 0 | 0     | 0     | 0     | Null Command:                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| 0 | 0     | 0     | 1     | Reset MRn Pointer: Causes the channel's MRn pointer to point to MR1n.                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 0 | 0     | 1     | 0     | <b>Reset Receiver:</b> Resets the individual channel receiver as if a hardware reset has been applied. The Receiver is disabled and the FIFO is flushed.                                                                                                                                                                                                                                                                         |  |  |  |

| 0 | 0     | 1     | 1     | <b>Reset Transmitte</b> r: Resets the individual channel transmitter as if a hardware reset had been applied. The TXDn output is forced to a high level.                                                                                                                                                                                                                                                                         |  |  |  |

| 0 | 1     | 0     | 0     | Reset Error Status: Clears the Received Break (RB), Parity Error (PE), Framing Error (FE) and Overrun Error (OE) status bits, SR[7:3].                                                                                                                                                                                                                                                                                           |  |  |  |

|   |       |       |       | Specifically, if the error mode, for a particular channel is set at "Block" error mode, this command will reset the all of the receiver error indicators in the status register. In the block error mode, once either a PE, FE, OE or RB occurs, this error will continue to be flagged in the channel status register, until this command is issued.                                                                            |  |  |  |

|   |       |       |       | If the Error Mode, for a particular channel is set at "Character" Error Mode, then the contents of the Status Register for PE, FE and RB are reflected on a character by character basic. In the "Character" Error Mode, the state of these indicators is based only upon the character that is at the top of the RHR.                                                                                                           |  |  |  |

|   |       |       |       | The OE indicator is always flagged as a "Block" Error Mode indicator, and requires this command to be reset.                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 0 | 1     | 0     | 1     | Reset Break Change Interrupt: Clears the channel's break change interrupt status bit.                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 0 | 1     | 1     | 0     | Start Break: Forces the TXDn output low. The transmitter must be enabled to start a break. If the transmitter is empty, the start of the break may be delayed up to two bit times. If the transmitter is active, the break begins when the transmission of those characters in the THR is completed, viz., TXEMP must be true before the break will begin.                                                                       |  |  |  |

| 0 | 1     | 1     | 1     | <b>Stop Break:</b> The TXDn line will go high within two bit times. TXDn will remain high for one bit time before the next character, if any, is transmitted.                                                                                                                                                                                                                                                                    |  |  |  |

| 1 | 0     | 0     | 0     | Set Rx BRG Select Extend Bit: Sets the channel's "Receiver BRG Select Extend Bit" to "1". (e.g. x=1)                                                                                                                                                                                                                                                                                                                             |  |  |  |

| 1 | 0     | 0     | 1     | Clear Rx BRG Select Extend Bit: Clears the channel's "Receiver BRG Select Extend Bit". (e.g. x=0)                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 1 | 0     | 1     | 0     | Set Tx BRG Select Extend Bit: Sets the channel's "Transmitter BRG Select Extend Bit" to "1".                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 1 | 0     | 1     | 1     | Clear Tx BRG Select Extend Bit: Clears the the channel's "Transmitter BRG Select Extend Bit" to "1".                                                                                                                                                                                                                                                                                                                             |  |  |  |

| 1 | 1     | 0     | 0     | Set Standby Mode (Channel A): When this command is invoked via the channel A command register, power is removed from each of the transmitters, receivers, Counter/Timer and additional circuits to place the DUART in the standby (or lower power) mode. Please note that this command effects the operation of the entire chip. Normal operation is restored by a hardware reset or by invoking the "SET AC TIVE MODE" command. |  |  |  |

| 1 | 1     | 0     | 1     | Set Active Mode (Channel A): When this command is invoked via the channel A command register, the DUART is removed from the standby mode and resumes normal operation.                                                                                                                                                                                                                                                           |  |  |  |

| 1 | 1     | 1     | 0     | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 1 | 1     | 1     | 1     | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

Table 3. Miscellaneous Commands, Upper Nibble of all Command Registers, Unless Otherwise Specified.

In addition to the commands which are available through the command registers, the DUART also offers "Address-Triggered" commands. These commands are listed in *Table 1*, DUART PORT AND REGISTER ADDRESSING"; and are further identified by being "shaded" in . Specifically, these commands are:

- START COUNTER/TIMER COMMAND

- STOP COUNTER/TIMER COMMAND

- SET OUTPUT PORT BITS COMMAND

- CLEAR OUTPUT PORT BITS COMMAND

Each of these commands are invoked by either reading or writing data to their corresponding DUART addresses as specified in *Table 1*.

For example, the START COUNTER/TIMER COMMAND is invoked by the procedure of reading DUART address 0E16. Please note that this "Read Operation" will not result in placing the contents of a DUART register on the data bus. The only thing that will happen, in response to this procedure; is that the Counter/Timer will initiate counting. For a detailed discussion into the operation of the Counter/Timers, please see *Section D.2*.

Another example of an "Address-Triggered" commands is the "SET OUTPUT PORT BITS 1" Command. This command is invoked by performing a write of data to DUART address 0E16. When the user invokes this command, he/she is setting certain bits (to "1") within the OPR (Output Port Register). All other bits, within the OPR (not specified to be set), are not changed.

The state of the output port pins are complements of the individual bits within the OPR. Hence, if OPR[0] is set to "1", the state of the corresponding output port pin, OP0, is now set to a logic "0". Consequently, one can think of the "SET OUTPUT PORT BITS" command as the "CLEAR OUTPUT PORT PINS" command. For a more detailed discussion into the operation of the output ports, please see *Section F*.

#### C. INTERRUPT CONTROL BLOCK

The interrupt control block allows the user to apply the DUART in an "Interrupt Driven" environment. The DUART includes an Interrupt Request output signal (INTR) is provided which may be programmed to be asserted upon the occurrence of any of the following events:

- Transmit Hold Register A or B ready

- Receive Hold Register A or B ready

- Receive FIFO A or B Full

- Start or End of Received Break in Channels A or B

- End of Counter/Timer Count Reached

- Change of State on input pins, IP0, IP1, IP2, IP3

The interrupt control block consists of an Interrupt Status Register (ISR), an Interrupt Mask Register (IMR), an Masked Interrupt Status Register (MISR) and an Interrupt Vector Register (IVR). *Table 4* lists these registers, and their address location (within the DUART).

| Register | Description                      | Address Location (in DUART Address Space) |  |  |  |

|----------|----------------------------------|-------------------------------------------|--|--|--|

| ISR      | Interrupt Status Register        | 0516 (Read Only)                          |  |  |  |

| IMR      | Interrupt Mask Register          | 0516(Write Only)                          |  |  |  |

| MISR     | Masked Interrupt Status Register | 0216(Read Only)                           |  |  |  |

| IVR      | Interrupt Vector Register        | 0C16                                      |  |  |  |

Table 4. Listing and Brief Description of Interrupt Control Block Registers

The role and purpose of each of these registers are defined as follows:

## C.1 Interrupt Status Registers (ISR)

The contents of the ISR indicates the status of all potential

interrupt conditions. If any bits within these registers are toggled "high", then the corresponding condition has or is occurring. In general, the contents of the ISR will indicate to the processor, the source or the reason for the interrupt request from the DUART. The bit-format of the ISR register is presented as follows.

| Bit 7                | Bit 6            | Bit 5            | Bit 4   | Bit 3            | Bit 2            | Bit 1            | Bit 0   |

|----------------------|------------------|------------------|---------|------------------|------------------|------------------|---------|

| Input Port<br>Change | Delta Break<br>B | RXRDY/<br>FFULLB | TXRDYB  | Counter<br>Ready | Delta Break<br>A | RXRDY/<br>FFULLA | TXRDYA  |

| 0 = No               | 0 = No           | 0 = No           | 0 = No  | 0 = No           | 0 = No           | 0 = No           | 0 = No  |

| 1 = Yes              | 1 = Yes          | 1 = Yes          | 1 = Yes | 1 = Yes          | 1 = Yes          | 1 = Yes          | 1 = Yes |

Table 5. Interrupt Status Register - (ISR) Bit Format

The meaning behind each of these bits is defined below.

# ISR[7]: Input Port Change of State:

If this bit is at a logic "1", then a "change of state" was detected at the IPO - IP3 pins. The user would service this interrupt by reading the IPCR (if ISR[7] = 1). ISR[7] is cleared when the CPU has read the IPCR. By reading the IPCR, the user will determine:

- The individual Input Port pin that changed state

- The final state of the monitored input ports, following the Change of State.

For a detailed description of the IPCR, please see *Section E*.

Please note that in order to enable this interrupt condition, the user must do two things:

- Write the appropriate data to the lower nibble of the Auxiliary Control Register, ACR[3:0]. In this step, the user is specifying which input pins should trigger an "Input Port Change" interrupt request.

- 2. Write a logic "1" to IMR[7].

# ISR[6] Delta Break Indicator - Channel B:

When this bit is set, it indicates that the channel B receiver has detected the beginning or end of a received break. This bit is cleared (or reset) when the CPU invokes a channel B "RESET BREAK CHANGE INTERRUPT" command. For more information into the DUART's response to a BREAK condition, please see *Section G.2*.

# ISR[5] RXRDYB/FFULLB - Channel B Receiver Ready or FIFO Full

The function of this bit is selected by programming MR1B[6]. If programmed as the Receiver Ready indicator (RXRDYB), it indicates that at least one character of data is in the RHRB and is ready to be read by the CPU. This bit is set when a character is transferred from the received shift register to RHRB and is cleared when the CPU reads RHRB. If there are still more characters in RHRB after the read operation, the bit will be set again after RHRB is "popped".

If this bit is programmed as FIFO Full indicator (FFULLB), it is set when a character is transferred from the RSR to RHRB and the transfer causes RHRB to become full. This bit is cleared when the CPU reads RHRB; and thereby "popping" the FIFO, making room for the next character. If a character is waiting in the RSR because RHRB is full, this bit will be set again after the read operation, when that character is loaded into RHRB.

# ISR[4] TXRDYB - Channel B Transmitter Ready

This bit, when set, indicates that THRB is empty and is ready to accept a character from the CPU. The bit is cleared when the CPU writes a new character to THRB; and is set again, when that character is transferred to the TSR. TXRDY is set when the transmitter is initially enabled and is cleared when the transmitter is disabled. Characters loaded into THRB while the transmitter is disabled will not be transmitted.

## **ISR[3] Counter Ready**

In the TIMER mode, the C/T (Counter/Timer) will set ISR[3] once each cycle of the resultant square wave (available at the OP3 pin). ISR[3] will be cleared by invoking the "STOP COUNTER" command. Bear in mind, that in the TIMER mode, the "STOP COUNTER" command will not stop the C/T.

In the COUNTER mode, this bit is set when the C/T reaches the terminal count (0000) 16 and is cleared when the C/T is stopped by a "STOP COUNTER" command. When the Counter/Timer is in the COUNTER mode, this command will stop the counter.

## ISR[2]: Delta Break Indicator - Channel A

Assertion of this bit indicates that the channel A receiver has detected the beginning or end of a Received Break (RB). This bit is cleared when the CPU invokes a channel A "RESET BREAK CHANGE INTERRUPT" command. For more information into the DUART's response to a BREAK condition, please see *Section G.2*.

# ISR[1] RXRDYA/FFULLA - Channel A Receiver Ready or FIFO Full

The function of this bit is selected by programming MR1A[6]. If programmed as the Receiver Ready indicator (RXRDYA), this bit indicates that there is at least one character of data in RHRA, and is ready to be read by the CPU. This bit is set when a character is transferred from the RSR to RHRA and is cleared when the CPU reads (or "pops") RHRA. If there are still more characters

in RHRA after the read operation, the bit will be set again after RHRA is "popped".

If this bit is programmed as the FIFO (RHR) full indicator (FFULLA), it is set when a character is transferred from the RSR to RHRA and the newly transferred character causes RHRA to become full. It is cleared when the CPU reads RHRA. If a character is waiting in the RSR because RHRA is full, this bit will be set again after the read operation, when that character is loaded into RHRA.

# ISR[0]: Channel A Transmitter Ready

This bit, when set, indicates that THRA is empty and is ready to accept a character from the CPU. The bit is cleared when the CPU writes a new character to THRA; and is set again, when that character is transferred to the TSR. TXRDY is set when the transmitter is initially enabled and is cleared when the transmitter is disabled. Characters loaded into THRA while the transmitter is disabled will not be transmitted.

# C.2 Interrupt Mask Register (IMR)

The interrupt mask register is a "Write Only" register which enables the user to select the conditions that will cause the DUART to issue an interrupt request to the processor. In other words, the use has the option of masking or blocking certain conditions from causing the DUART to issue an interrupt request. Therefore, the bit-format of the IMR is essentially the same as the ISR. However, for completeness, the bit format of the IMR is presented in the following table.

| Bit 7                | Bit 6            | Bit 5            | Bit 4   | Bit 3            | Bit 2            | Bit 1            | Bit 0   |

|----------------------|------------------|------------------|---------|------------------|------------------|------------------|---------|

| Input Port<br>Change | Delta Break<br>B | RXRDY/<br>FFULLB | TXRDYB  | Counter<br>Ready | Delta Break<br>A | RXRDY/<br>FFULLA | TXRDYA  |

| 0 = Off              | 0 = Off          | 0 = Off          | 0 = Off | 0 = Off          | 0 = Off          | 0 = Off          | 0 = Off |

| 1 = On               | 1 = On           | 1 = On           | 1 = On  | 1 = On           | 1 = On           | 1 = On           | 1 = On  |

Table 6. IMR Bit Format

If the user wishes to enable a certain interrupt, he/she should write a "1" to the bit, within the IMR, corresponding to that interrupt condition. Likewise, to disable or mask out a certain condition causing an interrupt, the user should write a "0" to the bit location corresponding to that condition. To enable all interrupts the user would write FFh (all "1"s) to this register.

Please note that IMR is a "write-only" register, and therefore, cannot be read by the processor.

# C.3 Masked Interrupt Status Register (MISR)

The contents of the MISR register is basically the results of ANDing the ISR and IMR together.

MISR Content = [ISR Contents] • [IMR Contents]

One limitation of interrupt routines that rely on reading the ISR is that the bits within the ISR can toggle "high" due to their corresponding conditions whether or not they are enabled by the IMR. Therefore, the user, following reading the interrupt status register, will have to make provisions for; and execute a "bit-by-bit" AND of the ISR and IMR contents. Since the IMR is a "Write Only" register and cannot be read by the processor, the contents of the IMR will have to be stored is system memory, for later recall. The additional hardware and software overhead required to suport this activity can be eliminated via use of the MISR.

# C.4 Interrupt Vector Register, IVR

The 68000 family of microprocessors supports vectored-interrupt processing. Specifically, during interrupt servicing, the DUART will respond to the interrupt acknowledge signal, from the CPU, by placing the contents of the IVR on the data bus, to be read by the CPU. During normal operation, the contents of the IVR is related to a location in memory, where the appropriate interrupt service routine (for the interrupting DUART) resides.

Therefore, in vectored interrupt applications, the contents of the IVR accomplish two things:

- 1. Identify the peripheral components requesting the interrupt.

- Allow the CPU to determine the location of; and branch program control to the location, in program memory, that contains the appropriate interrupt service routine for the interrupting DUART.

Consequently, during initialization of the DUART, the user will have to load the IVR with a hexadecimal numbers of values between 4016 (64)10 through FF16 (25510), inclusively. This is the range of the values, in the 680x0's exception vector table, that have been reserved for "User Interrupt Vector". The memory location of the "DUART" interrupt service routine can be found by multiplying the contents of the IVR by 4. Hence, the user should take care to make sure that the interrupt service routine starts at [Contents of IVR] • 4 in program memory.

The XR68C681, like many other 68000-series peripheral devices are designed such that the default contents of their IVR (following a RESET condition) is 0F16. Consequently, if, during an "interrupt acknowledge" cycle (see the next section) the CPU reads the value 0F16 from the DUART; and "Uninitialized Interrupt Vector" exception will be generated.

## C.5 Limitations of the DUART Interrupt Structure

The interrupt structure offered by the DUART allows the user to program the DUART to generate interrupts in response to certain THR and RHR (FIFO) conditions; the "Counter/Timer Ready" condition, and to changes in the break condition (at the Receiver). However, aside from the "Delta Break Condition", the DUART's interrupt structure does not allow for interrupt requests due to receiver problems such as Parity Error (PE), receiver Overrun Error (OE), or Framing Error (FE). The DUART also does not offer the user the ability to configure one of the output ports to relay the occurrence of any of these conditions. The user is, therefore, recommended to "validate" the receive data by frequently reading the status register; and checking for any non-zero upper nibble values. This is especially the case if the user has set the error mode to "Character" (MR1n[5] = 0).

# C.6 Servicing DUART Interrupts

The 68000 family of microprocessors supports vectored-interrupt processing. In vectored-interrupt processing, the peripheral device, responsible for requesting the interrupt, will identify itself to the microprocessor, during the "Interrupt Acknowledge" cycle. Once the microprocessor knows which peripheral device is requesting the interrupt, the microprocessor will determine the location of the appropriate interrupt service routine in memory, and branch program control to that location.

The advantage of using "Vectored-Interrupt" processing over "Polled-Interrupt" processing is significant in

time-critical applications using many peripherals devices. In "Polled-Interrupt" processing, upon the detection of the interrupt request, the microprocessor will have to go through and poll each and every peripheral device in order to determine the device causing the interrupt. Only after this polling procedure is completed can the microprocessor branch program control to the

appropriate interrupt service routine. The time required to poll each of these peripheral devices adds to the interrupt latency period over and above that which would occur during vectored-interrupt processing.

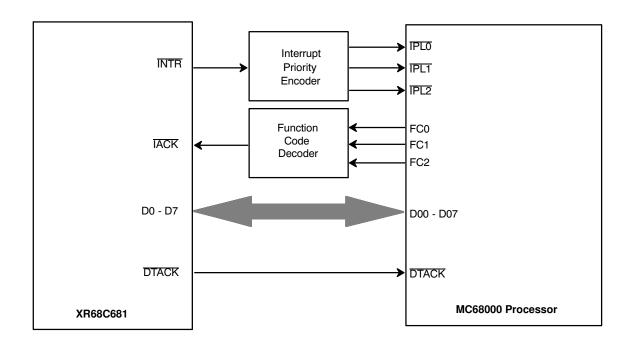

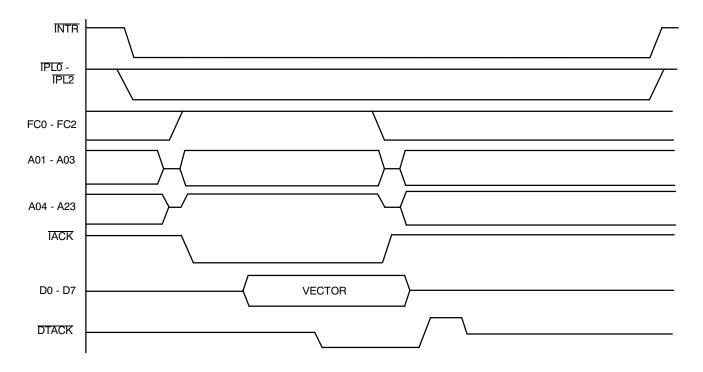

Figure 2 presents a simple illustration of how to interface the DUART to a 68000 processor for interrupt service considerations.

Figure 2. Simple Illustration Depicting the Interfacing of the XR68C681 DUART to a 68000 Processor

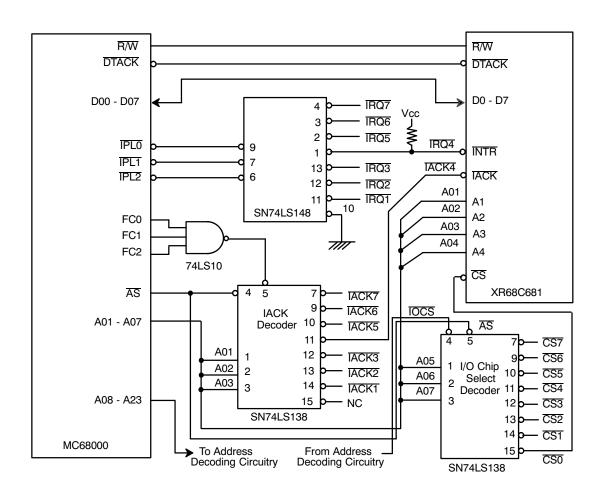

Figure 3 presents a more detailed schematic of the XR68C681 device interfacing to a 68000 microprocessor. This figure shows only the interrupt processing portion of the microprocessor/DUART interface. The address decoding circuitry for address bus bits A08 - A23 is not included. This circuit consists of an "Interrupt Priority Encoder" (SN74LS148), and two 3-line-to-8-line decoders (SN74LS138). For discussion purposes, one of these SN74LS138 devices are labeled "IACK Decoder" and the other is labeled "I/O Chip Select Decoder". In this figure, the DUART has an interrupt priority level of 4 (1002).