Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

### Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### **XRD8775**

CMOS 8-Bit High Speed Analog-to-Digital Converter

April 2002-4

### **FEATURES**

· 8-Bit Resolution

· Up to 20MHz Sampling Rate

· Internal S/H Function

· Single Supply: 5V

$\cdot$  V<sub>IN</sub> DC Range: 0V to V<sub>DD</sub>  $\cdot$  V<sub>RFF</sub> DC Range: 1V to V<sub>DD</sub>

· Low Power: 75mW typ. (excluding reference)

· Latch-Up Free

· ESD Protection: 2000V Minimum

· 3V Version: XRD87L75

Small 20-Pin SOIC/SSOP Packages

### **APPLICATIONS**

· Digital Color Copiers

· Cellular Telephones

· CCD-Based Systems

· Hardware Scanners

· Video Capture Boards

### **GENERAL DESCRIPTION**

The XRD8775 is an 8-bit Analog-to-Digital Converter in a small 20-pin SOIC/SSOP package. Designed using an advanced 5V CMOS process, this part offers excellent performance, low power consumption and latch-up free operation.

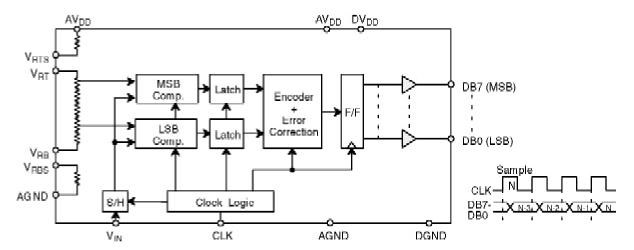

This device uses a two-step flash architecture to maintain low power consumption at high conversion rates. The input circuitry of the XRD8775 includes an on-chip S/H function and allows the user to digitize analog input signals between AGND and  ${\rm AV}_{\rm DD}$ . Careful design and chip layout have achieved a low analog input capacitance. This reduces "kickback" and eases the requirements of the buffer/amplifier used to drive the XRD8775.

The designer can choose the internally generated reference voltages by connecting  $V_{\text{RB}}$  to  $V_{\text{RBS}}$  and  $V_{\text{RT}}$  to  $V_{\text{RTS}}$ , or provide external reference voltages to the  $V_{\text{RB}}$  and  $V_{\text{RT}}$  pins. The internal reference generates 0.6V at  $V_{\text{RB}}$  and 2.6V at  $V_{\text{RT}}$ . Providing external reference voltages allows easy interface to any input signal range between GND and  $V_{\text{DD}}$ . This also allows the system to adjust these voltages to cancel zero scale and full scale errors, or to change the input range as needed.

The device operates from a single +5V supply. Power consumption is 75mW at  $F_s$  = 15MHz.

Specified for operation over the commercial / industrial (-40 to +85°C) temperature range, the XRD8775 is available in Surface Mount (SOIC), Shrink Small Outline (SSOP) and Plastic Dual-In-line (PDIP) Packages.

### SIMPLIFIED BLOCK AND TIMING DIAGRAM

Rev. 4.00

### **ORDERING INFORMATION**

| Package<br>Type | Temperature<br>Range | Part No.   | DNL<br>(LSB) | INL<br>(LSB) |

|-----------------|----------------------|------------|--------------|--------------|

| SOIC            | -40 to +85°C         | XRD8775AID | +/-0.75      | +/-1.5       |

| PDIP            | -40 to +85°C         | XRD8775AIP | +/-0.75      | +/-1.5       |

| SSOP            | -40 to +85°C         | XRD8775AIU | +/-0.75      | +/-1.5       |

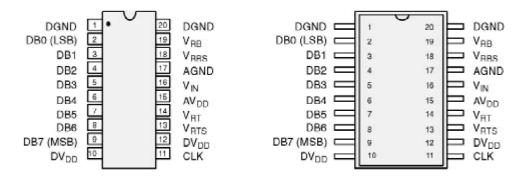

### **PIN CONFIGURATIONS**

See Packaging Section for Package Dimensions

20-Pin PDIP (300 MIL) - P20

20-Pin SOIC (Jedec, 300 MIL) - D20 20-Pin SSOP (5.3mm) - U20

### **PIN OUT DEFINITIONS**

| PIN NO. | NAME               | DESCRIPTION             | PIN NO. | NAME               | DESCRIPTION                               |

|---------|--------------------|-------------------------|---------|--------------------|-------------------------------------------|

| 1       | DGND               | Digital Ground          | 11      | CLK                | Sample Clock                              |

| 2       | DB0                | Data Output Bit 0 (LSB) | 12      | $DV_{DD}$          | Digital Power Supply                      |

| 3       | DB1                | Data Output Bit 1       | 13      | $V_{RTS}$          | Generates 2.6V if tied to $V_{\text{RT}}$ |

| 4       | DB2                | Data Output Bit 2       | 14      | $V_{RT}$           | Top Reference                             |

| 5       | DB3                | Data Output Bit 3       | 15      | $AV_{\mathtt{DD}}$ | Analog Power Supply                       |

| 6       | DB4                | Data Output Bit 4       | 16      | V <sub>IN</sub>    | Analog Input                              |

| 7       | DB5                | Data Output Bit 5       | 17      | AGND               | Analog Ground                             |

| 8       | DB6                | Data Output Bit 6       | 18      | $V_{RBS}$          | Generates 0.6V if tied to $V_{\tiny RB}$  |

| 9       | DB7                | Data Output Bit 7 (MSB) | 19      | $V_{RB}$           | Bottom Reference                          |

| 10      | $DV_{\mathtt{DD}}$ | Digital Power Supply    | 20      | DGND               | Digital Ground                            |

# ELECTRICAL CHARACTERISTICS TABLE UNLESS OTHERWISE SPECIFIED: $AV_{DD} = DV_{DD} = 5V$ , FS = 15MHZ (50% DUTY CYCLE), $V_{RT} = 2.6V$ , $V_{RB} = 0.6V$ , $T_A = 25^{\circ}C$

|                                            |                       |          | 25°C   |                    |        |                                     |

|--------------------------------------------|-----------------------|----------|--------|--------------------|--------|-------------------------------------|

| Parameter                                  | Symbol                | Min      | Тур    | Max                | Units  | Test Conditions/Comments            |

| KEYFEATURES                                |                       |          |        |                    |        |                                     |

| Resolution                                 |                       | 8        |        |                    | Bits   |                                     |

| Sampling Rate                              | FS                    | 0.1      | 15     | 20                 | MHz    |                                     |

| ACCURACY                                   |                       |          |        |                    |        |                                     |

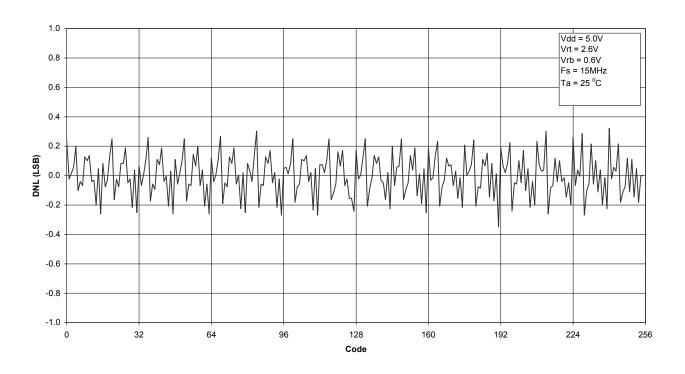

| Differential Non-Linearity                 | DNL                   |          |        | +/-0.75            | LSB    | @ 15MHz                             |

| Differential Non-Linearity                 | DNL                   |          | +/-0.5 |                    | LSB    | @ 10MHz                             |

| Integral Non-Linearity                     | INL                   |          |        | +/-1.5             | LSB    | Best Fit Line                       |

|                                            |                       |          |        |                    |        | (Max INL – Min INL)/2               |

| Zero Scale Error                           | EZS                   |          | +3     |                    | LSB    |                                     |

| Full Scale Error                           | EFS                   |          | -2     |                    | LSB    |                                     |

| REFERENCEVOLTAGES                          |                       |          |        |                    |        |                                     |

| Positive Ref. Voltage                      | $V_{RT}$              |          | 2.6    | $AV_{\mathtt{DD}}$ | V      |                                     |

| Negative Ref. Voltage                      | $V_{RB}$              | AGND     | 0.6    |                    | V      |                                     |

| Differential Ref. Voltage <sup>3</sup>     | V <sub>REF</sub>      | 1.0      |        | $AV_{\mathtt{DD}}$ | V      | $V_{REF} = V_{RT} - V_{RB}$         |

| Ladder Resistance                          | R <sub>L</sub>        | 245      | 350    | 550                | Ω      |                                     |

| Ladder Temp. Coefficient                   | R <sub>TCO</sub>      |          | 2000   |                    | ppm/°C |                                     |

| Self Bias 1                                |                       |          |        |                    |        |                                     |

| Short $V_{RB}$ and $V_{RBS}$               | $V_{RB}$              |          | 0.6    |                    | V      |                                     |

| Short V <sub>RT</sub> and V <sub>RTS</sub> | $V_{RT}$ - $V_{RB}$   |          | 2      |                    | V      |                                     |

| Self Bias 2                                |                       |          |        |                    |        |                                     |

| $V_{RB} = AGND,$                           | $V_{RT}$              |          | 2.3    |                    | V      |                                     |

| Short $V_{RT}$ and $V_{RTS}$               |                       |          |        |                    |        |                                     |

| ANALOGINPUT                                |                       |          |        |                    |        |                                     |

| Input Bandwidth (-1 dB) <sup>2,4</sup>     | BW                    |          | 50     |                    | MHz    |                                     |

| Input Voltage Range                        | $V_{IN}$              | $V_{RB}$ |        | $V_{RT}$           | V      |                                     |

| Input Capacitance 5                        | $C_{IN}$              |          | 16     |                    | pF     |                                     |

| Aperture Delay <sup>2</sup>                | t <sub>AP</sub>       |          | 3      |                    | ns     |                                     |

| DIGITALINPUTS                              |                       |          |        |                    |        |                                     |

| Logical "1" Voltage                        | $V_{IH}$              | 4.0      |        |                    | V      |                                     |

| Logical "0" Voltage                        | $V_{\text{\tiny IL}}$ |          |        | 1.0                | V      |                                     |

| DC Leakage Current <sup>6</sup>            | I <sub>IN</sub>       |          |        |                    |        | $V_{IN}$ = DGND to DV <sub>DD</sub> |

| CLK                                        |                       |          | 5      |                    | μΑ     |                                     |

| Input Capacitance                          |                       |          | 5      |                    | pF     |                                     |

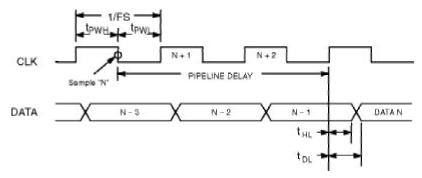

| Clock Timing ( See Figure 1.)7             |                       |          |        |                    |        |                                     |

| Clock Period                               | 1/FS                  | 50       | 66.7   |                    | ns     |                                     |

| High Pulse Width                           | t <sub>PWH</sub>      | 25       | 33.3   |                    | ns     |                                     |

| Low Pulse Width                            | t <sub>PWL</sub>      | 25       | 33.3   |                    | ns     |                                     |

| DIGITAL OUTPUTS                            |                       |          |        |                    |        | С <sub>оит</sub> =15 pF             |

| Logical "1" Voltage                        | $V_{OH}$              | 4.5      |        |                    | V      | I <sub>LOAD</sub> = 4 mA            |

| Logical "0" Voltage                        | V <sub>OL</sub>       |          |        | 0.4                | V      | I <sub>LOAD</sub> = 4 mA            |

| Data Valid Delay 8                         | t <sub>DL</sub>       |          | 10     |                    | ns     |                                     |

# ELECTRICAL CHARACTERISTICS TABLE (CONT'D) UNLESS OTHERWISE SPECIFIED: $AV_{DD} = DV_{DD} = 5V$ , FS = 15MHZ (50% DUTY CYCLE), $V_{RT} = 2.6V$ , $V_{RB} = 0.6V$ , $T_A = 25^{\circ}C$

|                                                                                       |                            |     | 25°C |     |        |                               |

|---------------------------------------------------------------------------------------|----------------------------|-----|------|-----|--------|-------------------------------|

| Parameter                                                                             | Symbol                     | Min | Тур  | Max | Units  | Test Conditions/Comments      |

| ACPARAMETERS                                                                          |                            |     |      |     |        |                               |

| Differential Gain Error                                                               | $d_{\scriptscriptstyle G}$ |     | 2    |     | %      | FS = 4 x NTSC                 |

| Differential Phase Error                                                              | $d_{PH}$                   |     | 1    |     | Degree | FS = 4 x NTSC                 |

| POWER SUPPLIES                                                                        |                            |     |      |     |        |                               |

| Operating Voltage (AV <sub>DD</sub> , DV <sub>DD</sub> ) <sup>9</sup> V <sub>DD</sub> |                            | 4.5 | 5    | 5.5 | V      |                               |

| Current (AGND + DGND)                                                                 | I <sub>DD</sub>            |     | 15   | 25  | mA     | Does not include ref. current |

#### NOTES

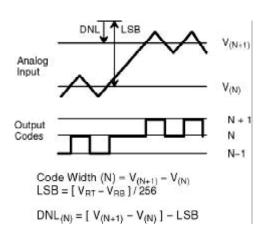

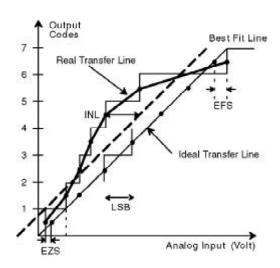

- 1. The difference between the measured and the ideal code width (V<sub>REF</sub>/256) is the DNL error (Figure 3). The INL error is the maximum distance (in LSBs) from the best fit line to any transition voltage (Figure 4). Accuracy is a function of the sampling rate (FS).

- 2. Guaranteed, not tested.

- 3. Specified values guarantee functionality. Refer to other parameters for accuracy.

- 4. -1dB bandwidth is a measure of performance of the A/D input stage (S/H + amplifier). Refer to other parameters for accuracy within the specified bandwidth.

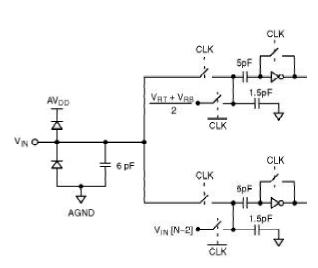

- $5. \, \mathrm{See} \, V_{\scriptscriptstyle N}$  input equivalent circuit (Figure  $5). \, \mathrm{Switched}$  capacitor analog input requires driver with low output resistance.

- 6. All inputs have diodes to DV DD and DGND. Input DC currents will not exceed specified limits for any input voltage between DGND and DV DD.

- 7.  $t_R$ ,  $t_F$  should be limited to >5ns for best results.

- 8. Depends on the RC load connected to the output pin.

- 9. AGND & DGND pins are connected through the silicon substrate. Connect together at the package and to the analog ground plane.

### Specifications are subject to change without notice

### ABSOLUTE MAXIMUM RATINGS (T<sub>A</sub> = +25°C unless otherwise noted)<sup>1, 2, 3</sup>

| V <sub>DD</sub> to GND7V                          | Storage Temperature65 to +150°C                |

|---------------------------------------------------|------------------------------------------------|

| $V_{RT}$ & V RB $V_{DD}$ +0.5 to GND –0.5V        | Lead Temperature (Soldering 10 seconds) +300°C |

| $V_{\text{IN}}$ $V_{\text{DD}}$ +0.5 to GND –0.5V | Package Power Dissipation Rating @ 75°C        |

| All InputsV <sub>DD</sub> +0.5 to GND -0.5V       | PDIP, SOIC, SSOP650mW                          |

| All OutputsV <sub>DD</sub> +0.5 to GND –0.5V      | Derates above 75°C 9mW/°C                      |

#### NOTES:

<sup>1.</sup> Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation at or above this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

<sup>2.</sup> Any input pin which can see a value outside the absolute maximum ratings should be protected by Schottky diode clamps (HP5082-2835) from input pin to the supplies. All inputs have protection diodes which will protect the device from short transients outside the supplies of less than 100µA for less than 100ms.

<sup>3.</sup>  $V_{\rm DD}$  refers to  $AV_{\rm DD}$  and  $DV_{\rm DD}$ . GND refers to AGND and DGND.

Figure 1. XRD8775 Timing Diagram

Figure 2. DNL Measurement

Figure 3. INL Error Calculation

Figure 4. Equivalent Input Circuit

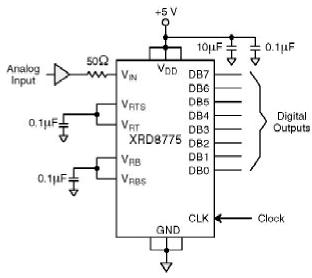

Figure 5. Typical Circuit Connections

### **APPLICATION NOTES**

Signals should not exceed AV<sub>DD</sub> +0.5V or go below AGND -0.5V or DV<sub>DD</sub> +0.5V or DGND -0.5V. All pins have internal protection diodes that will protect them from short transients (<100 $\mu$ s) outside the supply range.

AGND and DGND pins are connected internally through the P-substrate. DC voltage differences between these pins will cause undesirable internal substrate currents.

The power supply (AV<sub>DD</sub>) and reference voltage (V<sub>RT</sub> & V<sub>RB</sub>) pins should be decoupled with  $0.1\mu F$  and  $10\mu F$  capacitors to AGND, placed as close to the chip as possible.

The digital outputs should not drive long wires or buses. The capacitive coupling and reflections will contribute noise to the conversion.

To avoid timing errors, use the rising edge of the sample clock (CLK) to latch data from the XRD8775 to other parts of the system.

The reference can be biased internally by shorting  $V_{RT}$  to  $V_{RTS}$  and  $V_{RB}$  to  $V_{RBS}$ . This will generate 0.6V at  $V_{RB}$  and 2.6V at  $V_{RT}$  (see *Figure 5*.).

If the internal reference pins  $V_{\text{RTS}}$  and/or  $V_{\text{RBS}}$  are not used they should be left unconnected.

Graph 1. DNL vs. Code

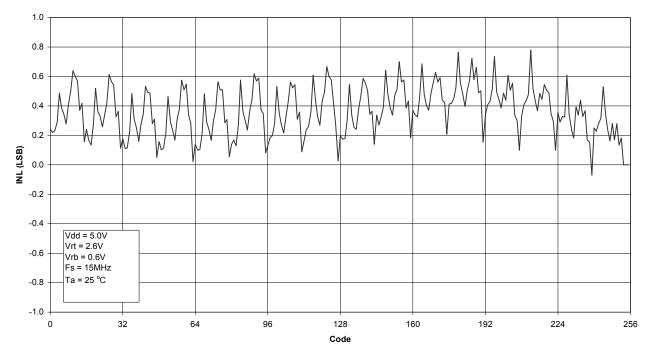

Graph 2. INL vs. Code

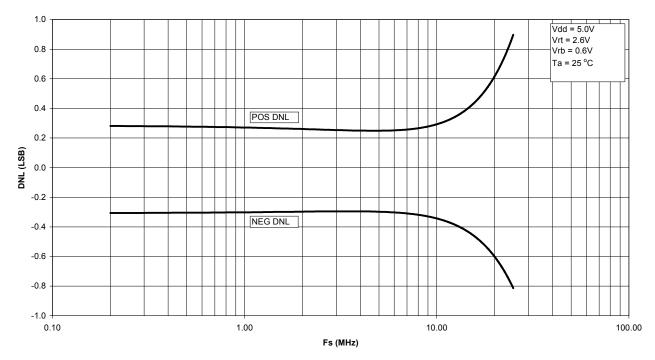

**Graph 3. DNLvs. Sampling Frequency**

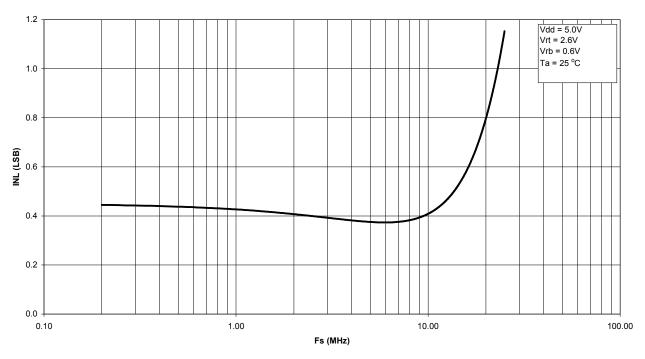

Graph 4. Best Fit INL vs. Sampling Frequency

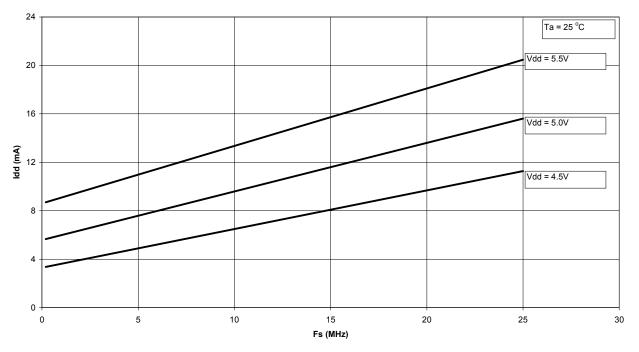

**Graph 5. IDD vs. Sampling Frequency**

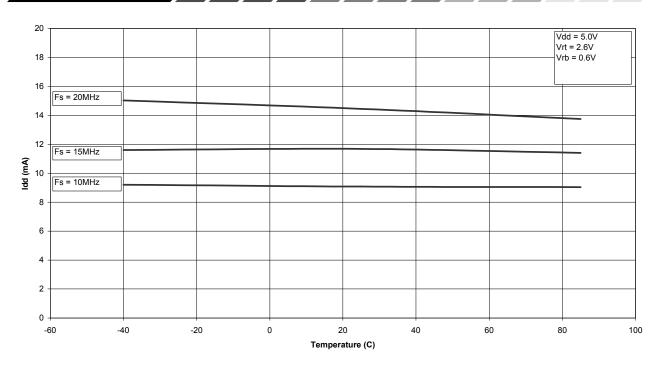

**Graph 6. Supply Current vs. Temperature**

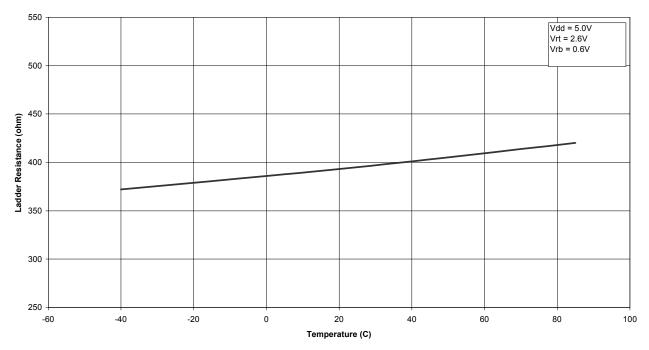

Graph 7. Ladder Resistance vs. Temperature

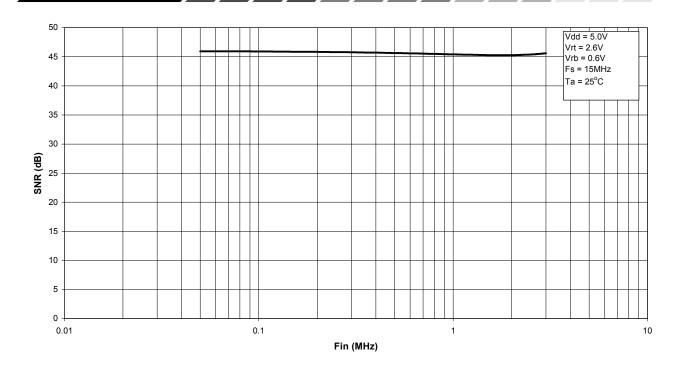

Graph 8. SNR vs. Input Frequency

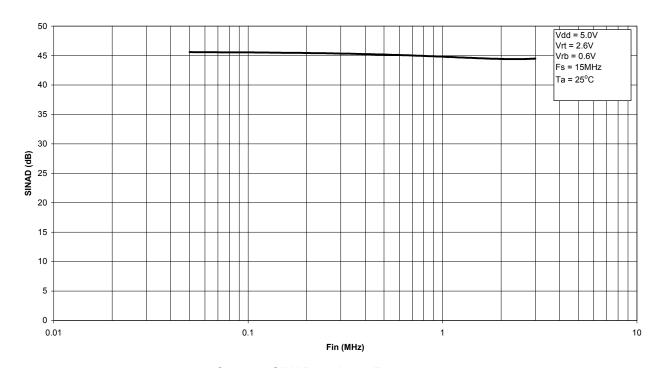

**Graph 9. SINAD vs. Input Frequency**

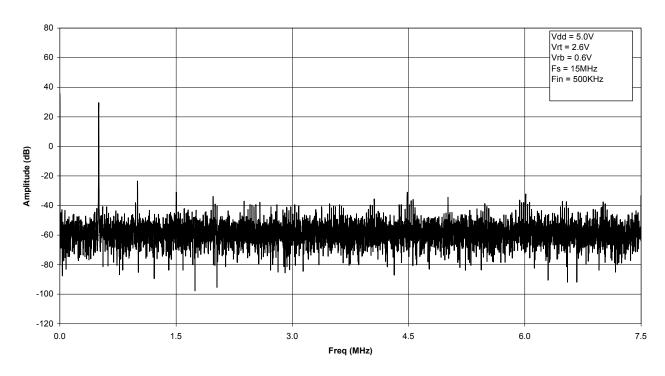

Graph 10. FFT Plot

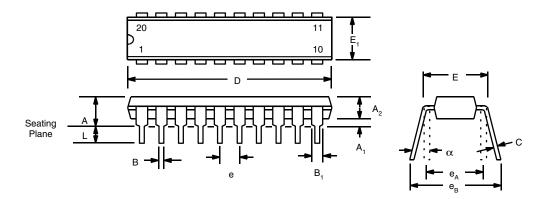

### 20 LEAD PLASTIC DUAL-IN-LINE (300 MIL PDIP) REV. 1.00

Note: The control dimension is the inch column

|        | INC       | HES   | MILL  | IMETERS |

|--------|-----------|-------|-------|---------|

| SYMBOL | MIN       | MAX   | MIN   | MAX     |

| Α      | 0.145     | 0.210 | 3.68  | 5.33    |

| A1     | 0.015     | 0.070 | 0.38  | 1.78    |

| A2     | 0.115     | 0.195 | 2.92  | 4.95    |

| В      | 0.014     | 0.024 | 0.36  | 0.56    |

| B1     | 0.030     | 0.070 | 0.76  | 1.78    |

| С      | 0.008     | 0.014 | 0.20  | 0.38    |

| D      | 0.925     | 1.060 | 23.50 | 26.92   |

| E      | 0.300     | 0.325 | 7.62  | 8.26    |

| E1     | 0.240     | 0.280 | 6.10  | 7.11    |

| е      | 0.10      | 0 BSC | 2.54  | BSC     |

| eA     | 0.300 BSC |       | 7.62  | BSC     |

| eB     | 0.310     | 0.430 | 7.87  | 10.92   |

| L      | 0.115     | 0.160 | 2.92  | 4.06    |

| а      | 0°        | 15°   | 0°    | 15°     |

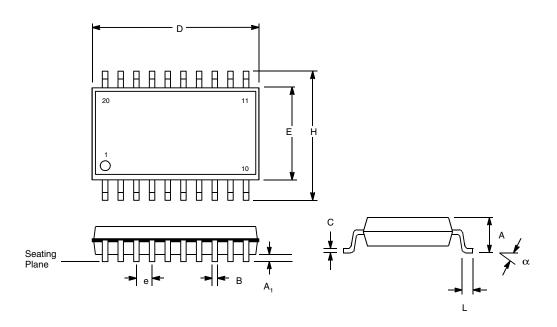

### 20 LEAD SMALL OUTLINE (300 MIL JEDEC SOIC) REV. 1.00

NOTE: The control dimension is the millimeter column

|        | IN    | CHES   | MILLIMETERS |       |  |

|--------|-------|--------|-------------|-------|--|

| SYMBOL | MIN   | MAX    | MIN         | MAX   |  |

| Α      | 0.093 | 0.104  | 2.35        | 2.65  |  |

| A1     | 0.004 | 0.012  | 0.10        | 0.30  |  |

| В      | 0.013 | 0.020  | 0.33        | 0.51  |  |

| С      | 0.009 | 0.013  | 0.23        | 0.32  |  |

| D      | 0.496 | 0.512  | 12.60       | 13.00 |  |

| E      | 0.291 | 0.299  | 7.40        | 7.60  |  |

| е      | 0.05  | 50 BSC | 1.27 BSC    |       |  |

| Н      | 0.394 | 0.419  | 10.00       | 10.65 |  |

| L      | 0.016 | 0.050  | 0.40        | 1.27  |  |

| а      | 0°    | 8°     | 0°          | 8°    |  |

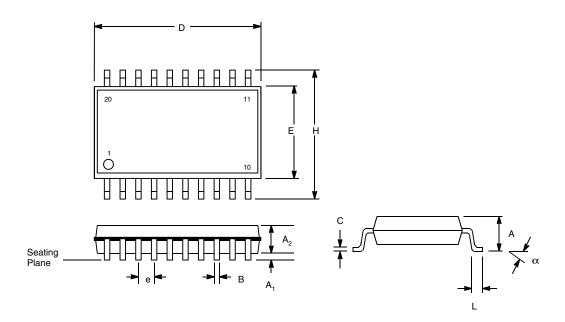

## 20 LEAD SHRINK SMALL OUTLINE PACKAGE (5.3 mm SSOP) REV. 2.00

Note: The control dimension is the millimeter column

|        | INC   | HES     | MILL | IMETERS |

|--------|-------|---------|------|---------|

| SYMBOL | MIN   | MAX     | MIN  | MAX     |

| Α      | 0.067 | 0.079   | 1.70 | 2.00    |

| A1     | 0.002 | 0.006   | 0.05 | 0.15    |

| A2     | 0.065 | 0.073   | 1.65 | 1.85    |

| В      | 0.009 | 0.015   | 0.22 | 0.38    |

| С      | 0.004 | 0.010   | 0.09 | 0.25    |

| D      | 0.272 | 0.296   | 6.90 | 7.50    |

| E      | 0.197 | 0.221   | 5.00 | 5.60    |

| е      | 0.02  | 256 BSC | 0.65 | BSC     |

| Н      | 0.292 | 0.323   | 7.40 | 8.20    |

| L      | 0.022 | 0.037   | 0.55 | 0.95    |

| а      | 0°    | 8°      | 0°   | 8°      |

### NOTICE

EXAR Corporation reserves the right to make changes to the products contained in this publication in order to improve design, performance or reliability. EXAR Corporation assumes no responsibility for the use of any circuits described herein, conveys no license under any patent or other right, and makes no representation that the circuits are free of patent infringement. Charts and schedules contained here in are only for illustration purposes and may vary depending upon a user's specific application. While the information in this publication has been carefully checked; no responsibility, however, is assumed for in accuracies.

EXAR Corporation does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless EXAR Corporation receives, in writing, assurances to its satisfaction that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; (c) potential liability of EXAR Corporation is adequately protected under the circumstances.

Copyright 2002 EXAR Corporation Datasheet April 2002

Reproduction, in part or whole, without the prior written consent of EXAR Corporation is prohibited.