# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### 14-Bit Linear CIS/CCD Sensor Signal Processor with Serial Control

May 2000-3

#### FEATURES

- 14-Bit Resolution, No Missing Codes

- One-channel 6MSPS Pixel Rate

- Triple-channel 2MSPS Pixel Rate

- 6-Bit Programmable Gain Amplifier

- 8-Bit Programmable Offset Adjustment

- CIS or CCD Compatibility

- Internal Clamp for CIS or CCD AC Coupled Configurations

- 5V Operation

- Serial Load Control Registers

- Low Power CMOS: 200mW-typ

- Low Cost 20-Lead Packages

- USB Compliant

#### **GENERAL DESCRIPTION**

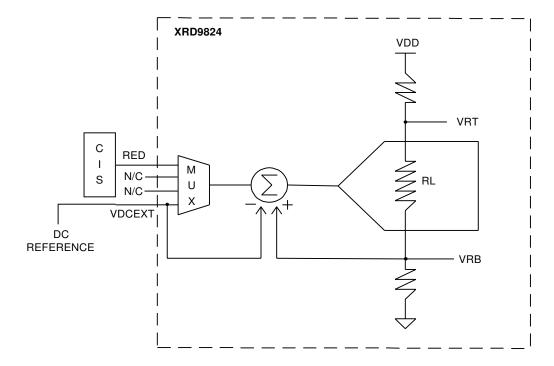

The XRD9824 is a complete linear CIS or CCD sensor signal processor on a single monolithic chip. The XRD9824 includes a high speed 14-bit resolution ADC, a 6-bit Programmable Gain Amplifier with gain adjustment of 1 to 10, and 8-bit programmable input referred offset calibration range of 800mV.

In the CCD configuration the input signal is AC coupled with an external capacitor. An internal clamp sets the black level. In the CIS configuration, the clamp switch can be disabled and the CIS output signal is DC coupled from the CIS sensor to the XRD9824. The CIS signal is level shifted to VRB in

order to use the full range of the ADC. In the CIS configuration the input can also be AC coupled similar to the CCD configuration. This enables CIS signals with large black levels to be internally clamped to a DC reference equal to the black level. The DC reference is internally subtracted from the input signal.

The CIS configuration can also be used in other applications that do not require CDS function, such as low cost data acquisition.

#### **ORDERING INFORMATION**

Rev.

2.00

| Package Type | Temperature Range | Part Number |

|--------------|-------------------|-------------|

| 20-Lead SOIC | 0°C to +70°C      | XRD9824ACD  |

| 20-Lead SSOP | 0°C to +70°C      | XRD9824ACU  |

EXAR Corporation, 48720 Kato Road, Fremont, CA 94538 • (510) 668-7000 • FAX (510) 668-7017 • www.exar.com

#### APPLICATIONS

- Color and Grayscale Flatbed Scanners

- Color and Grayscale Sheetfed Scanners

- Multifunction Peripherals

- Digital Color Copiers

- General Purpose CIS or CCD Imaging

- Low Cost Data Acquisition

- Simple and Direct Interface to Canon 600 DPI Sensors

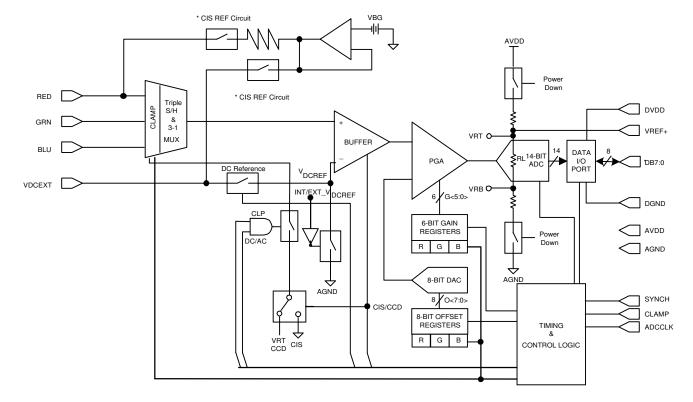

Note: \* For Canon CIS Sensor

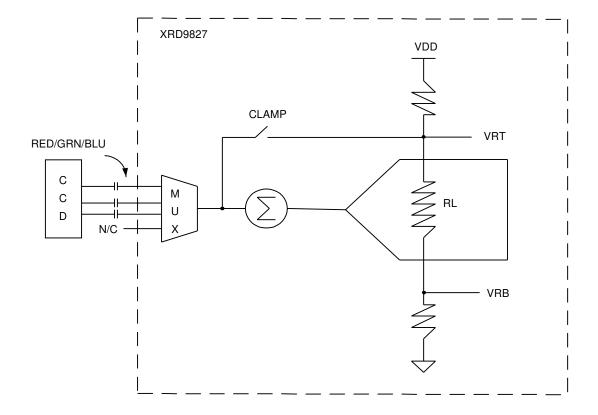

Figure 1. Functional Block Diagram

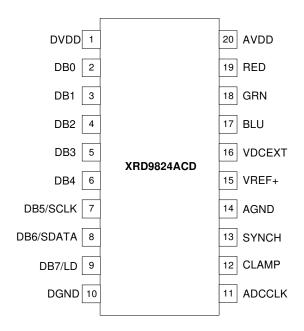

#### **PIN CONFIGURATION**

20-Lead SOIC

#### **PIN DESCRIPTION**

| Pin # | Symbol    | Description                                     |

|-------|-----------|-------------------------------------------------|

| 1     | DVDD      | Digital VDD (for Output Drivers)                |

| 2     | DB0       | Data Output Bit 0                               |

| 3     | DB1       | Data Output Bit 1                               |

| 4     | DB2       | Data Output Bit 2                               |

| 5     | DB3       | Data Output Bit 3                               |

| 6     | DB4       | Data Output Bit 4                               |

| 7     | DB5/SCLK  | Data Output Bit 5 & Data Input SCLK             |

| 8     | DB6/SDATA | Data Output Bit 6 & Data Input SDATA            |

| 9     | DB7/LD    | Data Output Bit 7 & LD                          |

| 10    | DGND      | Digital Ground (for Output Drivers)             |

| 11    | ADCCLK    | A/D Converter Clock                             |

| 12    | CLAMP     | Clamp and Video Sample Clock                    |

| 13    | SYNCH     | Start of New Line and Serial Data Input Control |

| 14    | AGND      | Analog Ground                                   |

| 15    | VREF+     | A/D Positive Reference for Decoupling Cap       |

| 16    | VDCEXT    | External DC Reference                           |

| 17    | BLU       | Blue Input                                      |

| 18    | GRN       | Green Input                                     |

| 19    | RED       | Red Input                                       |

| 20    | AVDD      | Analog Power Supply                             |

Rev. 2.00

#### **ELECTRICAL CHARACTERISTICS**

Test Conditions:  $AV_{DD}=DV_{DD}=5V$ , ADCCLK=6MHz, 50% Duty Cycle,  $T_A=25^{\circ}C$  unless otherwise specified.

| Symbol              | Parameter                            | Min.  | Тур.          | Max.  | Unit | Conditions              |

|---------------------|--------------------------------------|-------|---------------|-------|------|-------------------------|

| Power Supplies      |                                      |       |               |       |      |                         |

| AV                  | Analog Power Supply                  | 3.0   | 3.3           | 5.5   | V    | (Note 2)                |

|                     | Digital I/O Power Supply             | 3.0   | 3.3           | 5.5   | V    | $DV_{DD} \le AV_{DD}$   |

| I <sub>DD</sub>     | Supply Current                       |       | 40            | 55    | mA   | V <sub>DD</sub> =5V     |

| IDD <sub>PD</sub>   | Power Down Power Supply Current      |       |               | 50    | μA   | V <sub>DD</sub> =5V     |

| ADC Specific        | ations                               |       |               |       |      |                         |

| RES                 | Resolution                           | 14    |               |       | Bits |                         |

| Fs                  | Maximum Sampling Rate                | 12    |               |       | MSPS |                         |

| DNL                 | Differential Non-Linearity           | -3.0  | ±1.5          | 3.0   | LSB  |                         |

| V <sub>RT</sub>     | Top Reference Voltage                | 3.50  | $AV_{DD}/1.3$ | 3.90  | V    |                         |

| V <sub>RB</sub>     | Bottom Reference Voltage             |       | $AV_{DD}/10$  |       | V    |                         |

| $DV_{REF}$          | Differential Reference Voltage       | 0.3   | $0.67AV_{DD}$ |       | V    |                         |

|                     | (V <sub>RT</sub> - V <sub>RB</sub> ) |       |               |       |      |                         |

| $R_{L}$             | Ladder Resistance                    | 300   | 600           | 780   | Ω    |                         |

| PGA & Offset        | DAC Specifications                   |       |               |       |      |                         |

| PGARES              | PGA Resolution                       | 6     |               |       | Bits |                         |

| PGAG <sub>MIN</sub> | Minimum Gain                         | 0.950 | 1.0           | 1.050 | V/V  |                         |

| PGAG <sub>MAX</sub> | Maximum Gain                         | 9.5   | 10.0          | 10.50 | V/V  |                         |

| PGAGD               | Gain Adjustment Step Size            |       | 0.14          |       | V/V  |                         |

| V <sub>BLACK</sub>  | Black Level Input Range              | -100  |               | 500   | mV   | DC Configuration        |

| DACRES              | Offset DAC Resolution                | 8     |               |       | Bits |                         |

|                     | Minimum Offset Adjustment            | -250  | -200          | -150  | mV   | Mode 111, D5=0 (Note 1) |

|                     | Maximum Offset Adjustment            | +500  | +600          | +700  | mV   | Mode 111, D5=0          |

|                     | Minimum Offset Adjustment            | -450  | -400          | -350  | mV   | Mode 111, D5=1 (Note 1) |

|                     | Maximum Offset Adjustment            | +350  | +400          | +450  | mV   | Mode 111, D5=1          |

| $OFF\Delta$         | Offset Adjustment Step Size          |       | 3.14          |       | mV   |                         |

|                     |                                      |       |               |       |      |                         |

**Note 1:** The additional ±100 mV of adjustment with respect to the black level input range is needed to compensate for any additional offset introduced by the XRD9824 Buffer/PGA internally.

Note 2: It is not recommended to operate the part between 3.6V and 4.4V.

#### **ELECTRICAL CHARACTERISTICS (CONT'D)**

Test Conditions:  $AV_{DD} = DV_{DD} = 5V$ , ADCCLK=6MHz, 50% Duty Cycle,  $T_A = 25^{\circ}C$  unless otherwise specified.

| Symbol                              | Parameter                      | Min.                    | Тур.            | Max.                                      | Unit | Conditions                                                                                                  |

|-------------------------------------|--------------------------------|-------------------------|-----------------|-------------------------------------------|------|-------------------------------------------------------------------------------------------------------------|

| Buffer Speci                        | fications                      |                         |                 |                                           |      |                                                                                                             |

| I <sub>L</sub>                      | Input Leakage Current          |                         |                 | 100                                       | nA   |                                                                                                             |

| CIN                                 | Input Capacitance              |                         | 10              |                                           | pF   |                                                                                                             |

| VIN <sub>pp</sub>                   | AC Input Voltage Range         | 0                       |                 | AV <sub>DD</sub> -1.4                     | V    | CIS AC; INT V <sub>DCREF</sub><br>Config Reg<br>=> XXX010XX<br>Gain=1 (Note 1)                              |

|                                     | AC Input Voltage Range         | 0                       |                 | $DV_{REF}$                                | V    | CCD AC; INT V <sub>DCREF</sub><br>Config Reg<br>=> XXX011XX<br>Gain=1 (Note 1)                              |

| VIN                                 | DC Input Voltage Range         | -0.1                    |                 | AV <sub>DD</sub> -1.4                     | V    | CIS DC; INT V <sub>DCREF</sub><br>Config Reg<br>=> XXX000XX<br>Gain=1 (Note 2)                              |

|                                     | DC Input Voltage Range         | V <sub>DCEXT</sub> -0.1 |                 | V <sub>DCEXT</sub> +<br>DV <sub>REF</sub> | V    | CIS DC; EXT $V_{DCREF}$<br>Config Reg<br>=> XXX100XX<br>Gain=1 (Note 3)<br>$V_{DCEXT}+DV_{REF} \le AV_{DD}$ |

| V <sub>DCEXT</sub><br>Pin 16=Input  | External DC Reference          | 0.3                     |                 | AV <sub>DD</sub> /2                       | V    | CIS DC; EXT V <sub>DCREF</sub><br>Config Reg Mode 110<br>=> XXX100XX                                        |

| V <sub>DCEXT</sub><br>Pin 16=Output | Internal DC Reference          | 1.17                    |                 | 1.34                                      | V    | Internal CIS Reference<br>Circuit<br>Config Reg Mode 111<br>=> XXX1XXXX                                     |

| VIN <sub>BW</sub>                   | Input Bandwidth (Small Signal) |                         | 10              |                                           | MHz  |                                                                                                             |

| VIN <sub>CT</sub>                   | Channel to Channel Crosstalk   |                         | -60             | -50                                       | dB   | f <sub>in</sub> =3MHz                                                                                       |

| -                                   | mp Specifications              |                         |                 |                                           |      |                                                                                                             |

| V <sub>CLAMP</sub>                  | Clamp Voltage                  |                         | AGND            | 50                                        | mV   | CIS (AC) Config                                                                                             |

|                                     |                                | 3.5                     | V <sub>rt</sub> |                                           | V    | CCD (AC) Config                                                                                             |

| R <sub>INT</sub>                    | Clamp Switch On Resistance     |                         | 100             | 150                                       | Ω    |                                                                                                             |

|                                     | Clamp Switch Off Resistance    | 10                      |                 | Ι Τ                                       | MΩ   |                                                                                                             |

**Note 1:** VIN<sub>PP</sub> is the signal swing before the external capacitor tied to the MUX inputs.

**Note 2:** The -0.1V minimum is specified in order to accommodate black level signals lower than the external DC reference (clamp) voltage.

Rev. 2.00

**Note 3:** The V<sub>DCEXT</sub>-0.1V minimum is specified in order to accommodate black level signals lowerthan the external DC reference voltage.

#### **ELECTRICAL CHARACTERISTICS (CONT'D)**

Test Conditions:  $AV_{DD} = DV_{DD} = 5V$ , ADCCLK=6MHz, 50% Duty Cycle,  $T_A = 25^{\circ}C$  unless otherwise specified.

| Symbol            | Parameter                                               | Min.                  | Тур. | Max. | Unit              | Conditions                                                 |

|-------------------|---------------------------------------------------------|-----------------------|------|------|-------------------|------------------------------------------------------------|

| System Spe        | System Specifications (MUX + Buffer + PGA + ADC) Note 1 |                       |      |      |                   |                                                            |

| SYS               | System DNL                                              | -1.0                  | ±0.5 | +2.3 | LSB               |                                                            |

| SYS               | System Linearity                                        |                       | ±6.0 |      | LSB               |                                                            |

| SYS <sub>GE</sub> | System Gain Error                                       | -5.0                  |      | +5.0 | %                 |                                                            |

| IRN               | Input Referred Noise                                    |                       | 1.5  |      | mV <sub>rms</sub> | Gain=1                                                     |

|                   | Input Referred Noise                                    |                       | 0.5  |      | mV <sub>rms</sub> | Gain=10                                                    |

| System Timi       | ng Specifications                                       |                       |      |      | •                 | 1                                                          |

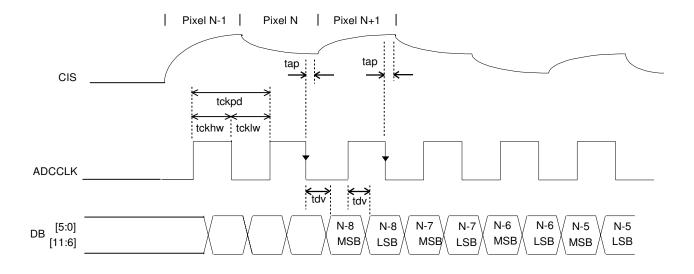

| tcklw             | ADCCLK Low Pulse Width                                  | 50                    | 83   |      | ns                |                                                            |

| tckhw             | ADCCLK High Pulse Width                                 | 70                    | 83   |      | ns                |                                                            |

| tckpd             | ADCCLK Period                                           | 120                   | 166  |      | ns                |                                                            |

| tsypw             | SYNCH Pulse Width                                       | 30                    |      |      | ns                |                                                            |

| trars             | Rising ADCCLK to rising<br>SYNCH                        | 0                     |      |      |                   | SYNCH must rise equal to<br>or after ADCCLK, See Figure 18 |

| tclpw             | CLAMP Pulse Width                                       | 30                    |      |      | ns                | Note 2                                                     |

| Write Timing      | Specifications                                          |                       |      |      |                   |                                                            |

| tsclkw            | SCLK Pulse Width                                        | 40                    |      |      | ns                |                                                            |

| tdz               | LD Low to SCLK High                                     | 20                    |      |      | ns                |                                                            |

| tds               | Input Data Set-up Time                                  | 20                    |      |      | ns                |                                                            |

| tdh               | Input Data Hold Time                                    | 0                     |      |      | ns                |                                                            |

| tdl               | SCLK High to LD High                                    | 50                    |      |      | ns                |                                                            |

| ADC Digital       | Output Specifications                                   |                       |      |      |                   |                                                            |

| tap               | Aperture Delay                                          |                       | 10   |      | ns                |                                                            |

| tdv               | Output Data Valid                                       | 40                    |      |      | ns                |                                                            |

| tsa               | SYNCH to ADCCLK                                         | 15                    |      |      | ns                | 3ch Pixel Md                                               |

| tlat              | Latency                                                 |                       | 8    |      | cycles            | Config 00, 11                                              |

| tlat              | Latency                                                 |                       | 6    |      | pixels            | Config 01, 10                                              |

| Digital Input     | Specifications                                          |                       |      |      |                   |                                                            |

| V <sub>IH</sub>   | Input High Voltage                                      | AV <sub>DD</sub> -2.5 |      |      | V                 |                                                            |

| V                 | Input Low Voltage                                       |                       |      | 1    | V                 |                                                            |

| I <sub>IH</sub>   | High Voltage Input Current                              |                       | 5    |      | μA                |                                                            |

| I <sub>L</sub>    | Low Voltage Input Current                               |                       | 5    |      | μA                |                                                            |

| C <sub>IN</sub>   | Input Capacitance                                       |                       | 10   |      | pF                |                                                            |

Note 1: System performance is specified for typical digital system timing specifications.

**Note 2:** The actual minimum 'tclpw' is dependent on the external capacitor value, the CIS output impedance. During 'clamp' operation, sufficient time needs to be allowed for the external capacitor to charge up to the correct operating level. Refer to the description in Theory of Operation, CIS Config.

Rev. 2.00

#### **ELECTRICAL CHARACTERISTICS (CONT'D)**

Test Conditions:  $AV_{DD}=DV_{DD}=5V$ , ADCCLK=6MHz, 50% Duty Cycle,  $T_A=25^{\circ}C$  unless otherwise specified.

| Symbol           | Parameter                                          | Min. | Тур. | Max. | Unit | Conditions               |

|------------------|----------------------------------------------------|------|------|------|------|--------------------------|

| Digital Output   | t Specifications                                   |      |      |      |      |                          |

| V <sub>OH</sub>  | Output High Voltage                                | 80   |      |      | (%)  |                          |

|                  | I <sub>L</sub> =1mA                                |      |      |      |      |                          |

| V <sub>ol</sub>  | Output Low Voltage                                 |      |      | 20   | (%)  |                          |

| $DV_{DD}$        | I_=-1mA                                            |      |      |      |      |                          |

| I <sub>oz</sub>  | Output High-Z Leakage Current                      | -10  |      | 10   | μA   |                          |

| C <sub>OUT</sub> | Output Capacitance                                 |      | 10   |      | pF   |                          |

| SR               | Slew Rate (10% to 90% $\mathrm{DV}_{\mathrm{DD}})$ | 2    |      | 15   | ns   | $C_L=10pF, DV_{DD}=3.3V$ |

#### THEORY OF OPERATION

#### CIS Configuration (Contact Image Sensor)

The XRD9824 has two configurations for CIS applications. Each configuration is set by the control registers accessed through the serial port.

#### Mode 1. DC Coupled

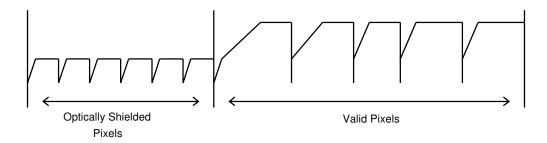

If the CIS does not have leading or trailing black pixels as shown in Figure 2, then DC couple the CIS output to the XRD9824 input.

Figure 2. Typical Output CIS Mode

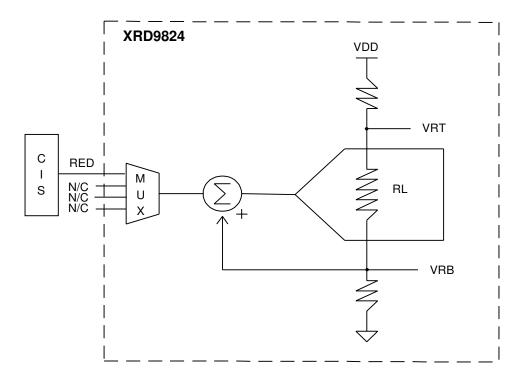

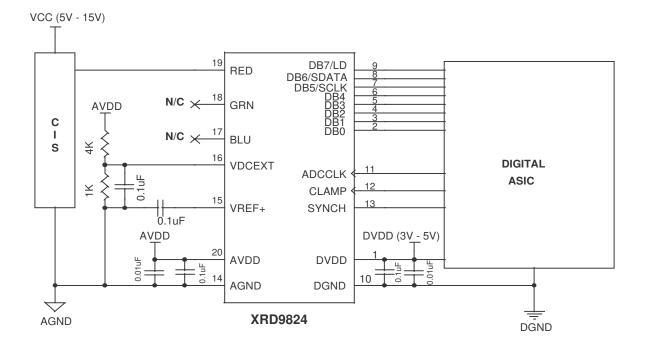

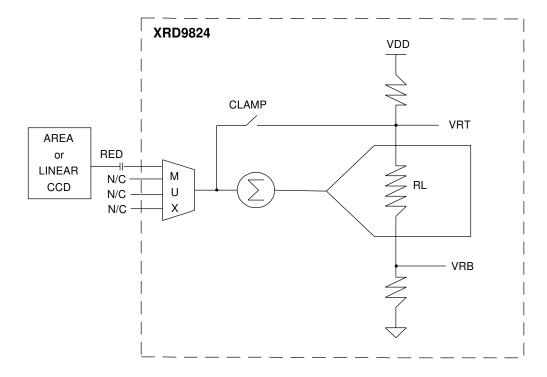

Adjust the offset of the CIS (-100 mV to 500 mV) by setting the internal registers of the XRD9824 to set the black pixel value when the LEDs of the CIS are off. When the LEDs are on, use the XRD9824 Programmable Gain to maximize the ADCs dynamic range. Figure 3 shows a typical application for a CIS with an offset of -100mV to 500mV.

Figure 3. Application with Offset in the Range (-100mv to 500mv)

The input is added to VRB before the signal passes through the ADC. If the CIS output is zero, then the output of the ADC will be zero code. This enables the CIS to be referenced to the bottom ladder reference voltage to use the full range of the ADC.

Some CIS sensors have an output with an offset voltage of greater than 500mV. If the CIS output is

beyond the offset range of the XRD9824 (see Offset Control DAC, Pg. 28) set the internal mode registers to external reference. An external reference voltage equal to the value of the CIS offset voltage can be applied to VDCEXT (Figure 4) in order to meet the dynamic range of the XRD9824. Figure 4 is a diagram of the XRD9824 in the external reference mode for CIS, DC coupled applications.

Figure 4. Application with Offset Greater Than (-100mv to 500mv)

The DC reference voltage applied to VDCEXT does not have to be accurate. The internal offset DAC voltage is still used in this mode for fine adjustment. VDCEXT cannot be used as an input from the CIS. Any signal applied to VDCEXT will be subtracted from the output signal of the multiplexer.

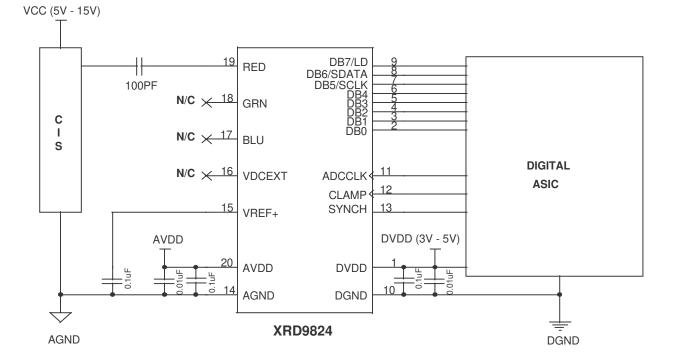

Figure 5. Typical Application Circuitry CIS DC Coupled Non-Inverted Mode

#### CIS Mode Timing -- DC Coupled (CLAMP disabled)

Figure 6. Timing Diagram for Figure 5

| ADCCLK       | Events                                     |

|--------------|--------------------------------------------|

| $\downarrow$ | ADC Sample & PGA Start Tracking next Pixel |

|              | MSB Data Out                               |

| ↑            | LSB Data Out                               |

| HI           | ADC Track PGA Output                       |

| LO           | ADC Hold/Convert                           |

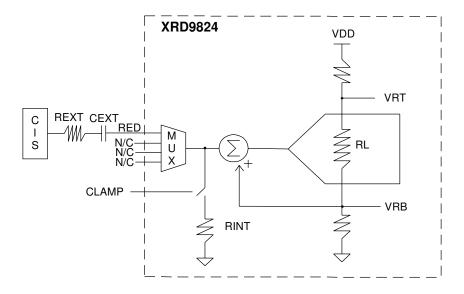

#### Mode 2. AC Coupled

If the CIS signal has a black reference for the video signal, an external capacitor  $\rm C_{\rm EXT}$  is used. When CLAMP (clamp) pin is set high an internal switch allows

one side of the external capacitor to be set to ground. It then is level shifted to correspond to the bottom ladder reference voltage of the ADC (Figure 7).

Rev. 2.00

Figure 7. CIS AC Coupled Application

This value corresponds to the black reference of the image sensor. When the CLAMP pin is set back to low, the ADC samples the video signal with respect to the black reference. The typical value for the external capacitor is 100pF. This value should be adjusted according to the time constant (Tc) needed in a particular application. The CLAMP pin has an internal 150 ohm impedance (R<sub>INT</sub>) which is in series with the external capacitor (C<sub>EXT</sub>).

Therefore,  $Tc = 1/R_{INT}C_{EXT}$

If the input to the external capacitor has a source impedance ( $\rm R_{\rm EXT}$ ), then:

$$T_c = 1/(R_{INT} + R_{EXT})C_{EXT}$$

**XPEXAR**

Figure 8. Typical Application Circuitry CIS AC Coupled Non-Inverted

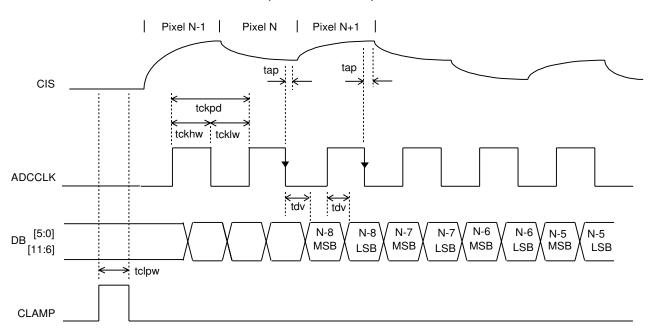

#### CIS Mode Timing -- AC Coupled (CLAMP enabled)

#### Figure 9. Timing Diagram for Figure 8

| ADCCLK       | Events                                     |

|--------------|--------------------------------------------|

| $\downarrow$ | ADC Sample & PGA Start Track of next Pixel |

|              | MSB Data Out                               |

| $\uparrow$   | LSB Data Out                               |

| HI           | ADC Track PGA Output                       |

| LO           | ADC Hold/Convert                           |

#### Table 3.

| CLAMP | Events                                                                                             |

|-------|----------------------------------------------------------------------------------------------------|

| HI    | PGA Tracks V <sub>CLAMP</sub> & C <sub>EXT</sub> is Charged to                                     |

| LO    | $V_{_{BLACK}}$ - $V_{_{CLAMP}}$ , which is equal to $V_{_{BLACK}}$ PGA Tracks $\text{VIN}_{_{PP}}$ |

Table 4.

Rev. 2.00

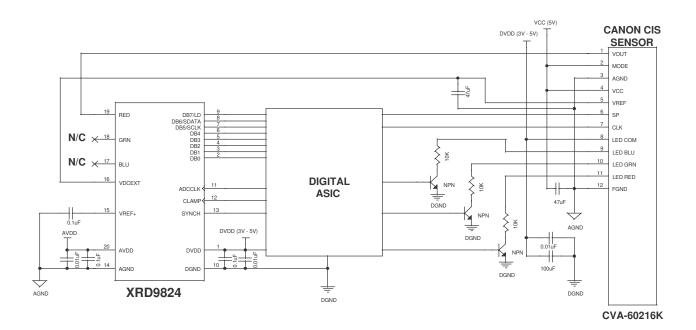

#### Internal CIS Reference Circuit (DB 4 = 1)

The XRD9824 has an internal register reserved for interfacing to the Canon CIS model number CVA-60216K. When this register is selected, the VDCEXT (Pin 16) becomes an output voltage of 1.24 volts. This voltage can be directly connected to the VREF (Pin 15) of the Canon sensor. This reduces the amount of

components needed for biasing the Canon CIS sensor (the external diodes and resistors typically used in this application have been included inside the XRD9824 for this mode of operation). Below is a typical application circuit using the XRD9824 and the Canon CVA-60216K CIS sensor.

Figure 10. Typical Application Circuitry Internal CIS Reference Circuit Mode CANON CIS Sensor, Model #CVA=60216k

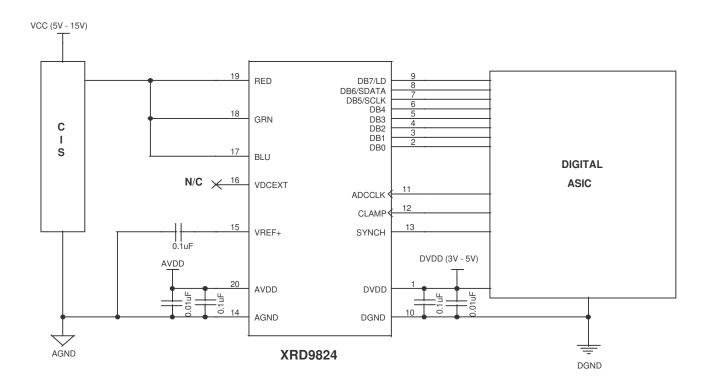

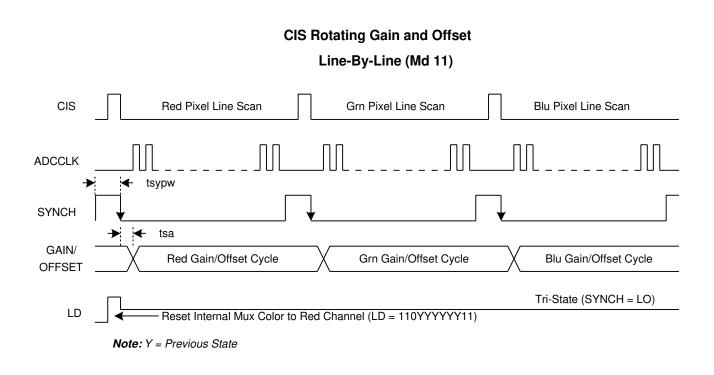

#### CIS Line-By-Line Rotating Gain and Offset (Configuration DB1 = 1, DB0 = 1)

Line-by-line rotating gain and offset minimizes the amount of write cycles per scan. Pre-loaded values of gain and offset can be loaded for each color before the first line is scanned. Each gain and offset is cycled through line-by-line so that the gain and offset do not have to be loaded in between lines. Below is the typical application circuit and timing for this configuration.

Figure 11. Typical Application Circuitry Internal CIS Rotating Gain and Offset Line-By-Line

Figure 12. Timing Diagram for Figure 11

#### **CCD Configuration (Charge Coupled Device)**

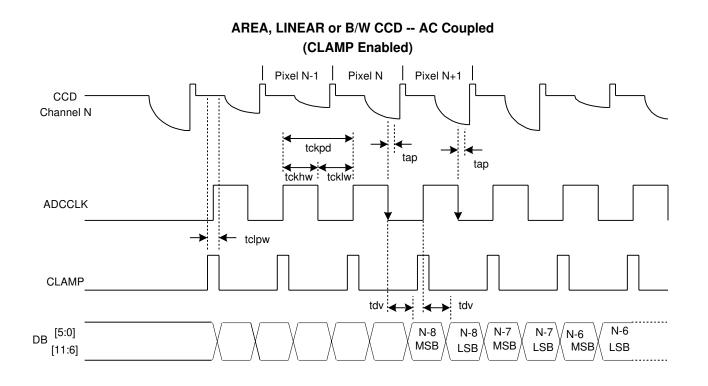

#### Mode 1. AC Coupled

In the CCD configuration of operation, an external capacitor needs to be chosen according to the equations below. The typical value for the external capacitor is 100pF. This value should be adjusted according to the time constant (Tc) needed in a particular application. The CLAMP pin has an internal 150 ohm impedance ( $R_{INT}$ ) which is in series with the external capacitor ( $C_{EXT}$ ).

Therefore,  $Tc = 1/R_{INT}C_{EXT}$

If the input to the external capacitor has a load impedance ( $R_{_{\rm FXT}}$ ), then

When CLAMP (clamp) pin is set high an internal switch allows one side of the external capacitor to be set to VRT (Figure 13). This value corresponds to the black reference of the CCD. When the CLAMP pin is set back to low, the ADC samples the video signal with respect to the black reference. The difference between the black reference and the video signal is the actual pixel value of the video content. Since this value is referenced to the top ladder reference voltage of the ADC a zero input signal would yield a full scale output code. Therefore, the output of the conversion is inverted (internally) to correspond to zero scale output code.

T<sub>c</sub>=1/(R<sub>INT</sub>+R<sub>EXT</sub>)C<sub>EXT</sub> *Rev. 2.00*

#### Figure 13. CCD AC Coupled Application

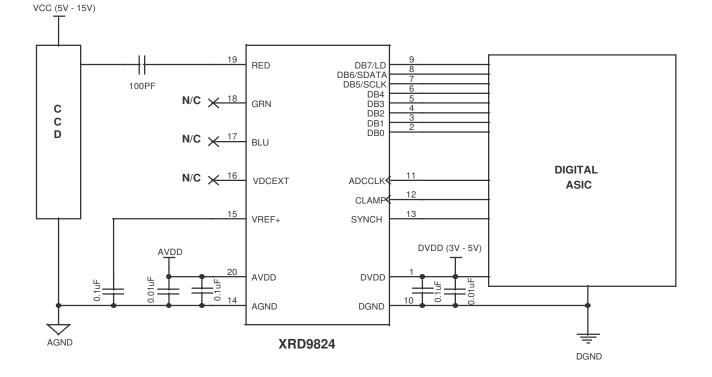

#### Area or Linear CCD Applications

Figure 13 is a block diagram for applications with Area or Linear CCDs (The timing for Area CCDs and B/W CCDs is the same). For Area or Linear CCD applications, a global offset is loaded into the serial port at the beginning of a line. The gain is set to adjust for the highest color intensity of the CCD output. Once the

pixel values have been sampled, the gain and offset are adjusted at the beginning of the next line. For example, if there is a line-to-line variation between the black reference pixels, the offset is adjusted. The gain is always adjusted for the highest color intensity.

Figure 14. Typical Application Circuitry Single Channel CCD AC Coupled Inverted Mode

Figure 15. Timing Diagram for Figure 14

#### **Triple Channel CCD Application**

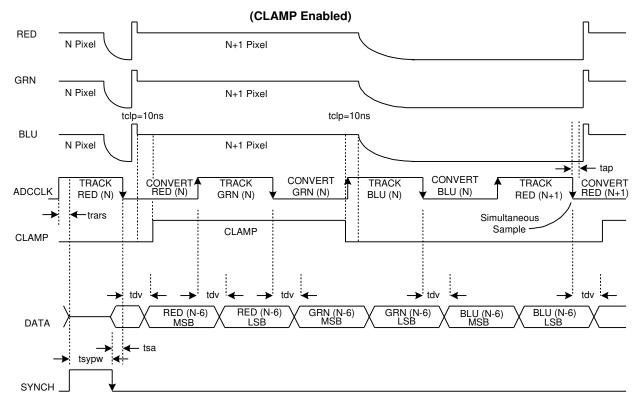

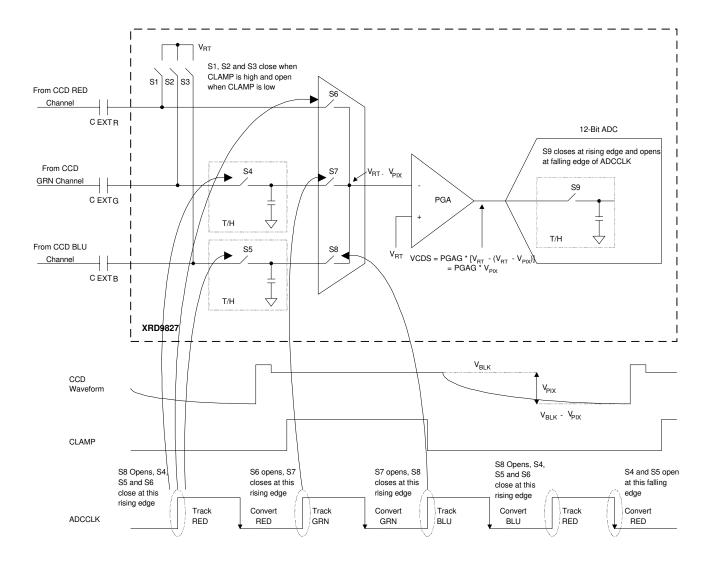

Figure 16, is a block diagram for pixel-by-pixel applications with triple channel CCDs. During the optically shielded section of a pixel, CLAMP must go high to store the black reference on each capacitor to the input. The gain and offset is automatically rotated to adjust for each channel input. The MSBs are available on the output bus on the falling edge of ADCCLK. The LSBs are available on the rising edge of ADCCLK.

Figure 16. CCD AC Coupled Application

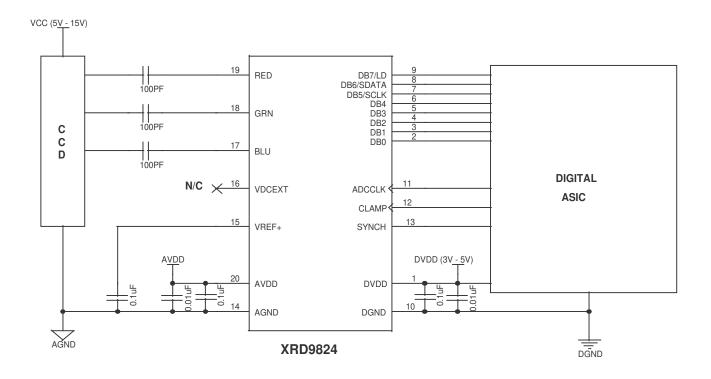

Figure 17. Typical Application Circuitry Triple Channel CCD AC Coupled Inverted Mode

#### PIXEL-BY-PIXEL 3 CHANNEL CCD -- AC Coupled

Figure 18. Timing Diagram for Figure 17

| ADCCLK | Events                                              |

|--------|-----------------------------------------------------|

| 3rd ↓  | Simultaneous RED/GRN/BLU Sample Every 3rd CLK.      |

|        | Convert RED, S/H GRN, S/H BLU.                      |

| All ↓  | MSB Data Out                                        |

| ↑ (    | LSB Data Out                                        |

| HI     | ADC Track PGA Output                                |

| LO     | ADC Hold/Convert                                    |

| CLAMP  | Events                                              |

| HI     | Internal Clamp Enabled                              |

| LO     | Internal RED/GRN/BLU Tracking Enabled               |

| SYNCH  | Events                                              |

| HI     | Reset Internal Mux to Red, Output Bus is Tri-stated |

| LO     | Increment Mux Color on Falling Edge of ADCCLK       |

Table 5.

#### Rev. 2.00

Figure 19. CDS Timing (Triple Channel) Mode: 110 00001110