Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

#### Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

October 2012 Rev. 1.0.1

#### **GENERAL DESCRIPTION**

The XRP7724 is a quad channel Digital Pulse Width Modulated (DPWM) Step down (buck) controller. A wide 4.75V to 5.5V and 5.5V to 25V input voltage dual range allows for single supply operation from standard power rails.

With integrated FET gate drivers, two LDOs for standby power and a 105kHz to 1.23MHz independent channel to channel programmable constant operating frequency, the XRP7724 reduces overall component count and solution footprint and optimizes conversion efficiencies. A selectable digital Pulse Frequency Mode (DPFM) capable of better than 80% efficiency at light current load and low operating current allow for portable and Energy Star compliant applications. Each XRP7724 output channel is individually programmable as low as 0.6V with resolution as fine as 2.5mV, configurable for precise soft start and soft stop sequencing, including delay and ramp control.

The XRP7724 operations are fully controlled via a SMBus-compliant  $I^2C$  interface allowing for advanced local and/or remote reconfiguration, full performance monitoring and reporting as well as fault handling.

Built-in independent output over voltage, over temperature, over-current and under voltage lockout protections insure safe operation under abnormal operating conditions.

The XRP7724 is offered in a RoHS compliant, "green"/halogen free 44-pin TQFN package.

#### **APPLICATIONS**

- Servers

- Base Stations

- Switches/Routers

- Broadcast Equipment

- Industrial Control Systems

- Automatic Test Equipment

- Video Surveillance Systems

#### **FEATURES**

#### Quad Channel Step-down Controller

- Digital PWM 105kHz-1.23MHz Operations

- Individual Channel Frequency Selection

- Patented digital PFM with Ultrasonic mode

- Patented Over Sampling Feedback

- Integrated MOSFET Drivers

- Programmable 5 coefficient PID control

#### 4.75V to 25V Input Voltage

- 4.75V-5.5 and 5.5V-25V Input Ranges

- 0.6V to 5.5V Output voltage

#### • SMBus Compliant - I<sup>2</sup>C Interface

- Full Power Monitoring and Reporting

- 3 x 15V Capable PSIO + 2 x GPIOs

- Full Start/Stop Sequencing Support

- Built-in Thermal, Over-Current, UVLO and Output Over-Voltage Protections

- On Board 5V and 3.3V Standby LDOs

- On Board Non-volatile Memory

- Supported by PowerArchitect™

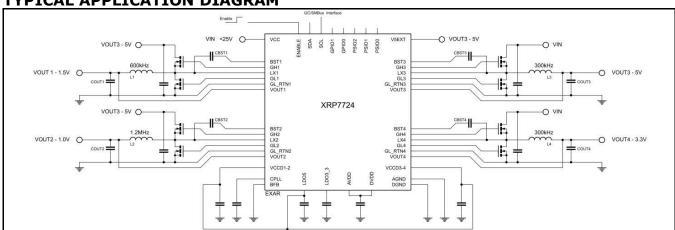

#### TYPICAL APPLICATION DIAGRAM

Fig. 1: XRP7724 Application Diagram

#### **ABSOLUTE MAXIMUM RATINGS**

#### These are stress ratings only and functional operation of the device at these ratings or any other above those indicated in the operation sections of the specifications below is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

| VCCD, LDO5, LDO3_3, GLx, VOUTx       | 0.3V to 7.0V         |

|--------------------------------------|----------------------|

| ENABLE, 5V_EXT                       | 0.3V to 7.0V         |

| GPIO0/1, SCL, SDA                    | 6.0V                 |

| PSIOs Inputs, BFB                    | 18V                  |

| DVDD, AVDD                           | 2.0V                 |

| VCC                                  | 28V                  |

| LX#                                  | 1V to 28V            |

| BSTx, GHx                            | VLXx + 6V            |

| Storage Temperature                  | 65°C to 150°C        |

| Power Dissipation                    | . Internally Limited |

| Lead Temperature (Soldering, 10 sec) | 300°C                |

| ESD Rating (HBM - Human Body Model)  | 2kV                  |

|                                      |                      |

#### **OPERATING RATINGS**

| Input Voltage Range V <sub>CC</sub>       | 5.5V to 25V   |

|-------------------------------------------|---------------|

| Input Voltage Range $V_{CC} = LDO5 \dots$ | 4.75V to 5.5V |

| VOUT1, 2, 3, 4                            | 5.5V          |

| Junction Temperature Range                | 40°C to 125°C |

| JEDEC Thermal Resistance θ <sub>JA</sub>  | 30.2°C/W      |

#### **ELECTRICAL SPECIFICATIONS**

Specifications with standard type are for an Operating Junction Temperature of  $T_1 = 25^{\circ}\text{C}$  only; limits applying over the full Operating Junction Temperature range are denoted by a "•". Minimum and Maximum limits are guaranteed through test, design, or statistical correlation. Typical values represent the most likely parametric norm at  $T_1 = 25^{\circ}\text{C}$ , and are provided for reference purposes only. Unless otherwise indicated,  $V_{CC} = 5.5V$  to 25V, 5V EXT open. Note that in cases where there is a discrepancy in values shown in this section and other sections of the datasheet, the values in the Electrical Specification section shall be deemed correct and supersede the other values.

#### **QUIESCENT CURRENT**

| Parameter                      | Min. | Тур. | Max. | Units | Conditions                                                                                                                     |

|--------------------------------|------|------|------|-------|--------------------------------------------------------------------------------------------------------------------------------|

| VCC Supply Current in SHUTDOWN |      | 10   | 20   | μA    | EN = 0V, VCC = 12V                                                                                                             |

| ENABLE Turn On Threshold       | 0.82 |      | 0.95 | V     | VCC = 12V Enable Rising                                                                                                        |

| ENABLE Pin Leakage Current     |      |      | 10   | uA    | EN=5V                                                                                                                          |

| ENABLE FIII Leakage Current    | -10  |      |      |       | EN=0V                                                                                                                          |

| VCC Supply Current in STANDBY  |      | 440  | 600  | μА    | LDO3_3 disabled, all channels disabled<br>GPIOs programmed as inputs<br>VCC=12V,EN = 5V                                        |

| VCC Supply Current 2ch PFM     |      | 3.1  |      | mA    | 2 channels on set at 5V, VOUT forced to 5.1V, no load, non-switching, Ultra-sonic off, VCC=12 V, No I <sup>2</sup> C activity. |

| VCC Supply Current 4ch PFM     |      | 4.0  |      | mA    | 4 channels on set at 5V, VOUT forced to 5.1V, no load, non-switching, Ultra-sonic off, VCC=12V, No $\rm I^2C$ activity.        |

| VCC Supply Current ON          |      | 18   |      | mA    | All channels enabled, Fsw=600kHz, gate drivers unloaded, No I <sup>2</sup> C activity.                                         |

#### INPUT VOLTAGE RANGE AND UNDERVOLTAGE LOCKOUT

| Parameter | Min. | Тур. | Max. | Units |   | Conditions                 |

|-----------|------|------|------|-------|---|----------------------------|

| VCC Range | 5.5  |      | 25   | V     | • |                            |

| VCC Range | 4.75 |      | 5.5  | V     | • | With VCC connected to LDO5 |

#### **VOLTAGE FEEDBACK ACCURACY AND OUTPUT VOLTAGE SET POINT RESOLUTION**

| Parameter                                              | Min.                 | Тур.             | Max.                | Units |   | Conditions                                             |

|--------------------------------------------------------|----------------------|------------------|---------------------|-------|---|--------------------------------------------------------|

| VOUT Regulation Accuracy                               | -5                   |                  | 5                   | mV    |   | 0.6 ≤ VOUT ≤ 1.6V                                      |

| Low Output Range                                       | -20                  |                  | 20                  | mV    | • | 70.6 \( \text{VOU1} \) \( \text{1.6V} \)               |

| 0.6V to 1.6V                                           | -7.5                 |                  | 7.5                 | mV    |   | 0.6 ≤ VOUT ≤ 1.6V                                      |

| PWM Operation                                          | -22.5                |                  | 22.5                | mV    | • | VCC=LDO5                                               |

| VOUT Regulation Accuracy                               | -15                  |                  | 15                  | mV    |   | -0.6 ≤ VOUT ≤ 3.2V                                     |

| Mid Output Range                                       | -45                  |                  | 45                  | mV    | • | 0.0 \( \text{VOO1} \( \text{S} \) 3.2\( \text{V}       |

| 0.6V to 3.2V                                           | -20                  |                  | 20                  | mV    |   | 0.6 ≤ VOUT ≤ 3.2V                                      |

| PWM Operation                                          | -50                  |                  | 50                  | mV    | • | VCC=LDO5                                               |

| VOUT Regulation Accuracy                               | -30                  |                  | 30                  | mV    |   | -0.6 ≤ VOUT ≤ 5.5V                                     |

| High Output Range                                      | -90                  |                  | 90                  | mV    | • | 0.0 \( \text{VOO1} \( \text{S} \) 3.3\( \text{VOO1} \) |

| 0.6V to 5.5V                                           | -40                  |                  | 40                  | mV    |   | 0.6 ≤ VOUT ≤ 4.2V                                      |

| PWM Operation                                          | -100                 |                  | 100                 | mV    | • | VCC=LDO5                                               |

| VOUT Regulation Range                                  | 0.6                  |                  | 5.5                 | V     | • | Without external divider network                       |

| VOUT Native Set Point<br>Resolution                    |                      | 12.5<br>25<br>50 |                     | mV    |   | Low Range<br>Mid Range<br>High Range                   |

| VOUT Fine Set Point Resolution <sup>1</sup>            |                      | 2.5<br>5<br>10   |                     | mV    |   | Low Range<br>Mid Range<br>High Range                   |

| VOUT Input Resistance                                  |                      | 120<br>90<br>75  |                     | kΩ    |   | Low Range<br>Mid Range<br>High Range                   |

| VOUT Input Resistance in PFM<br>Operation              |                      | 10<br>1<br>0.67  |                     | MΩ    |   | Low Range<br>Mid Range<br>High Range                   |

| Power Good and OVP Set Point<br>Range (from set point) | -155<br>-310<br>-620 |                  | 157.5<br>315<br>630 | mV    |   | Low Range<br>Mid Range<br>High Range                   |

| Power Good and OVP Set Point<br>Accuracy               | -5<br>-10<br>-20     |                  | 5<br>10<br>20       | mV    |   | Low Range<br>Mid Range<br>High Range                   |

| BFB Set Point Range                                    | 9                    | _                | 16                  | V     |   |                                                        |

| BFB Set Point Resolution                               |                      | 1                |                     | V     |   |                                                        |

| BFB Accuracy                                           | -0.5                 |                  | 0.5                 | V     |   |                                                        |

Note 1: Fine Set Point Resolution not available in PFM

#### **CURRENT AND AUX ADC (MONITORING ADCS)**

| Parameter                                      | Min.  | Тур.           | Max.  | Units |   | Conditions                           |

|------------------------------------------------|-------|----------------|-------|-------|---|--------------------------------------|

|                                                | -3.75 | ±1.25          | 3.75  | mV    |   | Low Range (≤120mV) Note 2            |

| Current Sense Accuracy                         | -10   |                | 10    | mV    | • | -60mV applied                        |

| Current Sense Accuracy                         | -5    | ±2.5           | 5     | mV    |   | High Range (≤280mV)                  |

|                                                | -12.5 |                | +12.5 | mV    | • | -150mV                               |

| Current Sense ADC INL                          |       | +/-0.4         |       | LSB   |   |                                      |

| DNL                                            |       | 0.27           |       |       |   |                                      |

| Current Limit Set Point                        |       | 1.25           |       | mV    |   | Low Range (≤120mV)                   |

| Resolution and Current<br>Sense ADC Resolution |       | 2.5            |       | mV    |   | High Range (≤280mV)                  |

| Current Conce ADC Bange                        | -120  |                | 20    | mV    |   | Low Range (≤120mV)                   |

| Current Sense ADC Range                        | -280  |                | 40    |       |   | High Range (≤280mV)                  |

| VOUT ADC Resolution                            |       | 15<br>30<br>60 |       | mV    |   | Low Range<br>Mid Range<br>High Range |

| VOUT ADC Accuracy                              | -1    |                | 1     | LSB   |   |                                      |

| VCC ADC Range                                  | 4.6   |                | 25    | V     |   | Note 3                               |

| UVLO WARN SET                                  | 4.4   |                | 4.72  | V     |   | UVLO WARN set point 4.6V, VCC=LDO5   |

| UVLO WARN CLEAR                                | 4.4   |                | 4.72  | V     |   | UVLO WARN set point 4.6V, VCC=LDO5   |

| UVLO FAULT SET (Note 4)                        | 4.2   |                | 4.55  | V     |   | UVLO FAULT set point 4.4V, VCC=LDO5  |

| VCC ADC Resolution                             |       | 200            |       | mV    |   |                                      |

| VCC ADC Accuracy                               | -1    |                | 1     | LSB   |   | Vin <= 20V                           |

| Die Temp ADC Resolution                        |       | 5              |       | °C    |   |                                      |

| Die Temp ADC Range                             | -44   |                | 156   | °C    |   | Output value is in Kelvin            |

Note 2: Final test limits are  $\pm 2.5$ mV or  $\pm 2$  LSB

Note 3: Although Range of VCC ADC is technically 0V to 25V, below 4.55 the LDO5 hardware UVLO may have tripped. Note 4: This test ensures an UVLO FAULT flag will be given before the LDO5 hardware UVLO trips.

#### **LINEAR REGULATORS**

| Parameter                                           | Min. | Тур. | Max. | Units |   | Conditions                                                                            |

|-----------------------------------------------------|------|------|------|-------|---|---------------------------------------------------------------------------------------|

| LDO5 Output Voltage                                 | 4.85 | 5.0  | 5.15 | V     | • | $5.5V \le VCC \le 25V$<br>$0mA < I_{LDO50UT} < 130mA, LDO3_3 Off$                     |

|                                                     |      |      |      |       |   |                                                                                       |

| LDO5 Current Limit                                  | 135  | 155  | 180  | mA    | • | LDO5 Fault Set                                                                        |

| LDO5 UVLO                                           | 4.74 |      |      | V     | • | VCC Rising                                                                            |

| LDO5 PGOOD Hysteresis                               |      | 375  |      | mV    |   | VCC Falling                                                                           |

| LDO5 Bypass Switch Resistance                       |      | 1.1  | 1.5  | Ω     |   |                                                                                       |

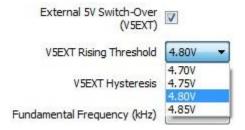

| Bypass Switch Activation<br>Threshold               | 2.5  |      | 2.5  | %     | • | V5EXT Rising, % of threshold setting                                                  |

| Bypass Switch Activation<br>Hysteresis              |      | 150  |      | mV    |   | V5EXT Falling                                                                         |

| LDO3_3 Output Voltage                               | 3.15 | 3.3  | 3.45 | V     | • | $4.6V \le LDO5 \le 5.5V$<br>$0mA < I_{LDO3\_3OUT} < 50mA$                             |

| LDO3_3 Current Limit                                | 53   |      | 85   | mA    | • | LDO3_3 Fault Set                                                                      |

| Maximum total LDO loading<br>during ENABLE start-up |      |      | 30   | mA    |   | ENABLE transition from logic low to high. Once LDO5 in regulation above limits apply. |

#### **PWM GENERATORS AND OSCILLATOR**

| Parameter                             | Min. | Тур. | Max. | Units | Conditions                                        |

|---------------------------------------|------|------|------|-------|---------------------------------------------------|

| Switching Frequency (fsw)<br>Range    | 105  |      | 1230 | kHz   | Steps defined in table                            |

| fsw Accuracy                          | -5   |      | 5    | %     |                                                   |

| CLOCK IN<br>Synchronization Frequency | 20   | 25.7 | 31   | MHz   | When synchronizing to an external clock (Range 1) |

| CLOCK IN<br>Synchronization Frequency | 10   | 12.8 | 15.5 | MHz   | When synchronizing to an external clock (Range 2) |

#### **GPIOs**<sup>5</sup>

| Parameter                                             | Min. | Тур. | Max. | Units | Conditions                |

|-------------------------------------------------------|------|------|------|-------|---------------------------|

| Input Pin Low Level                                   |      |      | 0.8  | V     |                           |

| Input Pin High Level                                  | 2.0  |      |      | V     |                           |

| Input Pin Leakage Current                             |      |      | 1    | μΑ    |                           |

| Output Pin Low Level                                  |      |      | 0.4  | V     | $I_{SINK} = 1mA$          |

| Output Pin High Level                                 | 2.4  |      |      | V     | I <sub>SOURCE</sub> = 1mA |

| Output Pin High Level                                 |      | 3.3  | 3.6  | V     | I <sub>SOURCE</sub> = 0mA |

| Output Pin High-Z leakage<br>Current (GPIO pins only) |      |      | 10   | μA    |                           |

| Maximum Sink Current                                  |      |      | 1    | mA    | Open Drain Mode           |

| I/O Frequency                                         |      |      | 30   | MHz   |                           |

Note 5: 3.3V CMOS logic compatible, 5V tolerant.

#### PSIOs<sup>6</sup>

| Parameter                                             | Min. | Тур. | Max. | Units | Conditions                                           |

|-------------------------------------------------------|------|------|------|-------|------------------------------------------------------|

| Input Pin Low Level                                   |      |      | 0.8  | V     |                                                      |

| Input Pin High Level                                  | 2.0  |      |      | V     |                                                      |

| Input Pin Leakage Current                             |      |      | 1    | μΑ    |                                                      |

| Output Pin Low Level                                  |      |      | 0.4  | V     | $I_{SINK} = 3mA$                                     |

| Output Pin High Level                                 |      |      | 15   | V     | Open Drain. External pull-up resistor to user supply |

| Output Pin High-Z leakage<br>Current (PSIO pins only) |      |      | 10   | μΑ    |                                                      |

| I/O Frequency                                         |      |      | 5    | MHz   |                                                      |

Note 6: 3.3V/5.0V CMOS logic compatible, maximum rating of 15.0V

#### **SMBUS (I2C) INTERFACE**

| Parameter                                                       | Min.           | Тур. | Max.    | Units | Conditions                                      |

|-----------------------------------------------------------------|----------------|------|---------|-------|-------------------------------------------------|

| Input Pin Low Level, $V_{\text{IL}}$                            |                |      | 0.3 VIO | V     | VIO = 3.3 V ±10%                                |

| Input Pin High Level, $V_{\text{IH}}$                           | 0.7 VIO        |      |         | V     | VIO = 3.3 V±10%                                 |

| Hysteresis of Schmitt Trigger inputs, V <sub>hys</sub>          | 0.05 VIO       |      |         | V     | VIO = 3.3 V±10%                                 |

| Output Pin Low Level (open drain or collector), V <sub>OL</sub> |                |      | 0.4     | V     | I <sub>SINK</sub> = 3mA                         |

| Input leakage current                                           | -10            |      | 10      | μΑ    | Input is between 0.1 VIO and 0.9 VIO            |

| Output fall time from $V_{\text{IHmin}}$ to $V_{\text{ILmax}}$  | 20 + 0.1<br>Cb |      | 250     | ns    | With a bus capacitance (Cb)from 10 pF to 400 pF |

| Internal Pin Capacitance                                        |                |      | 1       | pF    |                                                 |

#### **GATE DRIVERS**

| Parameter                                      | Min. | Тур. | Max. | Units | Conditions                                     |

|------------------------------------------------|------|------|------|-------|------------------------------------------------|

| GH, GL Rise Time                               |      | 17   |      | ns    | At 10 000/ of full cools 1pE C                 |

| GH, GL Fall Time                               |      | 11   |      | ns    | At 10-90% of full scale, 1nF C <sub>load</sub> |

|                                                |      |      |      |       |                                                |

| GH, GL Pull-Up On-State Output<br>Resistance   |      | 4    | 5    | Ω     |                                                |

| GH, GL Pull-Down On-State<br>Output Resistance |      | 2    | 2.5  | Ω     |                                                |

| GH, GL Pull-Down Resistance in Off-Mode        |      | 50   |      | kΩ    | VCC = VCCD = 0V.                               |

| Bootstrap diode forward resistance             |      | 9    |      | Ω     | @ 10mA                                         |

| Minimum On Time                                |      | 50   |      | ns    | 1nF of gate capacitance.                       |

| Minimum Off Time                               |      | 125  |      | ns    | 1nF of gate capacitance                        |

| Minimum Programmable Dead<br>Time              |      | 20   |      | ns    | Does not include dead time variation from      |

| Maximum Programmable Dead<br>Time              |      | Tsw  |      |       | driver output stage<br>Tsw=switching period    |

| Programmable Dead Time<br>Adjustment Step      | ·    | 607  |      | ps    |                                                |

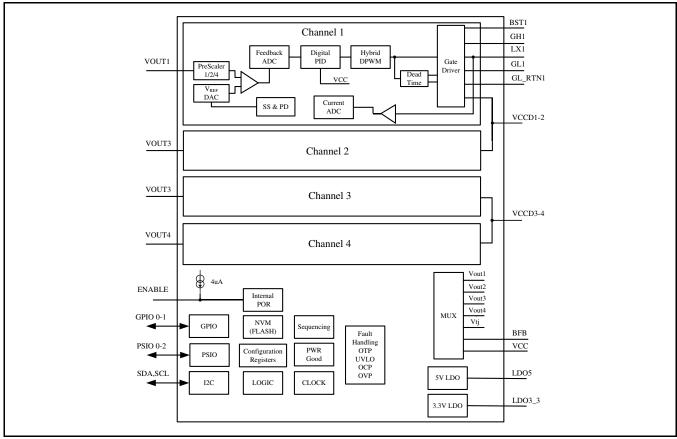

#### **BLOCK DIAGRAM**

Fig. 2: XRP7724 Block Diagram

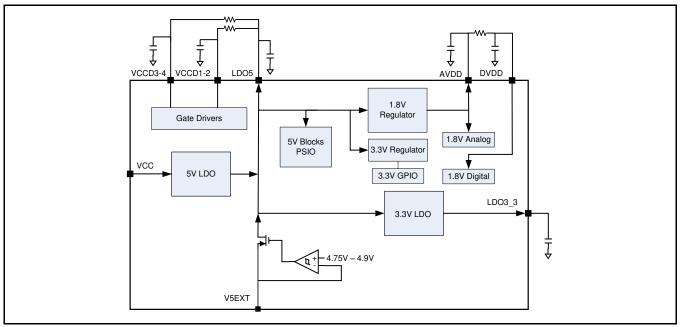

#### LDO BLOCK DIAGRAM

Fig. 3: XRP7724 LDO Block Diagram

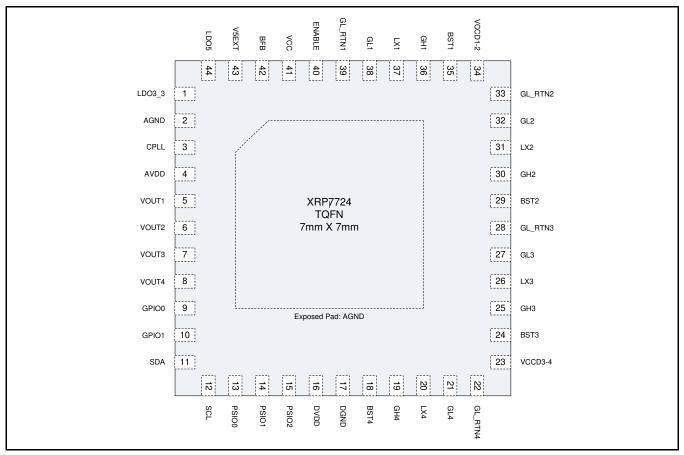

#### **PIN ASSIGNMENT**

Fig. 4: XRP7724 Pin Assignment

#### **PIN DESCRIPTION**

| Name               | Pin Number   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCC                | 41           | Input voltage. Place a decoupling capacitor close to the controller IC. This input is used in UVLO fault generation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| DVDD               | 16           | 1.8V supply input for digital circuitry. Connect pin to AVDD. Place a decoupling capacitor close to the controller IC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| VCCD1-2<br>VCCD3-4 | 23,34        | Gate Drive supply. Two independent gate drive supply pins where pin 34 supplies drivers 1 and 2 and pin 23 supplies drivers 3 & 5. One of the two pins must be connected to the LDO5 pin to enable two power rails initially. It is recommended that the other VCCD pin be connected to the output of a 5V switching rail(for improved efficiency or for driving larger external FETs), if available, otherwise this pin may also be connected to the LDO5 pin. A bypass capacitor (>1uF) to PAD is recommended for each VCCD pin with the pin(s) connected to LDO5 with shortest possible length of etch. |

| AGND               | 2            | Analog ground pin. This is the small signal ground connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| GL_RTN1-4          | 39,33, 28,22 | Ground connection for the low side gate driver. This should be routed as a signal trace with GL. Connect to the source of the low side MOSFET.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| GL1-GL4            | 38,32, 27,21 | Output pin of the low side gate driver. Connect directly to the gate of an external N-channel MOSFET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| GH1-GH4            | 36,30, 25,19 | Output pin of the high side gate driver. Connect directly to the gate of an external N-channel MOSFET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Name        | Pin Number   | Description                                                                                                                                                                                                                                                                                                                                  |

|-------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LX1-LX4     | 37,31, 26,20 | Lower supply rail for the GH high-side gate driver. Connect this pin to the switching node at the junction between the two external power MOSFETs and the inductor. These pins are also used to measure voltage drop across bottom MOSFETs in order to provide output current information to the control engine.                             |

| BST1-BST4   | 35,29, 24,18 | High side driver supply pin(s). Connect BST to the external capacitor as shown in the Typical Application Circuit on page 2. The high side driver is connected between the BST pin and LX pin and delivers the BST pin voltage to the high side FET gate each cycle.                                                                         |

| GPI0-GPIO1  | 9,10         | These pins can be configured as inputs or outputs to implement custom flags, power good signals, enable/disable controls and synchronization to an external clock.                                                                                                                                                                           |

| PSIO0-PSIO2 | 13,14,15     | Open drain, these pins can be used to control external power MOSFETs to switch loads on and off, shedding the load for fine grained power management. They can also be configures as standard logic outputs or inputs just as any of the GPIOs can be configured, but as open drains require an external pull-up when configured as outputs. |

| SDA, SCL    | 11,12        | SMBus/I <sup>2</sup> C serial interface communication pins.                                                                                                                                                                                                                                                                                  |

| VOUT1-VOUT4 | 5,6,7,8      | Connect to the output of the corresponding power stage. The output is sampled at least once every switching cycle                                                                                                                                                                                                                            |

| LDO5        | 44           | Output of a 5V LDO. This is a micro power LDO that can remain active while the rest of the IC is in shutdown. This LDO is also used to power the internal Analog Blocks.                                                                                                                                                                     |

| LD03_3      | 1            | Output of the 3.3V standby LDO. This is a micro power LDO that can remain active while the rest of the IC is in shutdown.                                                                                                                                                                                                                    |

| ENABLE      | 40           | If ENABLE is pulled high or allowed to float high, the chip is powered up (logic is reset, registers configuration loaded, etc.). The pin must be held low for the XRP7724 to be placed into shutdown.                                                                                                                                       |

| BFB         | 42           | Input from the 15V output created by the external boost supply. When this pin goes below a pre-defined threshold, a pulse is created on the low side drive to charge this output back to the original level. If not used, this pin should be connected to GND.                                                                               |

| DGND        | 17           | Digital ground pin. This is the logic ground connection, and should be connected to the ground plane close to the PAD.                                                                                                                                                                                                                       |

| CPLL        | 3            | Connect to a 2.2nF capacitor to GND.                                                                                                                                                                                                                                                                                                         |

| V5EXT       | 43           | External 5V that can be provided. If one of the output channels is configured for 5V, then this voltage can be fed back to this pin for reduced operating current of the chip and improved efficiency.                                                                                                                                       |

| AVDD        | 4            | Output of the internal 1.8V LDO. A decoupling capacitor should be placed between AVDD and AGND close to the chip.                                                                                                                                                                                                                            |

| PAD         | 45           | This is the die attach paddle, which is exposed on the bottom of the part. Connect externally to the ground plane.                                                                                                                                                                                                                           |

#### **ORDERING INFORMATION**

| Part Number                                                                                                                                                               | Temperature<br>Range         | Marking    | Package | Packing<br>Quantity | Note 1       | I <sup>2</sup> C Default<br>Address |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------|---------|---------------------|--------------|-------------------------------------|--|--|

| XRP7724ILB-F                                                                                                                                                              | -40°C≤T <sub>J</sub> ≤+125°C | XRP7724ILB |         | Bulk                | Halogen Free | 0x28 (7Bit)                         |  |  |

| XRP7724ILBTR-F                                                                                                                                                            | -40°C≤T <sub>J</sub> ≤+125°C | YYWW X     |         | 2.5K/Tape & Reel    | Halogen Free |                                     |  |  |

| XRP7724EVB-DEMO-2P-KIT  Evaluation kit includes XRP7724EVB-DEMO-1 Evaluation Board with Power Architect software and XRP77XXEVB-XCM (USB to I²C Exar Configuration Module |                              |            |         |                     |              |                                     |  |  |

<sup>&</sup>quot;YY'' = Year - "WW" = Work Week - "X" = Lot Number; when applicable.

#### TYPICAL PERFORMANCE CHARACTERISTICS

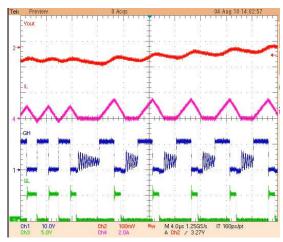

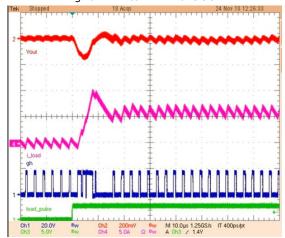

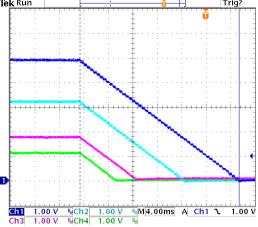

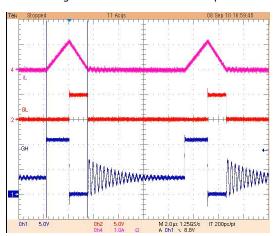

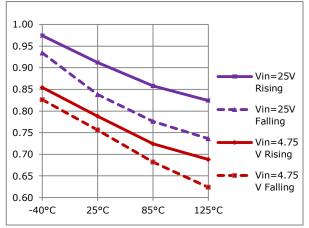

All data taken at VCC = 12V,  $T_1 = T_A = 25$ °C, unless otherwise specified - Schematic and BOM from XRP7724EVB. See XRP7724EVB-DEMO-1 Manual.

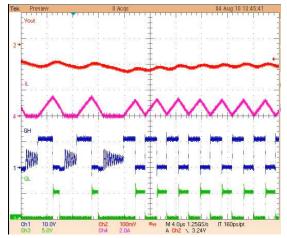

Fig. 5: PFM to PWM Transition

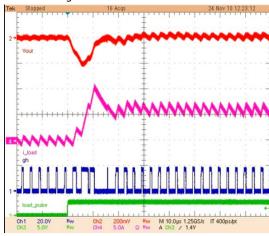

Fig. 7 0-6A Transient 300kHz PWM only

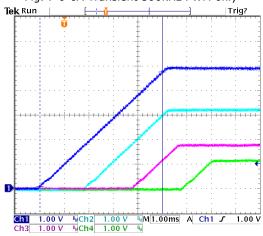

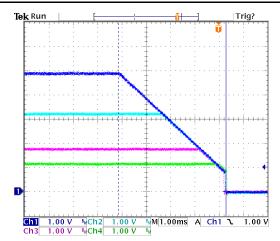

Fig. 9 Sequential Start-up

Fig. 6 PWM to PFM Transition

Fig. 8 10-6A Transient 300kHz with OVS  $\pm 5.5\%$

Fig. 10 Sequential Shut Down

# Tek Prevu Trig? Example Ch1 1.00 V Ch2 1.00 V M4.00ms A Ch4 J 1.06 V Ch3 1.00 V Ch4 1.00 V

Fig. 11: Simultaneous Start-up

Fig. 13: PFM Zero Current Accuracy

Fig. 15: Enable Threshold Over Temp

Fig. 12 Simultaneous Shut Down

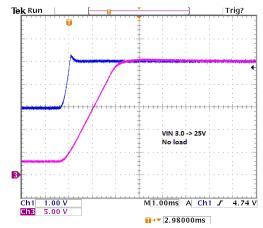

Fig. 14: LDO5 Brown Out Recovery, No Load

#### **FEATURES AND BENEFITS**

#### **Programmable Power Benefits**

#### • Fully Configurable

- Output set point

- Feedback compensation

- Frequency set point

- Under voltage lock out

- Input voltage measurement

- Gate drive dead time

#### Reduced Development Time

- Configurable and re-configurable for different Vout, Iout, Cout, and Inductor values

- No need to change external passives for a new output specification.

#### Higher integration and Reliability

Many external circuits used in the past can be eliminated significantly improving reliability.

#### PowerArchitect™ 5.0 Design and Configuration Software

- Wizard quickly generates a base design

- Calculates all configuration registers

- Projects can be saved and/or recalled

- GPIOs can be configured easily and intuitively

- "Dashboard" Interface can be used for real-time monitoring and debug

#### **System Benefits**

- Reliability is enhanced via communication with the system controller which can obtain real time data on an output voltage, input voltage and current.

- System processors can communicate with the XRP7724 directly to obtain data or make adjustments to react to circuit conditions

- A system process or could also be configured to log and analyze operating history, perform diagnostics and if required, take the supply off-line after making other system adjustments.

#### **System Integration Capabilities**

#### Single supply operation

#### • I<sup>2</sup>C interface allows:

- Communication with a System Controller or other Power Management devices for optimized system function

- Access to modify or read internal registers that control or monitor:

- Output Current

- Input and Output Voltage

- Soft-Start/Soft-Stop Time

- 'Power Good'

- Part Temperature

- Enable/Disable Outputs

- Over Current

- Over Voltage

- Temperature Faults

- Adjusting fault limits and disabling/enabling faults

- Packet Error Checking (PEC) on I<sup>2</sup>C communication

#### 5 GPIO pins with a wide range of configurability

- Fault reporting (including UVLO Warn/Fault, OCP Warn/Fault, OVP, Temperature, Soft-Start in progress, Power Good, System Reset)

- Allows a Logic Level interface with other non-digital IC's or as logic inputs to other devices

#### Frequency and Synchronization Capability

- Selectable switching frequency between 105kHz and 1.2MHz

- Main oscillator clock and DPWM clock can be synchronized to external sources

- `Master', `Slave' and `Stand-alone' Configurations are possible

#### Internal MOSFET Drivers

- Internal FET drivers  $(4\Omega/2\Omega)$  per channel

- Built-In Automatic Dead-time adjustment

- 30ns Rise and Fall times

#### 4 Independent SMPS channels and 2 LDOs in a 7x7mm TQFN

#### **FUNCTIONAL OVERVIEW**

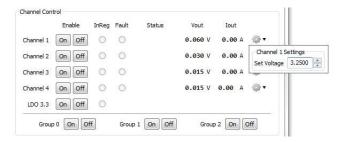

The XRP7724 is a quad-output digital pulse width modulation (DPWM) controller with integrated drivers for aate use synchronous buck switching regulators. Each output voltage can be programmed from 0.6V to 5.5V without the need of an external voltage divider. The wide range of the programmable DPWM switching frequency (from 105 kHz to 1.2 MHz) enables the user to optimize for efficiency or component sizes. Since the digital regulation loop requires no external passive components, performance is not compromised due to external component variation or operating condition.

The XRP7724 provides a number of critical safety features, such as Over-Current Protection (OCP), Over-Voltage Protection (OVP), Over Temperature Protection (OTP) plus input Under Voltage Lockout (UVLO). In addition, a number of key health monitoring features such as warning level flags for the safety functions, Power Goods (PGOOD), etc., plus full monitoring of system voltages and currents. The above are all programmable and/or readable from the SMBus and many are steerable to the GPIOs for hardware monitoring.

For hardware communication, the XRP7724 has two logic level General Purpose Input-Output (GPIO) pins and three, 15V, open drain, Power System Input-Output (PSIO) pins. Two pins are dedicated to the SMBus data (SDA) and clock (SCL). Additional pins include Chip Enable (Enable), Aux Boost Feedback (BFB) and External PLL Capacitor (CPLL).

In addition to providing four switching outputs, the XRP7724 also provides control for an Aux boost supply, and two stand-by linear regulators that produce 5V and 3.3V for a total of 7 customer usable supplies in a single device.

The 5V LDO is used for internal power and is also available for customer use to power

external circuitry. The 3.3V LDO is solely for customer use and is not used by the chip. There is also a 1.8V linear which is for internal use only and should not be used externally.

A key feature of the XRP7724 is its powerful power management capabilities. All four outputs are independently programmable and gives the user not only full control of the delay, ramp, and sequence during power up and power down. One can also control of how the outputs interact and power down in the event of a fault. This includes active ramp down of the output voltages to remove an output voltage as quickly as possible. Another nice feature is that the outputs can be defined and controlled as groups.

The XRP7724 has two main types of programmable memory. The first types are runtime registers that contain configuration, control and monitoring information for the chip. The second type is rewritable Non-Volatile Flash Memory (NVFM) that is used for permanent storage of the configuration data along with various chip internal functions. During power up the run time registers are loaded from the NVFM allowing for standalone operation.

The XRP7724 brings an extremely high level of functionality and performance to а programmable power system. Ever decreasing product budgets require the designer to quickly make aood cost/performance tradeoffs to trulv successful. By incorporating 4 switching channels, two user LDOs, a charge pump boost controller, along with internal gate drivers, all in a single package, the XRP7724 allows for extremely cost effective power system designs. Another key cost factor to put into the cost tradeoffs, which is often overlooked, is the unanticipated Engineering Change Order (ECO). The programmable versatility of the XRP7724, along with the lack hard wired, on board configuration components, allows for minor and major changes to be made, in circuit, on the board by simple reprogramming.

#### THEORY OF OPERATION

#### **CHIP ARCHITECTURE**

#### REGULATION LOOPS

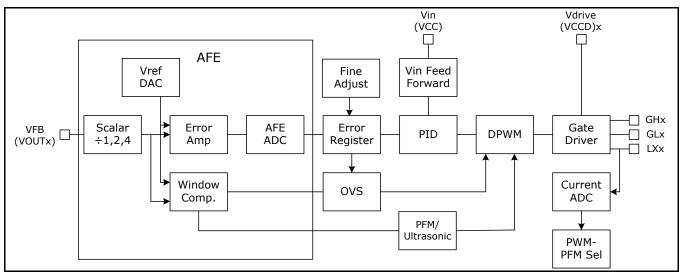

Fig 16 XRP7724 Regulation Loops

Figure 16 shows a functional block diagram of the regulation loops for an output channel. There are four separate parallel control loops; Pulse Width Modulation (PWM), Pulse Frequency Modulation (PFM), Ultrasonic, and Over Sampling (OVS). Each of these loops is fed by the Analog Front End (AFE) as shown at the left of the diagram. The AFE consist of an input voltage scalar, a programmable Voltage Reference (Vref) DAC, Error Amplifier, and a window comparator. (Please note that the block diagram shown is simplified for ease of understanding. Some of the function blocks are common and shared by each channel by means of a multiplexer.)

#### **PWM Loop**

The PWM loop operates in Voltage Control Mode (VCM) with optional Vin feed forward based on the voltage at the VCC pin. The reference voltage (Vref) for the error amp is created by a 0.15V to 1.6V DAC that has a 12.5mV resolution. In order to get a full 0.6V to 5.5V output voltage range an input scalar is used to reduce feedback voltages for higher output voltages to bring them within the 0.15V to 1.6V control range. So for output voltages

up to 1.6V (low range) the scalar has a gain of 1. For output voltages from 1.6V to 3.2V (mid range) the scalar gain is 1/2 and for voltages greater than 3.2V (high range) the gain is 1/4. This results in the low range having a reference voltage resolution of 12.5mV, mid range of 25mV and the high range having a resolution of 50mV. The error amp has a gain of 4 and compares the output voltage of the scalar to Vref to create an error voltage on its output. This is converted to a digital error term by the AFE ADC which is stored in the error register. The error register has a fine adjust function that can be used to improve the output voltage set point resolution by a factor of 5 resulting in a low range resolution of 2.5mV, mid range resolution of 5mV and a high range resolution of 10mV. The output of the error resister is then used by the Proportional Integral Derivative (PID) controller to manage the loop dynamics.

The XRP7724 PID is a 17-bit five coefficient control engine that calculates the correct duty cycle under the various operating conditions and feeds it to the Digital Pulse Width Modulator (DPWM). Besides the normal

coefficients the PID also uses the Vin voltage to provide a feed forward function.

The XRP7724 DPWM includes a special delay timing loop that gives a timing resolution that is 16 times the master oscillator frequency (103MHz) for a timing resolution of 607ns for both the driver pulse width and dead time delays. The DWPM creates and outputs the Gate High (GH) and Gate Low (GL) signals to the driver. The maximum and minimum on times and dead time delays are programmable by configuration resisters.

To provide current information, the output inductor current is measured by a differential amplifier that reads the voltage drop across the RDS of lower FET during its on time. There are two selectable ranges, a low range with a gain of 8 for a +20mV to -120 mV range and a high range with a gain of 4 for +40mV to -280mV range. The optimum range to use will depend on the maximum output current and the RDS of the lower FET. The measured voltage is then converted to a digital value by the current ADC block. The resulting current value is stored in a readable register and also used to determine when PWM to PFM transitions should occur.

#### PFM mode loop

The XRP7724 has a PFM loop that can be enabled to improve efficiency at light loads. By reducing switching frequency and operating in the discontinuous conduction mode (DCM), both switching and  $\rm I^2R$  losses are minimized.

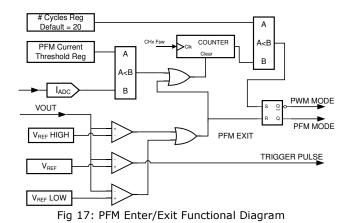

Figure 17 shows a functional diagram of the PFM logic.

The PFM loop works in conjunction with the PWM loop and is entered when the output current falls below a programmed threshold level for a programmed number of cycles. When PFM mode is entered, the PWM loop is disabled and instead, the scaled output voltage is compared to Vref with a window comparator. The window comparator has three thresholds; normal (Vref), high (Vref + %high) and low (Vref - %low). The %high and %low values are programmable and track Vref.

In PFM mode, the normal comparator is used to regulate the output voltage. If the output voltage falls below the Vref level, the comparator is activated and triggers the DPWM to start a switching cycle. When the high side FET is turned on, the inductor current ramps up which charges up the output capacitors and increasing their voltage. After the completion of the high side and low side on-times, the lower FET is turned off to inhibit any inductor reverse current flow. The load current then discharges the output capacitors until the output voltage falls below Vref and the normal comparator is activated this then triggers the DPWM to start the next switching cycle. The time from the end of the switching cycle to the next trigger is referred to as the dead zone. This PFM methodology ensures output voltage ripple does not increase from PWM to PFM.

When PFM mode is initially entered the switching duty cycle is the same that it was in PWM mode. The cause the inductor ripple current to be the same level that it was in PWM mode. During operation the PFM duty cycle is calculated based on the ratio of the output voltage to VCC.

If the output voltage ever goes outside the high/low windows, PFM mode is exited and the PWM loop is reactivated.

Although the PFM mode does a good job in improving efficiency at light load, at very light loads the dead zone time can increase to the point where the switching frequency can enter the audio hearing range. When this happens some components, like the output inductor and ceramic capacitors, can emit audible noise. The amplitude of the noise depends

mostly on the board design and on the manufacturer and construction details of the components. Proper selection of components can reduce the sound to very low levels. In general Ultrasonic Mode is not used unless required as it reduces light load efficiency.

#### **Ultrasonic Mode**

Ultrasonic mode is an extension of PFM to ensure that the switching frequency never enters the audible range. When this mode is entered, the switching frequency is set to 30kHz and the duty cycle of the upper and lower FETs, which are fixed in PFM mode, are decreased as required to keep the output voltage in regulation while maintaining the 30kHz switching frequency.

Under extremely light or zero load currents, the GH on time pulse width can decrease to its minimum width. When this happens, the lower FET on time is increased slightly to allow a small amount of reverse inductor to flow back into Vin to keep the output voltage in regulation while maintaining the switching frequency above the audio range.

#### **Oversampling OVS Mode**

Oversampling (OVS) mode is a feature added XRP7724 to improve transient the responses. This mode can only be enabled when the channel switching frequency is operating in 1x frequency mode. In OVS mode the output voltage is sampled 4 times per switching cycle and is monitored by the AFE window comparator. If the voltage goes outside the set high or low limits, the OVS control electronics can immediately modify the pulse width of the GH or GL drivers to respond accordingly, without having to wait for the next cycle to start. OVS has two types of response depending on whether the high limit is exceeded during an unloading transient (Over Voltage), or the low limit is exceeded during a loading transient (Under Voltage).

**Under Voltage OVS:** If there is an increasing current load step, the output voltage will drop until the regulator loop adapts to the new conditions to return the voltage to the correct level. Depending on where in the switching cycle the load step happens there can be a

delay of up to one switching cycle before the control loop can respond. With OVS enabled if output voltage drops below the lower level, an immediate GH pulse will be generated and sent to the driver to increase the output inductor current toward the new load level without having to wait for the next cycle to begin. If the output voltage is still below the lower limit at the beginning of the next cycle, OVS will work in conjunction with the PID to insert additional GH pulses to quickly return the output voltage back within its regulation band. The result of this system is transient response capabilities on par or exceeding those of a constant on-time control loop.

Over Voltage OVS: When there is a step load current decrease, the output voltage will increase (bump up) as the excess inductor current that is no longer used by the load, flows into the output capacitors causing the output voltage to rise. The voltage will continue to rise until the inductor current decreases to the new load current. With OVS enabled, if the output voltage exceeds the high limit of the window comparator, a blanking pulse is generated to truncate the GH signal. This causes inductor current to immediately begin decreasing to the new load level. The GH will continue to be blanked until the output voltage falls below the high limit. Again, since the output voltage is sampled at four times the switching frequency, over shoot will be decreased and the time required to get back into the regulation band is also decreased.

OVS can be used in conjunction with both the PWM and PFM operating modes. When it is activated it can noticeably decrease output voltage excursions when transitioning between PWM and PFM modes.

#### **INTERNAL DRIVERS**

The internal high and low gate drivers use totem pole FETs for high drive capability. They are powered by two external 5V power pins (VCCD1-2) and (VCCD3-4), VCCD1-2 powers the drivers for channels 1 and 2 and VCCD3-4 powers channels 3 and 4. The drivers can be powered by the internal 5V LDO by connecting their power pins to the LDO5 output through

an RC filter to avoid conducted noise back into the analog circuitry.

To minimize power dissipation in the 5V LDO it is recommended to power the drivers from an external 5V power source either directly or by using the V5EXT input. Good quality 1uF to 4.7uF capacitors should be connected directly between the power pins to ground to optimize driver performance and minimize noise coupling to the 5V LDO supply.

The driver outputs should be connected directly to their corresponding output switching FETs, with the Lx output connected to the drain of the lower FET for the best current monitoring accuracy.

See ANP-32 "Practical Layout Guidelines for Power<sup>XR</sup> Designs"

#### **LDOs**

The XRP7724 has two internal Low Drop Out (LDO) linear regulators that generate 5.0V (LDO5) and 3.3V (LDO3\_3) for both internal and external use. Additionally it also has a 1.8V regulator that supplies power for the XRP7724 internal circuits. Figure 3 shows a block diagram of the linear power supplies. LDO5 is the main power input to the device and is supplied by an external 5.5V to 25V

(VCC) supply. The output of LDO5 should be bypassed by a good quality capacitor connected between the pin and ground close to the device. The 5V output is used by the XRP7724 as a standby power supply and is also used to power the 3.3V and 1.8V linear regulators inside the chip and can also supply power to the 5V gate drivers. The total output current that the 5V LDO can provide is 130mA. The XRP7724 consumes approximately 20mA and the rest is shared between LDO3\_3 and the gate drive currents. During initial power up, the maximum external load should be limited to 30mA.

The 3.3V LDO output available on the LDO3\_3 pin is solely for customer use and is not used internally. This supply may be turned on or off by the configuration registers. Again a good bypass capacitor should be used.

The AVVD pin is the 1.8V regulator output and needs to be connected externally to the DVVD pin on the device. A good quality capacitor should be connected between this pin and ground close to the package.

For operation with a VCC of 4.75V to 5.5V, the LDO5 output needs to be connected directly to VCC on the board.

#### **CLOCKS AND TIMING**

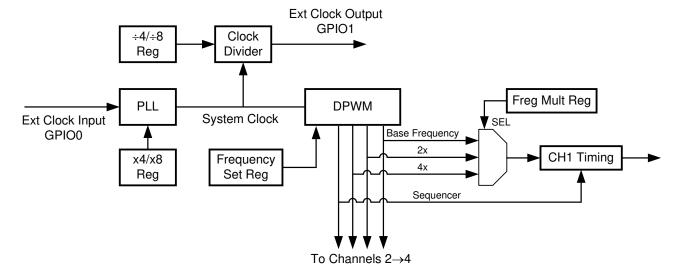

Fig 18 XRP7724 Timing Block Diagram

Figure 18 shows a simplified block diagram of the XRP7724 timings. Again, please note that the function blocks and signal names used are chosen for ease of understanding and do not necessarily reflect the actual design.

The system timings are generated by a 103MHz internal system clock (Sys\_Clk). There are two ways that the 103 MHz system clock can be generated. These include an internal oscillator and a Phase Locked Loop (PLL) that is synchronized to an external clock input. The basic timing architecture is to divide the Sys\_Clk down to create a fundamental switching frequency (Fsw\_Fund) for all the output channels that is settable from 105kHz to 306kHz. The switching frequency for a channel (Fsw\_CHx) can then be selected as 1 times, 2 times or 4 times the fundamental switching frequency.

To set the base frequency for the output channels a "Fsw\_Set" value representing the base frequency shown in Table 1, is entered into the switching frequency configuration register (Fsw\_Set is basically equal to the base frequency times 256). The system timings are then created by dividing down Sys\_Clk to produce a base frequency clock, 2X and 4X times the base frequency clocks, and sequencing timing to position the output channels relative to each other. Each output channel then has its own frequency multiplier register that is used to select its final output switching frequency.

Table 1 shows the available channel switching frequencies for the XRP7724 device. In practice the PowerArchitect $^{\text{TM}}$  5.0 design tool handles all the details and the user only has to enter the fundamental switching frequency and the 1x, 2x, 4x frequency multiplier for each channel.

If an external clock is used, the frequencies in this table will shift accordingly.

| Base<br>Frequency<br>kHz | Available 2x<br>Frequencies<br>kHz | Available 4x<br>Frequencies<br>kHz |

|--------------------------|------------------------------------|------------------------------------|

| 105.5                    | 211.1                              | 422.1                              |

| 107.3                    | 214.6                              | 429.2                              |

| 109.1                    | 218.2                              | 436.4                              |

| 111.0                    | 222.0                              | 444.0                              |

| 112.9                    | 225.9                              | 451.8                              |

| 115.0                    | 229.9                              | 459.8                              |

| 117.0                    | 234.1                              | 468.2                              |

| 119.2                    | 238.4                              | 476.9                              |

| 121.5                    | 242.9                              | 485.8                              |

| 123.8                    | 247.6                              | 495.2                              |

| 126.2                    | 252.5                              | 504.9                              |

| 128.8                    | 257.5                              | 515.0                              |

| 131.4                    | 262.8                              | 525.5                              |

| 134.1                    | 268.2                              | 536.5                              |

| 137.0                    | 273.9                              | 547.9                              |

| 139.9                    | 279.9                              | 559.8                              |

| 143.1                    | 286.1                              | 572.2                              |

| 146.3                    | 292.6                              | 585.2                              |

| 149.7                    | 299.4                              | 598.8                              |

| 153.3                    | 306.5                              | 613.1                              |

| 157.0                    | 314.0                              | 628.0                              |

| 160.9                    | 321.9                              | 643.8                              |

| 165.1                    | 330.1                              | 660.3                              |

| 169.4                    | 338.8                              | 677.6                              |

| 174.0                    | 348.0                              | 695.9                              |

| 178.8                    | 357.6                              | 715.3                              |

| 183.9                    | 367.9                              | 735.7                              |

| 189.3                    | 378.7                              | 757.4                              |

| 195.1                    | 390.2                              | 780.3                              |

| 201.2                    | 402.3                              | 804.7                              |

| 207.7                    | 415.3                              | 830.6                              |

| 214.6                    | 429.2                              | 858.3                              |

| 222.0                    | 444.0                              | 887.9                              |

| 229.9                    | 459.8                              | 919.6                              |

| 238.4                    | 476.9                              | 953.7                              |

| 247.6                    | 495.2                              | 990.4                              |

| 257.5                    | 515.0                              | 1030.0                             |

| 268.2                    | 536.5                              | 1072.9                             |

| 279.9                    | 559.8                              | 1119.6                             |

| 292.6                    | 585.2                              | 1170.5                             |

| 306.5                    | 613.1                              | 1226.2                             |

Table 1

#### **SUPERVISORY AND CONTROL**

Power system design with XRP7724 is accomplished using PowerArchitect design tool version 5 (PA5). All figures referenced in the following sections are taken from PA5. Furthermore, the following sections reference  $I^2C$  commands. For more on these commands please refer to ANP-38.

#### DIGITAL I/O

XRP7724 has two General Purpose Input Output (GPIO) and three Power System Input Output (PSIO) user configurable pins.

- GPIOs are 3.3V CMOS logic compatible and 5V tolerant.

- PSIO configured as outputs are open drain and require external pull-up resistor. These I/Os are 3.3V and 5V CMOS logic compatible, and up to 15V capable.

The polarity of the GPIO/PSIO pins is set in PA5 or with an  $I^2C$  command.

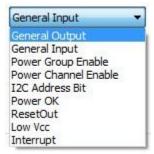

#### **Configuring GPIO/PSIOs**

The following functions can be controlled from or forwarded to any GPIO/PSIO:

- General Output set with an I2C command

- General Input triggers an interrupt; state read with an I2C command

- Power Group Enable controls enabling and disabling of Group 1 and Group 2

- Power Channel Enable controls enabling and disabling of a individual channel including LDO3.3

- I<sup>2</sup>C Address Bit controls an I2C address bit

- Power OK indicates that selected channels have reached their target levels and have not faulted. Multiple channel selection is available in which case the resulting signal is the AND logic function of all channels selected

- ResetOut is delayed Power OK. Delay is programmable in 1msec increments with the range of 0 to 255 msecs

- Low Vcc indicates when Vcc has fallen below the UVLO fault threshold and when the UVLO condition clears (Vcc voltage rises above the UVLO warning level)

- Interrupt the controller generated interrupt selection and clearing is done through I<sup>2</sup>C commands

Interrupt, Low Vcc, Power OK and ResetOut signals can only be forwarded to a single GPIO/PSIO.

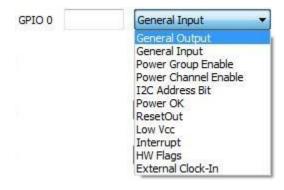

In addition, the following are functions that are unique to GPIO0 and GPIO1.

**HW Flags** – these are hardware monitoring functions forwarded to GPIO0 only. The functions include Under-Voltage Warning, Over- Temperature Warning, Over-Voltage Fault, Over-Current Fault and Over -Current Warning for every channel. Multiple selection is available in which case the resulting signal is the OR logic function

|        |          |   | Under-Voltage Warning     | Over-Te | mp Warnin | ig          |

|--------|----------|---|---------------------------|---------|-----------|-------------|

| GPIO 0 | HW Flags | • | Over-Voltage Fault: CH1   | CH2     | CH3       | ☐ CH        |

|        |          |   | Over-Current Fault: V CH1 | ▼ CH2   | ✓ CH3     | <b>V</b> CH |

|        |          |   | Over-Current Warning: CH1 | CH2     | CH3       | CH          |

External Clock-in – enables the controller to lock to an external clock including one from another XRP7724 applied to the GPIO0 pin. There are two ranges of clock frequencies the controller accepts, selectable by a user

| GPIO 1 | General Input ▼      |

|--------|----------------------|

|        | General Output       |

|        | General Input        |

|        | Power Group Enable   |

|        | Power Channel Enable |

|        | I2C Address Bit      |

|        | Power OK             |

|        | ResetOut             |

|        | Low Vcc              |

|        | Interrupt            |

|        | HW Power Good        |

|        | External Clock-Out   |

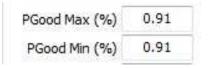

• **HW Power Good** – the Power Good hardware monitoring function. It can only be forwarded to GPIO1. It is an output voltage monitoring function that is a hardware comparison of channel output voltage against its user defined Power Good threshold limits (Power Good minimum and maximum levels). It has no hysteresis. Multiple channel selection is available in which case the resulting signal is the AND logic function of all channels selected.

| 22     |               |   |                   |     |     |                   |

|--------|---------------|---|-------------------|-----|-----|-------------------|

| GPIO 1 | HW Power Good | - | Power Good: 🔽 CH1 | CH2 | CH3 | ✓ CH <sup>4</sup> |

|        | 100           | - |                   |     |     |                   |

The Power Good minimum and maximum levels are expressed as percentages of the target voltage.

XRP7724

"PGood Max" is the upper window and "PGood Min" is the lower window. The minimum and maximum for each of these values can be calculated by the following equation:

$$PGOOD(\%) = \frac{N * LSB(mV) * 10^5}{Vtarget(V)}$$

- Where N =1 to 63 for the PGOOD Max value and N=1 to 62 for the PGOOD Min value. For example, with the target voltage of 1.5V and set point resolution of 2.5mV (LSB), the Power Good min and max values can range from 0.17% to 10.3% and 0.17% to 10.5% respectively. A user can effectively double the values by changing to the next higher output voltage range setting, but at the expense of reduced set point resolution.

- External Clock-out clock sent out through GPIO1 for synchronizing with another XRP7724 (see the clock out section for more information).

#### **FAULT HANDLING**

There are seven different types of fault handling:

- Under Voltage Lockout (UVLO)

monitors voltage supplied to the Vcc pin

and will cause the controller to shutdown

all channels if the supply drops to critical

levels.

- Over Temperature Protection (OTP)

monitors temperature of the chip and will

cause the controller to shutdown all

channels if temperature rises to critical

levels.

- Over Voltage Protection (OVP)

monitors regulated voltage of a channel

and will cause the controller to react in a

user specified way if the regulated voltage

surpasses threshold level.

- Over Current Protection (OCP)

monitors current of a channel and will

cause the controller to react in a user

specified way if the current level surpasses threshold level.

- Start-up Time-out Fault monitors if a channel gets into regulation in a user defined time period

- LDO5 Over Current Protection (LDO5 OCP) monitor current drawn from the regulator and will cause the controller to be reset if the current exceeds LDO5 limit (155mA typical)

- LDO3.3 Over Current Protection (LDO3.3 OCP) monitors current drawn from the regulator and will cause the controller to shut down the regulator if the current exceeds LDO3.3 current limit (65mA typical)

#### **UVLO**

Both UVLO warning and fault levels are user programmable and set at 200mV increments in PA5.

When the warning level is reached the controller will generate the UVLO\_WARNING\_EVENT interrupt. In addition, the host can be informed about the event through HW Flags on GPIO0 (see the Digital I/O section).

When an under voltage fault condition occurs, the XRP7724 outputs are shutdown and the UVLO\_FAULT\_ACTIVE\_EVENT interrupt is generated. In addition, the host can be informed by forwarding the Low Vcc signal to any GPIO/PSIO (see the Digital I/O section). This signal transitions when the UVLO fault occurs. When coming out of the fault, rising Vcc crossing the UVLO fault level will trigger the UVLO FAULT INACTIVE EVENT interrupt.

Once UVLO condition clears (Vcc voltage rises Above or TO the user defined UVLO warning level), the Low Vcc signal will transition and the controller will be reset.

A special attention needs to be paid in the case when Vcc = LDO5 = 4.75V to 5.5V. Since the input voltage ADC resolution is 200mV, the UVLO warning and fault set points are coarse for a 5V input. Therefore, setting the warning level at 4.8V and the fault

level at 4.6V may result in the outputs not reenable until a full 5.0V is reached on Vcc. Setting the warning level to 4.6v and the fault level at 4.4V would likely make UVLO handing as desired, however, below 4.6V the device has a hardware UVLO on LDO5 to ensure proper shutdown of the internal circuitry of the controller. This means the 4.4V UVLO fault level will never occur. A special test has been added to ensure that if UVLO FAULT will

#### **OTP**

User defined OTP warning, fault and restart levels are set at 5°C increments in PA5.

When the warning level is reached the controller will generate the TEMP\_WARNING\_EVENT interrupt. In addition, the host can be informed about the event through HW Flags on GPIO0 (see the Digital I/O section).

When an OTP fault condition occurs, the XRP7724 outputs are shutdown and the TEMP OVER EVENT interrupt is generated.

Once temperature reaches a user defined OTP Restart Threshold level, the TEMP\_UNDER\_EVENT interrupt will be generated and the controller will reset.

#### **OVP**

A user defined OVP fault level is set in PA5 and is expressed in percentages of a regulated target voltage.

Resolution is the same as for the target voltage (expressed in percentages). The OVP minimum and maximum values are calculated by the following equation where the range for N is 1 to 63:

$$OVP(\%) = \frac{N * LSB(mV) * 10^5}{Vtarget(V)}$$

When the OVP level is reached and the fault is generated, the host will be notified by the

#### XRP7724

#### Quad Channel Digital PWM/PFM Programmable Power Management System

SUPPLY\_FAULT\_EVENT interrupt generated by the controller. The host then can use anI2C command to check which channel is at fault.

In addition, OVP fault can be monitored through GPIO0.

A user can choose one of three options on how to react to an OVP event: to shutdown the faulting channel, to shut down faulting channel and to perform auto-restart of the channel, or to restart the chip.

Channel Fault Actions

## Channel 1 Shutdown Channel Shutdown Channel Channel 2 Shutdown and Auto-restart Channel Restart Chip Channel 3 Shutdown Channel Channel 4 Shutdown Channel

In the case of shutting down the faulting channel and auto-restarting, the user has an option to specify startup timeout (the time in which the fault is validated) and hiccup timeout (the period after which the controller will try to restart the channel) periods in 1 msec increments with a maximum value of 255 msec.

Note: a channel will share a response to an OVP or OCP event.

#### **OCP**

A user defined OCP fault level is set with 1mA increments in PA5. PA5 uses calculations to give the user the approximate DC output current entered in the current limit field. However the actual current limit trip value programmed into the part is limited to 280mV

as defined in the electrical characteristics. The maximum value the user can program is limited by Rdson of the synchronous Power FET and current monitoring ADC range. For example, using a synchronous FET with Rdson of  $30m\Omega$ , using the wider ADC range, the maximum current limit programmed would be:

$$OCP\ Max(A) = \frac{280mV}{30m\Omega} = 9.33A$$

The current is sampled approximately 30ns before the low side MOSFET turns off, so the actual measured DC output current in this example would be 9.33A plus approximately half the inductor ripple.

An OCP Fault is considered to have occurred only if the fault threshold has been tripped in 4 consecutive switching cycles. When the switching frequency is using the 4x multiplier, the current is sampled only every other cycle. As a result it can take as many as 8 switching cycles for an over current event to be detected. When operating in 4x mode inductors with a soft saturation characteristic are recommended.

When the OCP level is reached and the fault is generated, the host will be notified by the SUPPLY\_FAULT\_EVENT interrupt generated by the controller. The host then can use an I2C command to check which channel is at fault.

In addition, OCP fault can be monitored through HW Flags on GPIO0. The host can also monitor OCP warning flag through HW Flags on GPIO0. The OCP warning level is calculated by PowerArchitect $^{\text{TM}}$  as 85% of the OCP fault level.

A user can choose one of three options on how to react to an OCP event: to shutdown the faulting channel, to shut down faulting channel and to perform auto-restart of the channel, or to restart the chip.

The output current reported by the XRP7724 is processed through a 7 sample median filter in order to reduce noise. The OCP limit is compared against unfiltered ADC output.

## Channel Fault Actions Channel 1 Shutdown Channel Channel 2 Shutdown and Auto-restart Channel Restart Chip Channel 3 Shutdown Channel Channel 4 Shutdown Channel