Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Digital Line Interface Transceiver

October 2007

#### **FEATURES**

- Single 5V Supply

- Compatible with CCITT G.703 64Kbps Co-Directional Interface Recommendation When Used With Either XRT6165 or XRT6166

- Low Power

- Converts Balanced CMOS Transmit and Receive Signals Propagated Over Two Twisted Pair Cables to TTL Compatible Dual-Rail Data

- Links Remote Equipment Equipped With CCITT G.703 64Kbps Co-Directional Interfaces Over Distances Up to 500 Meters Without Equalization

- Receive Data Comparator Threshold Storage Provides Ping-Pong Operation Capability

- Loss of Signal Alarm

- Dual Matched Driver Outputs

# **APPLICATIONS**

- Data Adaption Unit (DAU)

- General Purpose TTL Compatible Line Interface

## **GENERAL DESCRIPTION**

The XRT6164A is a CMOS analog chip intended for general purpose line interface applications at bit rates up to 1.544Mbps (T1). It contains both receive and transmit circuitry in a 16-pin dual-in-line plastic (PDIP) package. The receiver is designed for short line applications having a cable loss up to 10dB measured at the half bit rate. The transmitter has open collector line driver outputs that are capable of handling up to 40mA. When used in conjunction with either XRT6165 or XRT6166, the chip set provides a 64Kbps codirectional interface as specified in CCITT G.703.

## **ORDERING INFORMATION**

| Part No.   | Package                    | Operating<br>Temperature Range     |

|------------|----------------------------|------------------------------------|

| XRT6164AIP | 16-Lead 300 Mil PDIP       | -4 <b>0</b> ° C to +8 <b>5</b> ° C |

| XRT6164AID | 16-Lead 300 Mil JEDEC SOIC | -4 <b>0</b> ° C to +8 <b>5</b> ° C |

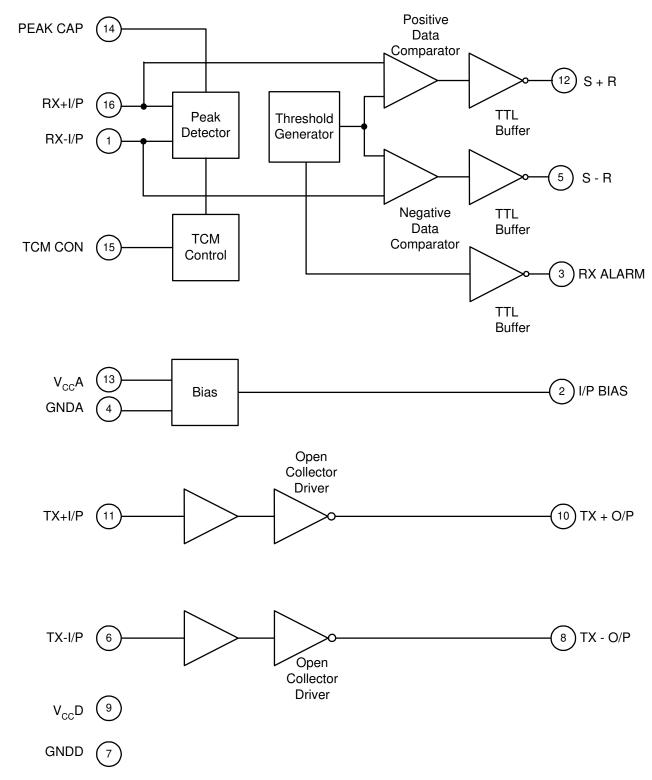

# **Block Dlagram**

Figure 1. XRT6164A Block Diagram

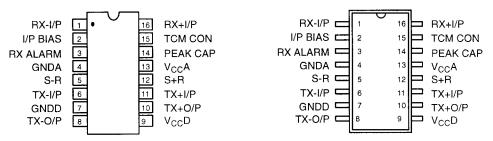

## **PIN CONFIGURATION**

16 Lead PDIP (0.300")

16 Lead SOIC (Jedec, 0.300")

## **PIN DESCRIPTION**

| Pin#   | Symbol    | Type | Description                                                                         |

|--------|-----------|------|-------------------------------------------------------------------------------------|

| 1      | RX-I/P    | I    | Receiver Negative CMOS Input. Line analog input.                                    |

| 2      | I/P BIAS  | 0    | Receive Input Bias. Connects to center tap of input transformer secondary winding.  |

| 3      | RXALARM   | 0    | Loss of Signal Alarm. Active low.                                                   |

| 4      | GNDA      |      | Analog Ground.                                                                      |

| 5      | SR        | 0    | Receive Negative Data Output. Output from negative CMOS input pulses (active low).  |

| 6      | TX-I/P    | Ι    | Transmit Negative Input Data. Input for negative output driver (active high).       |

| 7      | GNDD      |      | Digital Ground.                                                                     |

| 8      | TX-O/P    | 0    | Transmit Negative Output Driver. Open collector, drives output transformer primary. |

| 9      | $V_{cc}D$ |      | +5V +/-5% Digital Supply.                                                           |

| 10     | TX+O/P    | 0    | Transmit Positive Output Driver. Open collector, drives output transformer primary. |

| 11     | TX+I/P    | I    | Transmit Positive Input Data. Input for positive output driver (active high).       |

| 12     | S⊮R       | 0    | Receive Positive Data Output. Output from positive CMOS input pulses (active low).  |

| 13     | $V_{cc}A$ |      | +5V +/-5% Analog Supply.                                                            |

| 14     | PEAKCAP   |      | Peak Detector Capacitor. Stores peak detector voltage.                              |

| 15     | TCMCON    | I    | Time Compression Multiplex Control. When active, disconnects peak detector          |

| charge |           |      | and discharge paths (active low).                                                   |

| 16     | RX+I/P    | I    | Receiver Positive CMOS Input. Line analog input.                                    |

# **ELECTRICAL CHARACTERISTICS**

Test Conditions:  $V_{CC} = 5V + /-5\%$ ,  $T_A = 25$ °C, Unless Otherwise Specified

| Parameters                     | Min.              | Тур. | Max. | Units     | Conditions                                                                      |

|--------------------------------|-------------------|------|------|-----------|---------------------------------------------------------------------------------|

| DC Electrical Characteristics  |                   |      |      |           |                                                                                 |

| Supply Voltage                 | 4.75              | 5    | 5.25 | V         |                                                                                 |

| Analog Supply Current          |                   | 7    | 10   | mA        |                                                                                 |

| Digital Supply Current         |                   | 17   | 22   | mA        |                                                                                 |

| Receiver                       | _                 |      |      |           |                                                                                 |

| Input Signal                   |                   | 1    | 2.2  | Vp        | Measured from Pins 1 or 16 with Respect to Pin 2                                |

| Dynamic Range                  |                   |      | 10   | dB        | Maximum Cable Loss Range                                                        |

| Input Impedance                |                   | 20   |      | kΩ        | Measured Between Pins 1 and 16                                                  |

| Input Slicing Threshold        |                   | 50   |      | %         | Percent of Peak Input Signal Amplitude                                          |

| Input Bias Voltage             |                   | 1.45 |      | V         | Measured at Pin 2                                                               |

| Loss of Signal Alarm Threshold |                   | 150  |      | mVp       | Measured from Pins 1 or 16 with Respect to Pin 2                                |

| Loss of Signal Alarm Level     |                   | 1.5  |      | dB        | Difference Between Alarm-on and Alarm-off                                       |

| Hysteresis                     |                   |      |      |           | Levels                                                                          |

| Peak Detector Leakage          |                   | -80  |      | μА        |                                                                                 |

| Data Output Low                |                   |      | 0.4  | V         | Measured at Pins 5 or 12, I <sub>OUT</sub> = +1.6mA                             |

| Data Output High               | 3.0               |      |      | V         | Measured at Pins 5 or 12, I $_{OUT}$ = -40 $\mu$ A                              |

| Alarm Output Low               |                   |      | 0.4  | ٧         | Measured at Pin 3; I <sub>OUT</sub> = +1.6mA                                    |

| Alarm Output High              | V <sub>cc</sub> - |      |      | V         | Measured at Pin 3; I $_{OUT}$ = -40 $\mu$ A                                     |

| TCM Input Low Voltage          |                   |      | 0.8  | V<br>+5μA | Measured at Pin 15; I $_{\text{IN}}$ Min = -500 $\mu$ A, I $_{\text{IN}}$ Max = |

| Transmitter                    |                   |      |      |           |                                                                                 |

| Input Low Voltage              |                   |      | 0.8  | V         | Measured at Pins 6, 11; I <sub>IN</sub> = -700μA                                |

| Input High Voltage             | 2.2               |      |      | V         | Measured at Pins 6, 11; I <sub>IN</sub> = +5μA                                  |

| Output Low Voltage             |                   |      | 1.2  | V         | Measured at Pins 8, 10; I OUT = -40mA                                           |

| Output Low Current             |                   |      | 40   | mA        | Measured at Pins 8, 10; V <sub>OUT</sub> = 1V                                   |

| Output Leakage Current         | -100              |      |      | μΑ        | Measured at Pins 8, 10; V <sub>OUT</sub> = 10V Outputs in off state             |

| AC Electrical Characteristics  |                   |      |      |           |                                                                                 |

| Receiver                       |                   |      |      |           |                                                                                 |

| Input Level                    |                   | 1    | 2.2  | Vp        | Pin 1, 16 with Respect to Pin 2 1                                               |

| Output Rise Time               |                   |      | 80   | ns        | Pins 5, 12; C L = 15pF, 10% to 90%                                              |

| Output Fall Time               |                   |      | 80   | ns        | Pins 5, 12; C L =15pF, 90% to 10%                                               |

## Notes:

Bold face parameters are covered by production test and guaranteed over operating temperature range.

<sup>1.</sup> Higher input voltages are possible if a resistive input attenuator is used.

# **ELECTRICAL CHARACTERISTIC (CONT'D)**

| Parameters                             | Min. | Тур. | Max. | Units      | Conditions                                                          |  |

|----------------------------------------|------|------|------|------------|---------------------------------------------------------------------|--|

| AC Electrical Characteristics (Cont'd) |      |      |      |            |                                                                     |  |

| Transmitter                            |      |      |      |            |                                                                     |  |

| Output Rise Time                       |      |      | 80   | ns         | Pins 8, 10; R <sub>L</sub> = 130, C <sub>L</sub> = 15pF, 10% to 90% |  |

| Output Fall Time                       |      |      | 80   | ns         | Pins 8, 10; R <sub>L</sub> = 130, C <sub>L</sub> = 15pF, 90% to 10% |  |

| Rising Edge Delay                      |      |      | 100  | ns         | Pins 8, 10; R <sub>L</sub> = 130, C <sub>L</sub> = 15pF, 50% to 50% |  |

|                                        |      |      |      |            | (I/P to O/P)                                                        |  |

| Falling Edge Delay                     |      |      | 100  | <b>n</b> s | Pins 8, 10; R <sub>L</sub> = 130, C <sub>L</sub> = 15pF, 50% to 50% |  |

|                                        |      |      |      |            | (I/P to O/P)                                                        |  |

#### Notes:

Bold face parameters are covered by production test and guaranteed over operating temperature range. Specifications are subject to change without notice

# **ABSOLUTE MAXIMUM RATINGS**

# **Magnetic Supplier Information:**

Pulse Telecom Product Group P.O. Box 12235 San Diego, CA 92112 Tel. (619) 674-8100 Fax. (619) 674-8262 Transpower Technologies, Inc. 24 Highway 28, Suite 202 Crystal Bay, NV 89402-0187 Tel. (702) 831-0140 Fax. (702) 831-3521

# **SYSTEMDESCRIPTION**

The XRT6164A is a general purpose line interface chip that contains the receive and transmit circuitry necessary to convert TTL logic levels to a CMOS signal both to and from a twisted pair cable.

#### Receiver

The XRT6164A receiver section converts a balanced CMOS signal that has been attenuated and distorted by up to 10dB of twisted pair cable to active-low TTL-compatible logic levels.

The cable is transformer coupled to the receiver differential inputs (RX+IP, RX-IP) which are biased through the input transformer secondary winding by a voltage generated on-chip (I/P BIAS). The CMOS receive signal is applied to a peak detector, and to a pair of data comparators. The peak detector output voltage charges an external capacitor connected to PEAK CAP. This voltage generates a data comparator bias level that is approximately 50% of the peak input pulse amplitude.

Thus, data slicing is automatically accomplished at the optimum level over the full cable loss range. TTL-compatible output stages buffer the receiver digital outputs (S+R, S-R) and provide active low signals corresponding to received positive and negative input pulses.

Loss of input signal is detected by a comparator that monitors input signal level. An active-low TTL-compatible logic level (RX ALARM) indicates signal loss. Comparator hysteresis prevents chatter on this output. Ping-pong operation is made possible by the time compression multiplex control input (TCM CON). A logic 0 applied to this pin during transmission stores the peak detector output voltage by disconnecting the peak detector storage capacitor charge and discharge paths.

Since the receive data comparator bias voltage is stored during transmit mode, it is immediately available when receive mode resumes.

#### **Transmitter**

The XRT6164A transmitter section contains two matched open collector output drivers that are capable of driving the line transformer directly with a current up to 40mA. The transmitter output drivers include diode clamps to ensure non-saturating operation. Transmitter digital inputs, which are active-low, are TTL-compatible. External resistors are used between the transmitter outputs and the output transformer primary to set the output pulse amplitude.

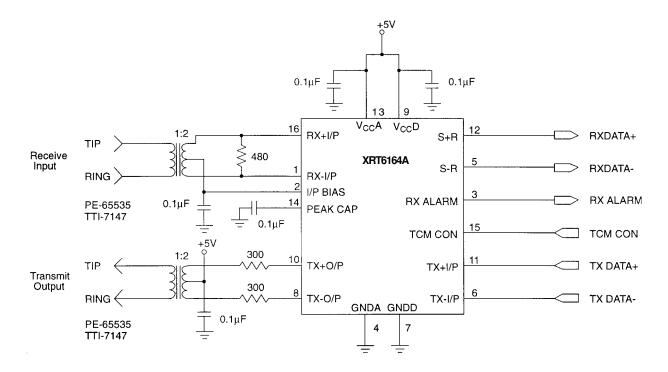

## **APPLICATION INFORMATION**

Figure 2 shows a general line driver application circuit using the XRT6164A. This device converts CMOS transmit and receive signals in the 64Kbps to 1.544Mbps range to active-low TTL-compatible logic levels. CMOS signals that have been attenuated and distorted by twisted pair cable are transformer-coupled to the line side of the XRT6164A as shown on the left side of Figure 2. Suggested transformers for both the input and output applications are the Pulse types PE-65535 or TTI-7147 for 64Kbps use and the PE-65835 for 1.544Mbps applications.

The right side of *Figure 2* shows the TTL-compatible digital inputs and outputs. Please refer to the pin description section of this data sheet for detailed information about each signal.

Figure 2. XRT6164A Line Driver Application

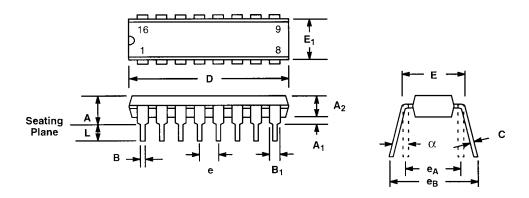

# 16 LEAD PLASTIC DUAL-IN-LINE (300 MIL PDIP)

Rev. 1.00

|        | INC   | HES   | MILLIMETERS |       |  |

|--------|-------|-------|-------------|-------|--|

| SYMBOL | MIN   | MAX   | MIN         | MAX   |  |

| Α      | 0.145 | 0.210 | 3.68        | 5.33  |  |

| A1     | 0.015 | 0.070 | 0.38        | 1.78  |  |

| A 2    | 0.115 | 0.195 | 2.92        | 4.95  |  |

| В      | 0.014 | 0.024 | 0.36        | 0.56  |  |

| B 1    | 0.030 | 0.070 | 0.76        | 1.78  |  |

| С      | 0.008 | 0.014 | 0.20        | 0.38  |  |

| D      | 0.745 | 0.840 | 18.92       | 21.34 |  |

| E      | 0.300 | 0.325 | 7.62        | 8.26  |  |

| E 1    | 0.240 | 0.280 | 6.10        | 7.11  |  |

| е      | 0.100 | BSC   | 2.54 BSC    |       |  |

| e A    | 0.300 | BSC   | 7.62 BSC    |       |  |

| e B    | 0.310 | 0.430 | 7.87        | 10.92 |  |

| L      | 0.115 | 0.160 | 2.92        | 4.06  |  |

| α      | 0°    | 15°   | 0°          | 15°   |  |

Note: The control dimension is the inch column

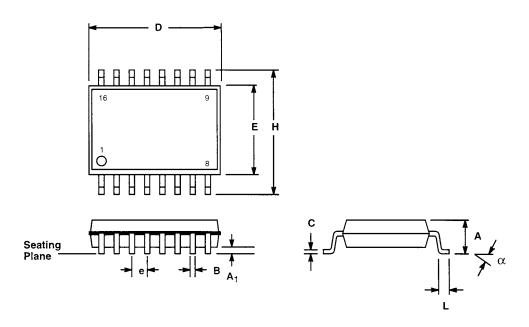

# 16 LEAD SMALL OUTLINE (300 MIL JEDEC SOIC)

Rev. 1.00

|        | INC   | HES   | MILLIMETERS |       |  |

|--------|-------|-------|-------------|-------|--|

| SYMBOL | MIN   | MAX   | MIN         | MAX   |  |

| Α      | 0.093 | 0.104 | 2.35        | 2.65  |  |

| A 1    | 0.004 | 0.012 | 0.10        | 0.30  |  |

| В      | 0.013 | 0.020 | 0.33        | 0.51  |  |

| С      | 0.009 | 0.013 | 0.23        | 0.32  |  |

| D      | 0.398 | 0.413 | 10.10       | 10.50 |  |

| Е      | 0.291 | 0.299 | 7.40        | 7.60  |  |

| е      | 0.050 | BSC   | 1.27 BSC    |       |  |

| Н      | 0.394 | 0.419 | 10.00       | 10.65 |  |

| L      | 0.016 | 0.050 | 0.40        | 1.27  |  |

| α      | 0°    | 8°    | 0°          | 8°    |  |

Note: The control dimension is the millimeter column

## **NOTICE**

EXAR Corporation reserves the right to make changes to the products contained in this publication in order to improve design, performance or reliability. EXAR Corporation assumes no responsibility for the use of any circuits described herein, conveys no license under any patent or other right, and makes no representation that the circuits are free of patent infringement. Charts and schedules contained here in are only for illustration purposes and may vary depending upon a user's specific application. While the information in this publication has been carefully checked; no responsibility, however, is assumed for inaccuracies.

EXAR Corporation does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless EXAR Corporation receives, in writing, assurances to its satisfaction that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; (c) potential liability of EXAR Corporation is adequately protected under the circumstances.

Copyright 2007 EXAR Corporation

Datasheet October 2007

Reproduction, in part or whole, without the prior written consent of EXAR Corporation is prohibited.