Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

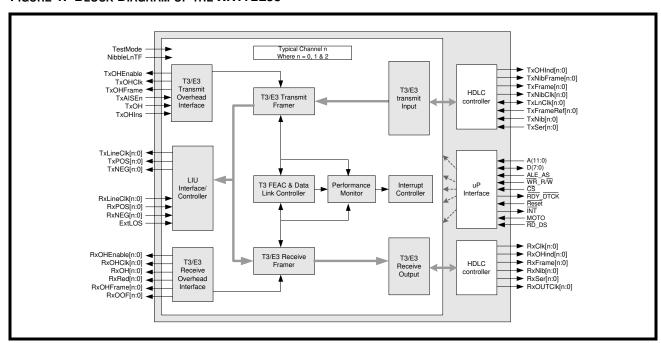

#### THREE CHANNEL DS3/E3 FRAMER IC WITH HDLC CONTROLLER

MAY 2001 REV. P1.1.8

#### GENERAL DESCRIPTION

The XRT72L53, 3 Channel DS3/E3 Framer IC is designed to accept User Data from the Terminal Equipment and insert this data into the Payload bit-fields within an Outbound DS3/E3 Data Stream. Further, the Framer IC is also designed to receive an Inbound DS3/E3 Data Stream (from the Remote Terminal Equipment) and extract out the User Data.

The XRT72L53 DS3/E3 Framer device is designed to support full-duplex data flow between Terminal Equipment and an LIU (Line Interface Unit) IC. The Framer Device will transmit, receive and process data in the DS3-C-bit Parity, DS3-M13, E3-ITU-T G.751 and E3-ITU-T G.832 (November 1995 and October 1998 Revisions) Framing Formats.

The XRT72L53 DS3/E3 Framer IC consists of three Transmit sections, three Receiver sections, three Performance Monitor Sections and a Microprocessor interface.

The Transmit Sections, include a Transmit Payload Data Input Interface block, a Transmit Overhead Data Input Interface block, a Transmit HDLC Controller, a Transmit DS3/E3 Framer block and a Transmit LIU Interface Block which allows the Terminal Equipment to transmit data to a remote terminal.

The Receive Sections, consist of a Receive LIU Interface, a Receive DS3/E3 Framer, a Receive HDLC Controller, a Receive Payload Data Output Interface, and a Receive Overhead Data Interface which allows

the local terminal equipment to receive data from remote terminal equipment.

The Microprocessor Interface is used to configure the Framer in different operating modes and monitor the performance of the Framer.

The Performance Monitor Sections consist of a large number of Reset-upon-Read and Read-Only registers that contain cumulative and One-Second statistics that reflect the performance/health of the three channels of the Framer IC/system.

#### **FEATURES**

- Transmits, Receives and Processes data in the DS3-C-bit Parity, DS3-M13, E3-ITU-T G.751 and E3-ITU-T G.832 Framing Formats.

- · 3 Channel HDLC Controller Tx and Rx

- Interfaces to all Popular Microprocessors

- · Integrated Framer Performance Monitor

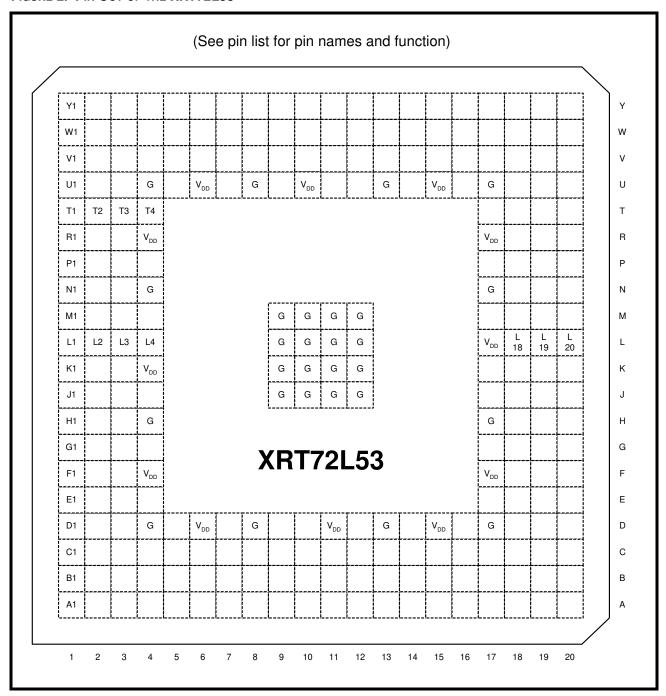

- Available in a 272 Ball PBGA package

- 3.3V Power Supply, 5V Tolerant I/O

- Operating Temperature -40°C to +85°C

#### **APPLICATIONS**

- · Network Interface Units

- CSU/DSU Equipment.

- PCM Test Equipment

- Fiber Optic Terminals

- DS3/E3 Frame Relay Equipment

FIGURE 1. BLOCK DIAGRAM OF THE XRT72L53

#### FIGURE 2. PIN OUT OF THE XRT72L53

# **ORDERING INFORMATION**

| PART NUMBER | PACKAGE TYPE           | OPERATING TEMPERATURE RANGE |

|-------------|------------------------|-----------------------------|

| XRT72L53    | 27x27 mm 272 Ball PBGA | -40°C to +85°C              |

# **PIN DESCRIPTIONS**

#### PIN DESCRIPTION No Connection Pins

| Pin# | PIN NAME | Түре | DESCRIPTION                                             |

|------|----------|------|---------------------------------------------------------|

| J18  | NC       | **** | No Connection                                           |

| K1   | NC       |      | The pins listed here are not connected in the XRT72L53. |

| K2   | NC       |      |                                                         |

| L2   | NC       |      |                                                         |

| L4   | NC       |      |                                                         |

| L19  | NC       |      |                                                         |

| M2   | NC       |      |                                                         |

| M4   | NC       |      |                                                         |

| N2   | NC       |      |                                                         |

| P1   | NC       |      |                                                         |

| P4   | NC       |      |                                                         |

| R1   | NC<br>NC |      |                                                         |

| R2   | NC<br>NC |      |                                                         |

| T2   | NC<br>NC |      |                                                         |

| T4   | NC<br>NC |      |                                                         |

| U1   | NC<br>NC |      |                                                         |

| U2   | NC<br>NC |      |                                                         |

| U7   | NC<br>NC |      |                                                         |

|      |          |      |                                                         |

| U16  | NC<br>NC |      |                                                         |

| U18  | NC<br>NC |      |                                                         |

| V2   | NC<br>NO |      |                                                         |

| V3   | NC       |      |                                                         |

| V4   | NC       |      |                                                         |

| V5   | NC       |      |                                                         |

| V8   | NC       |      |                                                         |

| V9   | NC       |      |                                                         |

| V10  | NC       |      |                                                         |

| V11  | NC       |      |                                                         |

| V12  | NC       |      |                                                         |

| V13  | NC       |      |                                                         |

| V14  | NC       |      |                                                         |

| V15  | NC       |      |                                                         |

| V18  | NC       |      |                                                         |

| V19  | NC       |      |                                                         |

| W7   | NC       |      |                                                         |

| W14  | NC       |      |                                                         |

| W17  | NC       |      |                                                         |

| W18  | NC       |      |                                                         |

| Y1   | NC       |      |                                                         |

| Y2   | NC       |      |                                                         |

| Y3   | NC       |      |                                                         |

| Y5   | NC       |      |                                                         |

| Y6   | NC       |      |                                                         |

| Y8   | NC       |      |                                                         |

| Y9   | NC       |      |                                                         |

| Y11  | NC       |      |                                                         |

| Y12  | NC       |      |                                                         |

| Y13  | NC       |      |                                                         |

| Y16  | NC       |      |                                                         |

| Y17  | NC       |      |                                                         |

| Y20  | NC       |      |                                                         |

|      |          |      |                                                         |

| PIN# | PIN NAME                      | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------|-------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1   | TxLev[1]                      | 0    | Transmit Line Build-Out Enable/Disable Select output pin - Channel 1: See Description for Pin C3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| A2   | EncoDis[1]                    | 0    | HDB3/B3ZS Encoder Enable/Disable output pin - Channel 1:<br>See Description for Pin B2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| А3   | RxOOF[0]                      | 0    | Receive Out of Frame Indicator - Channel 0: The Receive Section of Channel 0, within the XRT72L53 Framer IC will assert this output signal whenever it has declared an Out of Frame (OOF) condition with the incoming DS3 or E3 frames. This signal is negated when the framer correctly locates the framing alignment bits or bytes and correctly aligns itself with the incoming DS3 or E3 frames.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| A4   | RxRed[1]                      | 0    | Receive Red Alarm Indicator - Channel 1:<br>See Description for Pin B5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| A5   | REQ[0]                        | 0    | Receive Equalization Enable/Disable Select output pin - Channel 0-(to be connected to the DS3/E3 Line Interface Unit IC): This output pin is intended to be connected to either the $\overline{\text{REQ}}$ , REQDIS or REQEN input pin of the DS3/E3 LIU. The user can control the state of this output pin by writing a '0' or '1' to Bit 5 ( $\overline{\text{REQ}}$ ) within the Line Interface Driver Register (Address = 0x80). This output pin permits the user to have control over the state of the Receive Equalizer block(s) within the corresponding DS3/E3 LIU IC. Writing a "1" to Bit 5 of the Line Interface Drive Register (Address = 0x80) will cause this output pin to toggle "High". Writing a "0" to this bit-field will cause this output pin to toggle "Low".  Note: This output pin can also be used as a "General Purpose Output" pin. |

| A6   | LLOOP[1]                      | 0    | Local Loop-back Output pin - Channel 1 (to be connected to the LLOOP input pin of the DS3/E3 LIU IC): See Description for Pin C7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| A7   | RLOOP[1]                      | 0    | Remote Loop-back Output pin - Channel 1 (to be connected to the RLOOP input pin of the DS3/E3 LIU IC): See Description for Pin B7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| A8   | ExtLOS[1]                     | I    | Receive LOS (Loss of Signal) Input - Channel 1:<br>See Description for Pin D9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| A9   | RxOHClk[1]/<br>RxHDLCClk[1]   | 0    | Receive Overhead Data Output Clock signal/Receive HDLC Controller Output Clock signal - Channel 1: See Description for Pin D12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| A10  | TxOHClk[1]                    | 0    | Transmit Overhead Clock Output - Channel 1:<br>See Description for Pin A14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| A11  | TxOHFrame[1]/<br>TxHDLCClk[1] | 0    | Transmit Overhead Framing Pulse/Transmit HDLC Controller Output clock signal - Channel 1: See Description for Pin C13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| A12  | TxOH[1]/<br>TxHDLCDat5[1]     | I    | Transmit Overhead Input pin/Transmit HDLC Controller Data Input - Bit 5 (Channel 1): See Description for Pin A15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Pin# | PIN NAME                    | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------|-----------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A13  | RxOHFrame[0]/ RxHDLCDat4[0] | 0    | Receive Overhead Frame Boundary Indicator/Receive HDLC Controller Data Output - Bit 4  The exact functionality of this output pin depends upon whether Channel 0 has been configured to operate in the "High Speed HDLC Controller" Mode, or not.  Non-High Speed HDLC Controller Mode - Receive Overhead Frame Boundary Indicator:  This output pin pulses "High" whenever the Receive Overhead Data Output Interface" block outputs the first overhead bit (or nibble) of a new DS3 or E3 frame.  High Speed HDLC Controller Mode - Receive HDLC Data Output - Bit 4:  This pin functions as bit 4, within the byte-wide Receive HDLC Controller output interface (RxHDLCDat[7:0]), whenever Channel 0 has been configured to operate in the "High Speed HDLC Controller" Mode.                                                                                                                                                                                                                                                                                                                                                                                                             |

| A14  | TxOHClk[0]                  | 0    | Transmit Overhead Clock output - Channel 0: This output signal serves two purposes: 1. The Transmit Overhead Data Input Interface block will provide a rising clock edge on this signal, one bit-period prior to the start to the instant that the "Transmit Overhead Data Input Interface" block (associated with Channel 1) is processing an overhead bit. 2. The Transmit Overhead Data Input Interface will sample the data at the "TxOH[0]" input pin, on the falling edge of this clock signal (provided that the "TxOHIns[0]" input pin is "HIGH").  Note: The Transmit Overhead Data Input Interface block will supply a clock edge for all overhead bits within the DS3 or E3 frame (via the "TxOHClk[0]" output signal). This includes those overhead bits that the "Transmit Overhead Data Input Interface" will not accept from the Terminal Equipment.                                                                                                                                                                                                                                                                                                                           |

| A15  | TxOH[0]/                    |      | Transmit Overhead Input Pin/Transmit HDLC Controller Data Input - Bit 5 (Channel 0):  The exact functionality of this input pin depends upon whether Channel 0 has been configured to operate in the "High-Speed HDLC Controller" Mode, or not.  Non-High Speed HDLC Controller Mode - Transmit Overhead Input pin - Channel 0:  The Transmit Overhead Data Input Interface accepts the overhead data via this input pin, and inserts into the overhead bit position within the very next outbound DS3 or E3 frame. If the TxOHIns pin is pulled "High", then the Transmit Overhead Data Input Interface will sample the data at this input pin (TxOH[0]), on the falling edge of the TxOHClk[0] output pin. Conversely, if the TxOHIns[0] pin is pulled "Low", then the Transmit Overhead Data Input Interface will NOT sample the data at this input pin (TxOH[0]). Consequently, this data will be ignored.  High Speed HDLC Controller Mode - Transmit HDLC Data Input - Bit 5:  This pin functions as bit 5, within the byte-wide Transmit HDLC Controller input interface (TxHDLCDat[7:0]), whenever Channel 0 has been configured to operate in the "High Speed HDLC Controller" Mode. |

REV. P1.1.7

| Pin# | PIN NAME                     | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------|------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A16  | TxNib2[1]/<br>TxHDLCDat2[1]  | I    | Transmit Nibble-Parallel Data Input - Bit 2/Transmit HDLC Data Input - Bit 2; Channel 1: See Description for Pin C20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| A17  | RxSer[1]/<br>RxIdle[1]       | 0    | Receive Serial Output/Receive Flag Sequence Indicator - Channel 1: See Description for Pin F19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| A18  | TxOHInd[1]/<br>TxHDLCDat6[1] | 0    | Transmit Overhead Data Indicator output/Transmit HDLC Data Input - Bit 6; Channel 1: See Description for Pin E19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| A19  | RxOHInd[1]                   | 0    | Receive Overhead Bit Indicator output - Channel 1:<br>See Description for Pin G18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| A20  | RxClk[1]                     | 0    | Receive Clock Output signal for Serial and Nibble-Parallel Data Interface - Channel 1: See Description for Pin D20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| B1   | TDI                          | I    | Test Data In: Boundary Scan Test data input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| B2   | EncoDis[0]                   | 0    | Encoder (HDB3/B3ZS) Disable Output pin - Channel 0 (intended to be connected to either the ENCODIS or the ENDECDIS input to the DS3/E3 Line Interface Unit IC):  This output pin is intended to be connected to either the Encodis or ENDECDIS input pin of the DS3/E3 Line Interface Unit IC. The user can control the state of this output pin by writing a "0" or "1" to Bit 3 (Encodis) within the Line Interface Driver Register (Address = 0x80). If the user commands this signal to toggle "High" then it will disable the B3ZS/HDB3 encoder circuitry within the DS3/E3 LIU IC. Conversely, if the user commands this output signal to toggle "Low", then the B3ZS/HDB3 Encoder circuitry, within the DS3/E3 LIU IC will be enabled.  Writing a "1" to Bit 3 of the Line Interface Driver Register (Address = 0x80) will cause this output pin to toggle "High". Writing a "0" to this bit-field will cause this output pin to toggle "How".  The user is advised to disable the B3ZS/HDB3 encoder (within the DS3/E3 LIU IC) if Channel 0, within the XRT72L53 Framer IC has been configured to operate in the B3ZS/HDB3 line code.  Note: .This output pin can be used as a "General Purpose" Output pin. |

| В3   | RxLOS[1]                     | 0    | Receive LOS (Loss of Signal) Indicator Output - Channel 1:<br>See Description for Pin C4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| B4   | RxAIS[1]                     | 0    | Receive AIS (Alarm Indication Signal) Indicator Output - Channel 1: See Description for Pin C5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| B5   | RxRed[0]                     | 0    | Receive Red Alarm Indicator Output - Channel 0: The Framer toggles this output pin "high" to denote that one of the following events has been detected by the Receive Framer block, within Channel 0: LOS - Loss of Signal Condition OOF - Out of Frame Condition AIS - Alarm Indication Signal Detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Pin# | PIN NAME                     | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------|------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| В6   | Req[1]                       | 0    | Receive Equalization Enable/Disable Select output pin - Channel 1:<br>See Description for Pin A5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| B7   | RLOOP[0]                     | 0    | Remote Loopback Output Pin - Channel 0 (to be connected to DS3/E3 Line Interface Unit IC):                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|      |                              |      | This output pin is intended to be connected to the RLOOP input pin of the DS3/E3 Line Interface Unit IC. The user can command this signal to toggle "High" and, in turn, force the DS3/E3 Line Interface Unit IC into either the Remote or Digital Local- Loopback modes (depending upon the state of the LLOOP[0] pin. Conversely, the user can command this signal to toggle "Low" and allow the XRT7300 device to operate in the normal mode.  Writing a "1" to bit 1 of the Line Interface Drive Register (Address = 0x80) will cause this output pin to toggle "High". Writing a "0" to this bit-field will cause the RLOOP output to toggle "Low".  Note: This output pin can be used as a General Purpose Output pin. |

| В8   | RLOL[0]                      | I    | Receive Loss of Lock Indicator input pin - Channel 0 (from the DS3/E3 Line Interface Unit IC):                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      |                              |      | This input pin is intended to be connected to the RLOL (Receive Loss of Lock) output pin of the DS3/E3 Line Interface Unit IC. The user can monitor the state of this pin by reading the state of Bit 1 (RLOL) within the Line Interface Scan Register (Address = 0x81).  If this input pin is "Low", then it means that the clock recovery phase-                                                                                                                                                                                                                                                                                                                                                                           |

|      |                              |      | locked-loop circuitry, within the LIU device is properly locked onto the incoming DS3 E3 data-stream; and is properly recovering clock and data from this DS3/E3 data-stream. However, if this input pin is "High", then it means that the phase-locked-loop circuitry, within the LIU device has lost lock with the incoming DS3 or E3 data-stream, and is not properly recovering clock and data.  If the customer is not using an "Exar XRT73L0X Family of DS3/E3 LIU ICs, then this input pin can be used for other purposes.                                                                                                                                                                                            |

| В9   | DMO[1]                       | I    | Drive Monitor Output input pin - Channel 1 (from the DS3/E3 LIU IC): See Description for Pin C9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| B10  | RxOH[1]/<br>RxHDLCDat6[1]    | 0    | Receive Overhead Data Output port/Receive HDLC Data Output - Bit 6; Channel 1: See Description for Pin C12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| B11  | TxOHIns[1]/<br>TxHDLCDat4[1] | I    | Transmit Overhead Data Insert Input/Transmit HDLC Data Input - Bit 4 - Channel 1: See Description for Pin C14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| B12  | TxAISEn[1]                   | I    | Transmit AIS Command Input - Channel 1:<br>See Description for Pin B15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

REV. P1.1.7

| Pin# | PIN NAME                    | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------|-----------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B13  | RxOHEnable[0]/              | 0    | Receive Overhead Enable Indicator/Receive HDLC Controller Data Output - Bit 5; Channel 0:  The exact functionality of this output pin depends upon whether Channel 0 has been configured to operate in the "High-Speed HDLC Controller" Mode, or not.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|      |                             |      | Non-High Speed HDLC Controller Mode - Receive Overhead Enable Indicator - Channel 0:  The XRT72L53 will assert this output signal for one "RxOutClk" period when it is safe for the Terminal Equipment to sample the data on the "RxOH" output pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|      | RxHDLCDat5[0]               |      | High-Speed HDLC Controller Mode - Receive HDLC Controller Data Ouptut - Bit 5, Channel 0:  This pin functions as bit 5, within the byte-wide Receive HDLC Controller output interface (RxHDLCDat[7:0]), whenever Channel 0 has been configured to operate in the "High-Speed HDLC Controller" Mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| B14  | TxOHEnable[0]/              | 0    | Transmit Overhead Input Enable/Transmit HDLC Controller Data Output - Bit 7; Channel 0:  The exact functionality of this bit-field depends upon whether Channel 0 has been configured to operate in the "High-Speed HDLC Controller" Mode, or not.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | TxHDLCDat7[0]               | I    | Non-High Speed HDLC Controller Mode - Transmit Overhead Input Enable Output - Channel 0:  Channel 0, within the XRT72L53 device, will assert this signal, for one "TxInClk[0]" period, just prior to the instant that the "Transmit Overhead Data Input Interface" will be sampling and processing an overhead bit. If the Terminal Equipment intends to insert its own value for an overhead bit, into the outbound DS3 or E3 frame, it is expected to sample the state of this signal, upon the falling edge of "TxInClk". Upon sampling the "TxOHEnable" high, the Terminal Equipment should (1) place the desired value of the overhead bit, onto the "TxOH" input pin and (2) assert the "TxOHIns" input pin. The Transmit Overhead Data Input Interface" block will sample and latch the data on the "TxOH" signal, upon the rising edge of the very next "TxInClk" input signal.  High-Speed HDLC Controller Mode - Transmit HDLC Data Input - |

|      |                             |      | Bit 7; Channel 0: This pin functions as bit 5, within the byte-wide Transmit HDLC Controller input interface (TxHDLCDat[7:0]), whenever Channel 0 has been configured to operate in the "High-Speed HDLC Controller" Mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| B15  | TxAISEn[0]                  | I    | Transmit AlS Command Input - Channel 0: Setting this input pin "High" configures the Transmit Section of Channel 0 to generate and transmit an AIS Pattern. Setting this input pin "Low" configures the Transmit Section to generate E3 or DS3 traffic in a normal manner.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| B16  | TxNib3[1]/<br>TxHDLCDat3[1] | I    | Transmit Nibble-Parallel Payload Data Input - Bit 3/Transmit HDLC Data Input - Bit 3; Channel 1: See Description for Pin D19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Pin# | PIN NAME                    | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                           |

|------|-----------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B17  | TxNibFrame[1]/<br>ValFCS[1] | 0    | Transmit Frame Boundary Indicator - Nibble-Parallel Interface/ Transmit HDLC - VALID FRAME CHECK SEQUENCE Indicator - Channel 1: See Description for Pin G17                                                                                                                                                                                                                                          |

| B18  | RxFrame[1]                  | 0    | Receive Boundary of DS3 or E3 Frame Output Indicator - Channel 1:<br>See Description for Pin F20                                                                                                                                                                                                                                                                                                      |

| B19  | RxNib0[1]/<br>RxHDLCDat0[1] | 0    | Receive Nibble Output - Bit 0/Receive HDLC Data Output - Bit 0;<br>Channel 1:<br>See Description for Pin G19                                                                                                                                                                                                                                                                                          |

| B20  | RxNib2[1]/<br>RxHDLCDat2[1] | 0    | Receive Nibble Output - Bit 2/Receive HDLC Data Output - Bit 2;<br>Channel 1:<br>See Description for Pin H18                                                                                                                                                                                                                                                                                          |

| C1   | TxPOS[0]                    | 0    | Transmit Positive Polarity Pulse output - Channel 0: The exact role of this output pin depends upon whether Channel 0 is operating in the Single-Rail or Dual-Rail Mode.                                                                                                                                                                                                                              |

|      |                             |      | Single-Rail Mode: This output pin functions as the Single-Rail output signal for the outbound DS3 or E3 data stream. The signal, at this output pin, will be updated on the user-selected edge of the TxLineClk signal.                                                                                                                                                                               |

|      |                             |      | Dual-Rail Mode: This output pin functions as one of the two dual rail output signals that commands the sequence of pulses to be driven on the line. TxNEG[0] is the other output pin. This input is typically connected to the TPDATA input of the external DS3 or E3 Line Interface Unit IC. When this output is asserted, it will command the LIU to generate a positive polarity pulse on the line |

| C2   | TCK                         | I    | Test Clock: Boundary Scan clock input.                                                                                                                                                                                                                                                                                                                                                                |

REV. P1.1.7

| Pin# | PIN NAME | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C3   | TxLev[0] | 0    | Transmit Line Build-Out Enable/Disable Select Output - Channel 0 (to be connected to the DS3/E3 Line Interface Unit IC):  This output pin is intended to be connected to the TxLev input pin of the DS3/E3 Line Interface Unit IC. The user can control the state of this output pin by writing a "0" or a "1" to Bit 2 (TxLev) within the Line Interface Driver Register (Address = 0x80).  Writing a "1" to Bit 2 of the Line Interface Drive Register (Address = 0x80) will cause this output pin to toggle "High". Writing a "0" to this bit-field will cause this output pin to toggle "Low".  For DS3 Application:  If the user commands this signal to toggle "High" then the Transmit Line Build-Out circuit (within the DS3/E3 LIU device) will be disabled. In this mode, the LIU device will output unshaped (e.g., square) pulses onto the line (via the TTIP and TRING output pins).  Conversely, if the user commands this signal to toggle "Low" then the Transmit Line Build-Out circuit (within the DS3/E3 LIU device) will be disabled. In this mode, the LIU device will output shaped (e.g., more rounded) pulses onto the line (via the TTIP and TRING output pins). In order to comply with the DSX-3 Isolated Pulse Template Requirement (per Bellcore GR-499-CORE), the user is advised to command this output pin to be "High" if the cable length (between the transmit output of the XRT7300 device and the DSX-3 Cross-Connect System) is greater than 225 feet. Conversely, the user is advised to command this output pin to be "Low" if the cable length (between the transmit output of the XRT7300 device and the DSX-3 Cross Connect System) is less than 225 feet.  For E3 Applications:  This pin can be used as a General Purpose Output pin. The Transmit Line Build-Out circuitry (within the XRT7300 device) is not active for E3 |

| C4   | RxLOS[0] | 0    | applications.  Receive Loss of Signal Output Indicator - Channel 0: This pin is asserted when the Receive Section of Channel 0 encounters a string of 180 consecutive 0's (for DS3 operation) or 32 consecutive 0's (for E3 operation) via the RxPOS[0] and RxNEG[0] pins. This pin will be negated once the Receive Section has detected at least 60 pulses within 180 bit-periods (for DS3 operation); or the Receive Section has detected a string of 32 consecutive bits, that does not contain a string of 4 consecutive "0s" (for E3 operation).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| C5   | RxAIS[0] | 0    | Receive Alarm Indication Signal Output pin - Channel 0: Channel 0 will assert this pin to indicate that the Alarm Indication Signal (AIS) has been identified in the Receive DS3 or E3 data stream.  For DS3 Applications: Channel 0 will assert this pin to indicate that the Alarm Indication Signal (AIS) has been identified in the Receive DS3 data stream. An AIS is detected if the payload consists of the recurring pattern of 1010 and this pattern persists for 63 M-frames. An additional requirement for AIS indication is that the C-bits are set to 0, and the X-bits are set to 1. This pin will be negated when a sufficient number of frames, not exhibiting the "1010" pattern in the payload has been detected.  For E3 Applications: Channel 0 will declare an AIS condition, if it detects two consecutive E3 frames, each containing 7 or less "0s".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Pin# | PIN NAME                        | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------|---------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C6   | TAOS[0]                         | 0    | Transmit All Ones Signal (TAOS) Command Input - Channel 0 (for the DS3/E3 LIU IC):                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      |                                 |      | This output pin is intended to be connected to the TAOS input pin of the DS3/E3 Line Interface Unit IC. The user can control the state of this output pin by writing a '0' or '1' to Bit 4 (TAOS) of the Line Interface Drive Register (Address = 0x80). If the user commands this signal to toggle "High" then it will force the Line Interface Unit IC to transmit an "All Ones" pattern onto the line. Conversely, if the user commands this output signal to toggle "Low" then the DS3/E3 Line Interface Unit IC will proceed to transmit data based upon the pattern that it receives via the TxPOS[0] and TxNEG[0] output pins.  Writing a "1" to Bit 4 of the Line Interface Drive Register (Address = 0x80) will cause this output pin to toggle "High". Writing a "0" to this bit-field will cause this output pin to toggle "Low".  If the customer is not using an Exar "XRT73L0X Family of DS3/E3 LIU ICs then this output pin can be used for a variety of other purposes. |

| C7   | LLOOP[0]                        | 0    | Local Loopback Output Pin - Channel 0 (to be connected to the DS3/E3 Line Interface Unit IC):  This output pin is intended to be connected to the LLOOP input pin of the DS3/E3 LIU IC. The user can command this signal to toggle "High" and, in turn, force the LIU into the Local Loopback mode.  Writing a "1" to bit 1 of the Line Interface Drive Register (Address = 0x80) will cause this output pin to toggle "High". Writing a "0" to this bit-field will cause the RLOOP output to toggle "Low".                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |