Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# **XRT72L71**

#### **DS3 ATM UNI/CLEAR CHANNEL FRAMER**

AUGUST 2002 REV. 1.1.0

#### **GENERAL DESCRIPTION**

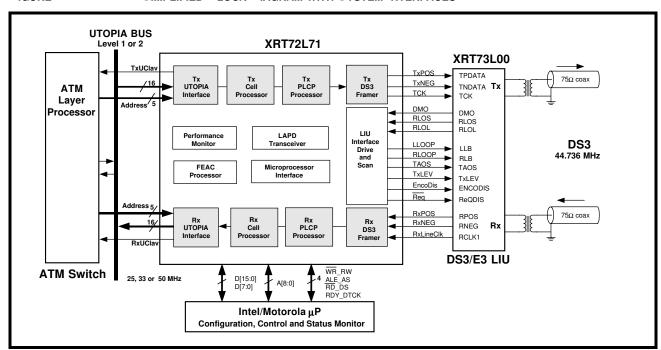

The XRT72L71 DS3 ATM User Network Interface (UNI)/Clear-Channel Framer is designed to function as either a DS3 ATM UNI or Clear channel framer. For ATM UNI applications, this device provides the ATM Physical Layer (Physical Medium Dependent and Transmission Convergence sub-layers) interface for both the public and private networks at DS3 rates. For Clear-Channel framer applications, this device supports the transmission and reception of "user data" via the DS3 payload bits.

The XRT72L71incorporates Receive, Transmit, Microprocessor Interface, Performance Monitor, Test and Diagnostic and Line Interface Unit Scan Drive sections.

#### **APPLICATIONS**

- · Private User Network Interfaces

- · ATM Switches

- ATM Concentrators

- DSLAM Equipment

- · DS3 Frame Relay Equipment

#### **FEATURES**

- Compliant with UTOPIA Level 1 and 2 with 8 or 16 Bit Interface Specification and supports UTOPIA Bus speeds of up to 50 MHz

- Contains on-chip 16 cell FIFO in both the Transmit (TxFIFO) and Receive Directions (RxFIFO)

- Contains on-chip 54 byte Transmit OAM Cell buffer and a 108 byte Receive OAM cell buffer, for transmission, reception and processing of OAM cells.

- Supports PLCP or ATM Direct Mapping modes

- · Supports M13 and C-Bit Parity Framing Formats

- Supports DS3 Clear Channel Framing Applications

- Includes PRBS Generator and Receiver

- Supports Local, Remote-Line, Cell, and PLCP Loop-backs

- Interfaces to 8 or 16 Bit wide Motorola and Intel μPs

- Low power 3.3V, 5V input tolerant, CMOS

- · 160 pin PQFP Package

- · 3 and 4 Channel Version also Available

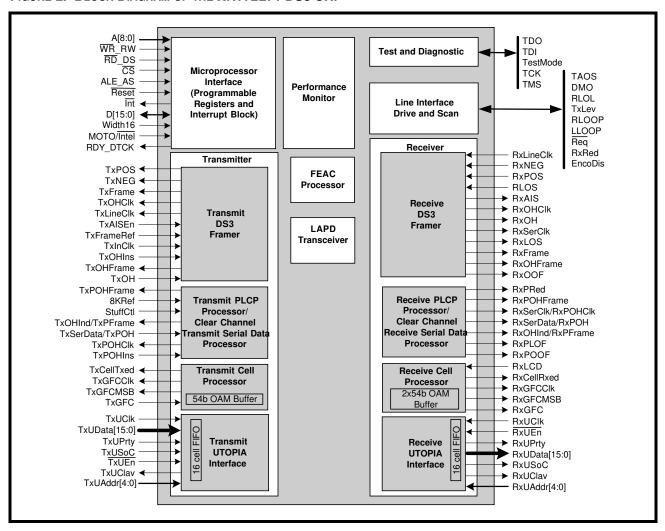

FIGURE 2. BLOCK DIAGRAM OF THE XRT72L71 DS3 UNI

#### ORDERING INFORMATION

| PART NUMBER | PACKAGE  | OPERATING TEMPERATURE RANGE |

|-------------|----------|-----------------------------|

| XRT72L71IQ  | 160 PQFP | -40°C to +85°C              |

# **TABLE OF CONTENTS**

| GENERAL DESCRIPTION                                                                                | 1        |

|----------------------------------------------------------------------------------------------------|----------|

| APPLICATIONS                                                                                       |          |

| FEATURES                                                                                           |          |

| Figure 1. XRT72L71 Simplified Block Diagram with System Interfaces                                 | 1        |

| Figure 2. Block Diagram of the XRT72L71 DS3 UNI                                                    |          |

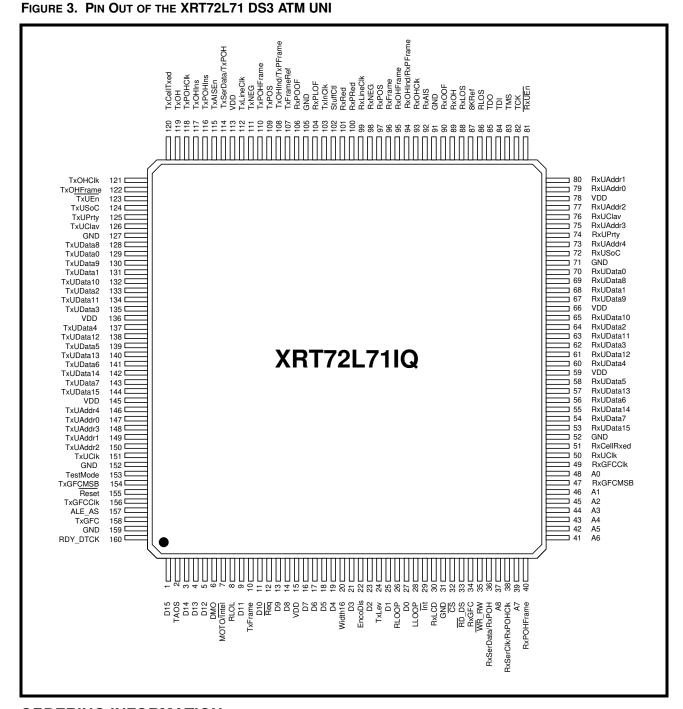

| Figure 3. Pin Out of the XRT72L71 DS3 ATM UNI                                                      |          |

| ORDERING INFORMATION                                                                               | 3        |

| TABLE OF CONTENTS                                                                                  | <i>I</i> |

| Pin Descriptions (see Figure 3)                                                                    |          |

| PIN DESCRIPTION                                                                                    |          |

| ABSOLUTE MAXIMUM RATINGS                                                                           | 23       |

| DC ELECTRICAL CHARACTERISTICS                                                                      | 23       |

| AC ELECTRICAL CHARACTERISTICS                                                                      | 23       |

| TIMING DIAGRAMS                                                                                    |          |

| Figure 4. XRT72L71 Transmit UTOPIA Interface Block Timing                                          |          |

| Figure 5. GFC Nibble-Field Serial Input Interface (at Transmit Cell Processor) Timing              |          |

| Figure 6. Transmit PLCP Processor—POH Byte Serial Input Port Interface Timing                      |          |

| Figure 7. Transmit DS3 Framer—OH Bit Serial Input Port Interface Timing                            |          |

| Figure 8. Transmit DS3 Framer Line Interface Output Timing (TxPOS and TxNEG are updated on the ris |          |

| edge of TxLineClk)                                                                                 |          |

| Figure 9. Transmit DS3 Framer Line Interface Output Timing (TxPOS and TxNEG are updated on the fa  |          |

| edge of TxLineClk)                                                                                 | _        |

| Figure 10. Receive DS3 Framer—OH Bit Serial Output Port Interface Timing                           |          |

| Figure 11. Receive DS3 Framer Line Interface Input Signal Timing (RxPOS and RxNEG are sampled on   | rising   |

| edge of RxLineClk)                                                                                 |          |

| Figure 12. Receive DS3 Framer Line Interface Input Signal Timing (RxPOS and RxNEG are sampled or   |          |

| falling edge of RxLineClk)                                                                         |          |

| Figure 13. Receive PLCP Processor—POH Byte Serial Output Port Interface Timing                     |          |

| Figure 14. GFC Nibble-Field Serial Output Port Timing (Receive Cell Processor)                     |          |

| Figure 15. Receive UTOPIA Interface Block Timing                                                   |          |

| Figure 16. Microprocessor Interface Timing - Intel Type Programmed I/O Read Operations             |          |

| Figure 19. Microprocessor Interface Timing - Intel Type Programmed I/O Write Operations            |          |

| Figure 18. Microprocessor Interface Timing—Motorola Type Processors (Read Operations) Non-Burst N  | noue .   |

| Figure 19. Microprocessor Interface Timing—Motorola Type Processor (Write Operations) Non-Burst Mo | odo      |

| 35                                                                                                 | Jue      |

| Figure 20. Microprocessor Interface Timing - Reset Pulse Width                                     | 35       |

| FUNCTIONAL DESCRIPTION                                                                             |          |

| THE ATM UNI MODE OF OPERATION                                                                      |          |

| The Receive Section                                                                                |          |

|                                                                                                    |          |

| The Transmit Section                                                                               |          |

| Clear-channel-framing Mode of operation                                                            |          |

| THE RECEIVE SECTION                                                                                |          |

| THE TRANSMIT SECTION                                                                               |          |

| The Microprocessor Interface Section                                                               |          |

| Performance Monitor Section                                                                        |          |

| Test and Diagnostic Section                                                                        |          |

| FOR ATM UNI APPLICATIONS                                                                           |          |

| FOR CLEAR-CHANNEL FRAMING APPLICATIONS                                                             |          |

| Line Interface Drive and Scan Section                                                              | . 40     |

| CLEAR CHANNEL MODE OPERATION                                                 |      |

|------------------------------------------------------------------------------|------|

| Features 4                                                                   |      |

| Transmit and Receive Sections 4                                              | ļ1   |

| UTOPIA Interface Blocks                                                      |      |

| Transmit Cell Processor Block                                                | 42   |

| Receive Cell Processor Block                                                 |      |

| Transmit PLCP Processor Block                                                | 42   |

| Receive PLCP Processor Block                                                 |      |

| Transmit/Receive DS3 Framer Block                                            |      |

| Microprocessor Interface Section                                             | 42   |

| Performance Monitor Section                                                  |      |

| Test and Diagnostic Section                                                  |      |

| Line Interface Drive and Scan Section                                        |      |

| LIST OF REGISTERS                                                            | 44   |

| REGISTER SUMMARY LIST                                                        | . 44 |

| Table 1: UNI Operating Mode Register                                         | . 46 |

| Table 2: UNI I/O Control Register                                            | . 47 |

| Table 3: Part Number Register                                                | . 47 |

| Table 4: Version Number Register                                             |      |

| Table 5: UNI Interrupt Enable Register                                       | . 48 |

| Table 6: UNI Interrupt Status Register                                       |      |

| Table 7: Test Cell Control and Status Register                               |      |

| Table 8: Test Cell Error Accumulator Holding Register                        |      |

| Table 9: Test Cell Header Byte-1                                             |      |

| Table 10: Test Cell Header Byte-2                                            |      |

| Table 11: Test Cell Header Byte-3                                            |      |

| Table 12: Test Cell Header Byte-4                                            |      |

| Table 13: Test Cell Error Accumulator - MSB                                  |      |

| Table 14: Test Cell Error Accumulator - LSB                                  |      |

| Table 15: Rx DS3 Configuration and Status Register                           |      |

| Table 16: RxDS3 Status Register                                              |      |

| Table 17: Rx DS3 Interrupt Enable Register                                   |      |

| Table 18: Rx DS3 Interrupt Status Register                                   |      |

| Table 19: Rx DS3 FEAC Register                                               |      |

| TABLE 20: RX DS3 FEAC INTERRUPT ENABLE/STATUS REGISTER                       |      |

| TABLE 21: RX DS3 LAPD CONTROL REGISTER                                       |      |

| TABLE 22: RX DS3 LAPD STATUS REGISTER                                        |      |

| Table 23: Tx DS3 Configuration Register                                      |      |

| Table 24: Tx DS3 M-Bit Mask Register                                         |      |

| Table 25: Tx DS3 F-Bit Mask1 Register                                        |      |

| Table 26: Tx Ds3 F-Bit Mask2 Register                                        |      |

| Table 27: Tx DS3 F-Bit Mask3 Register                                        |      |

| Table 28: Tx DS3 F-Bit Mask4 Register                                        |      |

| TABLE 29: TX DS3 FEAC CONFIGURATION AND STATUS REGISTER                      | -    |

| TABLE 31: TX DS3 FEAC REGISTER  TABLE 31: TX DS3 LAPD CONFIGURATION REGISTER |      |

| TABLE 31: TX DS3 LAPD CONFIGURATION REGISTER                                 |      |

| TABLE 32: TX DS3 LAPD STATUS/INTERRUPT REGISTER                              |      |

| TABLE 33: PMON LCV EVENT COUNT REGISTER - NISB                               |      |

| TABLE 35: PMON FRAMING BIT ERROR EVENT COUNT REGISTER - LSB                  |      |

| TABLE 35: PMON FRAMING BIT ERROR EVENT COUNT REGISTER - MISS                 |      |

| TABLE 30: 1 MON PRINTERFOR COUNT REGISTER - MSB                              |      |

| TABLE 37: 1 MON P-BIT ERROR COUNT REGISTER - MSD                             |      |

| TABLE 39: PMON FEBE EVENT COUNT REGISTER - MSB                               |      |

|                                                                              | . 55 |

| TABLE 40: PMON FEBE EVENT COUNT REGISTER - LSB                                                                                                                                                                                                                                                                                                                                                                                                                   | 66                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| TABLE 41: PMON PLCP BIP-8 ERROR COUNT REGISTER - MSB                                                                                                                                                                                                                                                                                                                                                                                                             | 66                                           |

| TABLE 42: PMON PLCP BIP-8 ERROR COUNT REGISTER - LSB                                                                                                                                                                                                                                                                                                                                                                                                             | 66                                           |

| TABLE 43: PMON PLCP FRAMING BYTE ERROR COUNT REGISTER - MSB                                                                                                                                                                                                                                                                                                                                                                                                      | 66                                           |

| TABLE 44: PMON PLCP FRAMING BYTE ERROR COUNT REGISTER - LSB                                                                                                                                                                                                                                                                                                                                                                                                      | 67                                           |

| TABLE 45: PMON PLCP FEBE COUNT REGISTER - MSB                                                                                                                                                                                                                                                                                                                                                                                                                    | 67                                           |

| TABLE 46: PMON PLCP FEBE COUNT REGISTER -LSB                                                                                                                                                                                                                                                                                                                                                                                                                     | 67                                           |

| TABLE 47: PMON SINGLE-BIT HEC ERROR COUNT - MSB                                                                                                                                                                                                                                                                                                                                                                                                                  |                                              |

| TABLE 48: PMON SINGLE-BIT HEC ERROR COUNT - LSB                                                                                                                                                                                                                                                                                                                                                                                                                  | 68                                           |

| TABLE 49: PMON MULTIPLE-BIT HEC ERROR COUNT - MSB                                                                                                                                                                                                                                                                                                                                                                                                                | 68                                           |

| TABLE 50: PMON MULTIPLE-BIT HEC ERROR COUNT - LSB                                                                                                                                                                                                                                                                                                                                                                                                                |                                              |

| TABLE 51: PMON RECEIVED IDLE CELL COUNT/PRBS ERROR COUNT - MSB                                                                                                                                                                                                                                                                                                                                                                                                   | 68                                           |

| TABLE 52: PMON RECEIVED IDLE CELL COUNT/PRBS ERROR COUNT - LSB                                                                                                                                                                                                                                                                                                                                                                                                   | 69                                           |

| TABLE 53: PMON RECEIVE VALID CELL COUNT - MSB                                                                                                                                                                                                                                                                                                                                                                                                                    |                                              |

| TABLE 54: PMON RECEIVE VALID CELL COUNT - LSB                                                                                                                                                                                                                                                                                                                                                                                                                    |                                              |

| TABLE 55: PMON DISCARDED CELL COUNT - MSB                                                                                                                                                                                                                                                                                                                                                                                                                        |                                              |

| TABLE 56: PMON DISCARDED CELL COUNT - LSB                                                                                                                                                                                                                                                                                                                                                                                                                        |                                              |

| TABLE 57: PMON TRANSMIT IDLE CELL COUNT - MSB                                                                                                                                                                                                                                                                                                                                                                                                                    |                                              |

| TABLE 58: PMON TRANSMIT IDLE CELL COUNT - LSB                                                                                                                                                                                                                                                                                                                                                                                                                    |                                              |

| TABLE 59: PMON TRANSMIT VALID CELL COUNT - MSB                                                                                                                                                                                                                                                                                                                                                                                                                   |                                              |

| TABLE 60: PMON TRANSMIT VALID CELL COUNT - LSB                                                                                                                                                                                                                                                                                                                                                                                                                   |                                              |

| Table 61: PMON Holding Register                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                              |

| Table 62: One Second Error Status Register                                                                                                                                                                                                                                                                                                                                                                                                                       |                                              |

| TABLE 63: LCV - ONE SECOND ACCUMULATOR REGISTER - MSB                                                                                                                                                                                                                                                                                                                                                                                                            |                                              |

| TABLE 64: LCV - ONE SECOND ACCUMULATOR REGISTER - LSB                                                                                                                                                                                                                                                                                                                                                                                                            |                                              |

| TABLE 65: P-BIT ERRORS - ONE SECOND ACCUMULATOR REGISTER - MSB                                                                                                                                                                                                                                                                                                                                                                                                   |                                              |

| Table 66: P-Bit Errors - One Second Accumulator Register - LSB                                                                                                                                                                                                                                                                                                                                                                                                   |                                              |

| Table 67: HEC Byte Errors - One Second Accumulator Register - MSB                                                                                                                                                                                                                                                                                                                                                                                                |                                              |

| Table 68: HEC Byte Errors - One Second Accumulator Register -LSB                                                                                                                                                                                                                                                                                                                                                                                                 |                                              |

| Table 69: Rx PLCP Configuration/Status Register                                                                                                                                                                                                                                                                                                                                                                                                                  |                                              |

| Table 70: Rx PLCP Interrupt Enable Register                                                                                                                                                                                                                                                                                                                                                                                                                      |                                              |

| Table 71: Rx PLCP Interrupt Status Register                                                                                                                                                                                                                                                                                                                                                                                                                      |                                              |

| TABLE 72: FUTURE USE                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                              |

| TABLE 73: TX PLCP FA1 BYTE ERROR MASK REGISTER                                                                                                                                                                                                                                                                                                                                                                                                                   |                                              |

| Table 74: Tx PLCP FA2 Byte Error Mask Register                                                                                                                                                                                                                                                                                                                                                                                                                   |                                              |

| TABLE 75: Tx PLCP BIP-8 ERROR MASK                                                                                                                                                                                                                                                                                                                                                                                                                               |                                              |

| TABLE 76: TX PLCP G1 BYTE REGISTER                                                                                                                                                                                                                                                                                                                                                                                                                               |                                              |

| TABLE 77: RX CP CONFIGURATION REGISTER                                                                                                                                                                                                                                                                                                                                                                                                                           | _                                            |

| Table 78: Rx CP Additional Configuration Register                                                                                                                                                                                                                                                                                                                                                                                                                |                                              |

| Table 79: Rx CP Interrupt Enable Register                                                                                                                                                                                                                                                                                                                                                                                                                        |                                              |

| Table 80: Rx CP Interrupt Status Register                                                                                                                                                                                                                                                                                                                                                                                                                        |                                              |

| TABLE 81: RX CP IDLE CELL PATTERN HEADER BYTE-1                                                                                                                                                                                                                                                                                                                                                                                                                  |                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                              |

| TABLE 82: BX GP IDLE GELL PATTERN HEADER BYTE-2                                                                                                                                                                                                                                                                                                                                                                                                                  | 80                                           |

| TABLE 82: RX CP IDLE CELL PATTERN HEADER BYTE-3                                                                                                                                                                                                                                                                                                                                                                                                                  |                                              |

| TABLE 83: RX CP IDLE CELL PATTERN HEADER BYTE-3                                                                                                                                                                                                                                                                                                                                                                                                                  | 80                                           |

| TABLE 83: RX CP IDLE CELL PATTERN HEADER BYTE-3                                                                                                                                                                                                                                                                                                                                                                                                                  | 80<br>80                                     |

| TABLE 83: RX CP IDLE CELL PATTERN HEADER BYTE-3                                                                                                                                                                                                                                                                                                                                                                                                                  | 80<br>80<br>81                               |

| TABLE 83: RX CP IDLE CELL PATTERN HEADER BYTE-3  TABLE 84: RX CP IDLE CELL PATTERN HEADER BYTE-4  TABLE 85: RX CP IDLE CELL MASK HEADER BYTE-1  TABLE 86: RX CP IDLE CELL MASK HEADER BYTE-2                                                                                                                                                                                                                                                                     | 80<br>80<br>81<br>81                         |

| TABLE 83: RX CP IDLE CELL PATTERN HEADER BYTE-3  TABLE 84: RX CP IDLE CELL PATTERN HEADER BYTE-4  TABLE 85: RX CP IDLE CELL MASK HEADER BYTE-1  TABLE 86: RX CP IDLE CELL MASK HEADER BYTE-2  TABLE 87: RX CP IDLE CELL MASK HEADER BYTE-3                                                                                                                                                                                                                       | 80<br>80<br>81<br>81<br>82                   |

| TABLE 83: RX CP IDLE CELL PATTERN HEADER BYTE-3  TABLE 84: RX CP IDLE CELL PATTERN HEADER BYTE-4  TABLE 85: RX CP IDLE CELL MASK HEADER BYTE-1  TABLE 86: RX CP IDLE CELL MASK HEADER BYTE-2  TABLE 87: RX CP IDLE CELL MASK HEADER BYTE-3  TABLE 88: RX CP IDLE CELL MASK HEADER BYTE-4                                                                                                                                                                         | 80<br>80<br>81<br>81<br>82<br>82             |

| TABLE 83: RX CP IDLE CELL PATTERN HEADER BYTE-3  TABLE 84: RX CP IDLE CELL PATTERN HEADER BYTE-4  TABLE 85: RX CP IDLE CELL MASK HEADER BYTE-1  TABLE 86: RX CP IDLE CELL MASK HEADER BYTE-2  TABLE 87: RX CP IDLE CELL MASK HEADER BYTE-3  TABLE 88: RX CP IDLE CELL MASK HEADER BYTE-4  TABLE 89: RX CP USER CELL FILTER PATTERN HEADER BYTE-1                                                                                                                 | 80<br>80<br>81<br>81<br>82<br>82<br>82       |

| TABLE 83: RX CP IDLE CELL PATTERN HEADER BYTE-3  TABLE 84: RX CP IDLE CELL PATTERN HEADER BYTE-4  TABLE 85: RX CP IDLE CELL MASK HEADER BYTE-1  TABLE 86: RX CP IDLE CELL MASK HEADER BYTE-2  TABLE 87: RX CP IDLE CELL MASK HEADER BYTE-3  TABLE 88: RX CP IDLE CELL MASK HEADER BYTE-4  TABLE 89: RX CP USER CELL FILTER PATTERN HEADER BYTE-1  TABLE 90: RX CP USER CELL FILTER PATTERN HEADER BYTE-2                                                         | 80<br>81<br>81<br>82<br>82<br>82<br>83       |

| TABLE 83: RX CP IDLE CELL PATTERN HEADER BYTE-3  TABLE 84: RX CP IDLE CELL PATTERN HEADER BYTE-4  TABLE 85: RX CP IDLE CELL MASK HEADER BYTE-1  TABLE 86: RX CP IDLE CELL MASK HEADER BYTE-2  TABLE 87: RX CP IDLE CELL MASK HEADER BYTE-3  TABLE 88: RX CP IDLE CELL MASK HEADER BYTE-4  TABLE 89: RX CP USER CELL FILTER PATTERN HEADER BYTE-1  TABLE 90: RX CP USER CELL FILTER PATTERN HEADER BYTE-2  TABLE 91: RX CP USER CELL FILTER PATTERN HEADER BYTE-3 | 80<br>81<br>81<br>82<br>82<br>82<br>83<br>83 |

| TABLE 83: RX CP IDLE CELL PATTERN HEADER BYTE-3  TABLE 84: RX CP IDLE CELL PATTERN HEADER BYTE-4  TABLE 85: RX CP IDLE CELL MASK HEADER BYTE-1  TABLE 86: RX CP IDLE CELL MASK HEADER BYTE-2  TABLE 87: RX CP IDLE CELL MASK HEADER BYTE-3  TABLE 88: RX CP IDLE CELL MASK HEADER BYTE-4  TABLE 89: RX CP USER CELL FILTER PATTERN HEADER BYTE-1  TABLE 90: RX CP USER CELL FILTER PATTERN HEADER BYTE-2                                                         | 80<br>81<br>81<br>82<br>82<br>82<br>83<br>83 |

| Table 94: Rx CP User Filter Cell Mask Header Byte-2                    | 84         |

|------------------------------------------------------------------------|------------|

| TABLE 95: RX CP USER CELL FILTER MASK HEADER BYTE-3                    | 84         |

| TABLE 96: RX CP USER CELL FILTER MASK HEADER BYTE-4                    | 84         |

| TABLE 97: TX CP CONTROL REGISTER                                       | 85         |

| TABLE 98: Tx CP OAM REGISTER                                           | 86         |

| TABLE 99: Tx CP HEC ERROR MASK REGISTER                                | 86         |

| TABLE 100: FUTURE USE                                                  |            |

| TABLE 101: Tx CP IDLE CELL PATTERN HEADER BYTE-1                       | 86         |

| TABLE 102: Tx CP IDLE CELL PATTERN HEADER BYTE-2                       | 87         |

| TABLE 103: Tx CP IDLE CELL PATTERN HEADER BYTE-3                       | 87         |

| TABLE 104: Tx CP IDLE CELL PATTERN HEADER BYTE-4                       | 87         |

| TABLE 105: Tx CP IDLE CELL PATTERN HEADER BYTE-5                       | 87         |

| TABLE 106: Tx CP IDLE CELL PAYLOAD REGISTER                            | 87         |

| TABLE 107: UTOPIA CONFIGURATION REGISTER                               | 88         |

| TABLE 108: RX UTOPIA INTERRUPT ENABLE/STATUS REGISTER                  | 89         |

| TABLE 109: RX UTOPIA ADDRESS                                           | 89         |

| TABLE 110: RX UTOPIA FIFO STATUS REGISTER                              | 90         |

| TABLE 111: TX UTOPIA INTERRUPT/STATUS REGISTER                         | 91         |

| TABLE 112: FUTURE USE                                                  | 91         |

| TABLE 113: TX UTOPIA ADDRESS                                           | 92         |

| TABLE 114: TX UTOPIA STATUS REGISTER                                   | 92         |

| TABLE 115: LINE INTERFACE DRIVE REGISTER                               | 93         |

| TABLE 116: LINE INTERFACE SCAN REGISTER                                | 95         |

| TABLE 117: PMON CP-BIT ERROR EVENT COUNT REGISTER - MSB                | 96         |

| TABLE 118: PMON CP-Bit Error Event Count Register - LSB                | 96         |

| TABLE 119: FRAME CP-BIT ERRORS - ONE SECOND ACCUMULATOR REGISTER - MSB | 96         |

| TABLE 120: FRAME CP-BIT ERRORS - ONE SECOND ACCUMULATOR REGISTER - LSB | 96         |

| TABLE 121: UNUSED                                                      | 96         |

| PACKAGE DIMENSIONS                                                     | <b>9</b> 7 |

| DEVICION HISTORY                                                       | <u>Λ</u> α |

## PIN DESCRIPTIONS (SEE FIGURE 3)

#### **PIN DESCRIPTION**

| Pin No.     | SYMBOL            | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------|-------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1           | D15               | I/O  | MSB of Bi-Directional Data Bus (Microprocessor Interface Section): This pin, along with pins D0 - D14, function as the Microprocessor Interface bi-directional data bus, and is intended to be interfaced to the "local" microprocessor. This pin is inactive if the Microprocessor Interface block is configured to operate over an 8 bit data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2           | TAOS              | 0    | "Transmit All Ones Signal" (TAOS) Command (for the XRT7300 LIU IC). This output pin is intended to be connected to the TAOS input pin of the XRT7300 LIU IC. The user can control the state of this output pin by writing a '0' or '1' to Bit 4 (TAOS) within the Line Interface Drive Register (Address = 0x72). If the user commands this signal to toggle "High" then it will force the XRT7300 DS3 Line Transmitter IC to transmit an "All Ones" pattern onto the line. Conversely, if the user commands this output signal to toggle "Low" then the XRT7300 DS3 Line Transmitter IC will proceed to transmit data based upon the pattern that it receives via the TxPOS and TxNEG output pins. Writing a "1" to Bit 4 of the Line Interface Drive Register (Address = 0x72) will cause this output pin to toggle "High". Writing a "0" to this bit-field will cause this output pin to toggle "Low".  **Note:* If the designer is not using the XRT7300 DS3/E3/STS-1 LIU IC, then this output pin can be used for other purposes. |

| 3<br>4<br>5 | D14<br>D13<br>D12 | I/O  | <b>Bi-directional Data bus (Microprocessor Interface Section):</b> This pin is inactive if the Microprocessor Interface block is configured to operate over an 8 bit data bus. Please see description for D15, pin 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 6           | DMO               | I    | "Drive Monitor Output" Input (from the XRT7300 LIU IC): This input pin is intended to be tied to the DMO output pin of the XRT7300 E3/DS3/STS-1 LIU IC. The user can determine the state of this input pin by reading Bit 2 (DMO) within the Line Interface Scan Register (Address = $0x73$ ). If this input signal is "High", then it means that the drive monitor circuitry (within the XRT7300 LIU IC) has not detected any bipolar signals at the MTIP and MRING inputs within the last $128 \pm 32$ bit-periods. If this input signal is "Low", then it means that bipolar signals are being detected at the MTIP and MRING input pins of the XRT7300.  Note: If the designer is not using the XRT7300 E3/DS3/STS-1 LIU IC, then this input pin can be used for other purposes.                                                                                                                                                                                                                                                   |

| 7           | MOTO/Intel        | I    | Motorola/Intel Processor Interface Select Mode: This input pin allows the user to configure the Microprocessor Interface to interface with either a "Motorola-type" or "Intel-type" microprocessor/microcontroller. Tying this input pin to VDD, configures the microprocessor interface to operate in the Motorola mode (e.g., the UNI/Framer can be readily interfaced to a "Motorola type" local microprocessor). Tying this input pin to GND configures the microprocessor interface to operate in the Intel Mode (e.g., the UNI/Framer can be readily interfaced to an "Intel type" local microprocessor).                                                                                                                                                                                                                                                                                                                                                                                                                        |

| PIN No. | SYMBOL  | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------|---------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8       | RLOL    | I    | Receive Loss of Lock Indicator—from the XRT7300 E3/DS3/STS-1 LIU IC: This input pin is intended to be connected to the RLOL (Receive Loss of Lock) output pin of the XRT7300 LIU IC. The user can monitor the state of this pin by reading the state of Bit 1 (RLOL) within the Line Interface Scan Register (Address = 0x73). If this input pin is "Low", then it means that the phase-locked-loop circuitry, within the XRT7300 is properly locked onto the incoming DS3 data-stream; and is properly recovering clock and data from this DS3 data-stream. However, if this input pin is "High", then it means that the phase-locked-loop circuitry, within the XRT7300 has lost lock with the incoming DS3 data-stream, and is not properly recovering clock and data. For more information on the operation of the XRT7300 E3/DS3/STS-1 LIU IC, please consult the "XRT7300 E3/DS3/STS-1 LIU IC" data sheet.  **Note: If the designer is not using the XRT7300 DS3/E3/STS-1 LIU IC, this input pin can be used for other purposes.**                                                                                                                                                           |

| 9       | D11     | I/O  | <b>Bi-Directional Data bus (Microprocessor Interface Section):</b> This pin is inactive if the Microprocessor Interface block is configured to operate over an 8-bit wide data bus. Please see description for D15, pin 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 10      | TxFrame | 0    | Transmit End of DS3 Frame Indicator: The function of this pin is same in both Clear Channel and ATM UNI modes of the XRT72L71. This pin marks the end of each DS3 frame.  ATM UNI Mode This pin is pulsed for one DS3 clock period when the transmit input interface is processing the last bit of the given DS3 frame. This just serves as an indication to terminal equpiment in the ATM UNI mode.  Clear Channel Mode When the XRT72L71 is configured to operate in the "Clear-Channel Framer" mode, then the Transmit DS3 Framer block will pulse this output pin "High" (for one bit period) when the "Transmit Payload Data Input Interface" block is processing the last bit of a given DS3 frame.  The purpose of this output pin is to alert the Terminal Equipment that it needs to begin transmission of a new DS3 frame to the XRT72L71 (e.g., to permit the XRT72L71 to maintain Transmit DS3 framing alignment control over the Terminal Equipment).                                                                                                                                                                                                                                 |

| 11      | D10     | I/O  | <b>Bi-Directional Data bus (Microprocessor Interface Section):</b> This pin is inactive if the Microprocessor Interface block is configured to operate over an 8 bit data bus. (Please see description for D15, pin 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 12      | Req     | 0    | Receive Equalization Bypass Control Output Pin—(to be connected to the XRT7300 E3/DS3/STS-1 LIU IC): This output pin is intended to be connected to the Req input pin of the XRT7300 E3/DS3/STS-1 LIU IC. The user can control the state of this output pin by writing a '0' or '1' to Bit 5 (Req) of the Line Interface Driver Register (Address = 0x72). If the user commands this signal to toggle "High" then it will cause the incoming DS3 line signal to "bypass" equalization circuitry, within the XRT7300. Conversely, if the user commands this output signal to toggle "Low", then the incoming DS3 line signal with be routed through the equalization circuitry. For information on the criteria that should be used when deciding whether to bypass the equalization circuitry or not, please consult the "XRT7300 E3/DS3/STS-1 LIU IC" data sheet. Writing a "1" to Bit 5 of the Line Interface Drive Register (Address = 0x72) will cause this output pin to toggle "High". Writing a "0" to this bit-field will cause this output pin to toggle "Low".  Note: If the designer is not using the XRT7300 E3/DS3/STS-1 LIU IC, then this output pin can be used for other purposes. |

| Pin No.              | SYMBOL               | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------|----------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13                   | D9                   | I/O  | <b>Bi-Directional Data bus (Microprocessor Interface Section):</b> This pin is inactive if the Microprocessor Interface block is configured to operate over an 8 bit data bus. Please see description for D15, pin1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 14                   | D8                   | I/O  | <b>Bi-Directional Data bus (Microprocessor Interface Section):</b> This pin is inactive if the Microprocessor Interface block is configured to operate over an 8 bit data bus. Please see description for D15, pin1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 15                   | VDD                  | ***  | Power Supply Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 16<br>17<br>18<br>19 | D7<br>D6<br>D5<br>D4 | I/O  | Bi-Directional Data bus (Microprocessor Interface Section): Please see description for D15, pin 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 20                   | Width16              | I    | Microprocessor Interface Block Data Bus Width Selector: This input pin permits the user to configure the microprocessor interface of the UNI/Framer, to operate over either an 8 or 16 bit wide bi-directional data bus. Tying this pin to VDD configures the Microprocessor Interface Data Bus width to be 16 bits. Tying this pin to GND configures the Microprocessor Interface Data Bus width to be 8 bits.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 21                   | D3                   | I/O  | Bi-Directional Data bus (Microprocessor Interface Section): Please see description for D15, pin 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 22                   | EncoDis              | 0    | Encoder (B3ZS) Disable Output pin (intended to be connected to the XRT7300 E3/DS3/STS-1 LIU IC): This output pin is intended to be connected to the EncoDis input pin of the XRT7300 LIU IC. The user can control the state of this output pin by writing a "0" or "1" to Bit 3 (EncoDis) of the Line Interface Driver Register (Address = 0x72). If the user commands this signal to toggle "High" then it will disable the B3ZS encoder circuitry within the XRT7300 IC. Conversely, if the user commands this output signal to toggle "Low", then the B3ZS Encoder circuitry, within the XRT7300 IC will be enabled. Writing a "1" to Bit 3 of the Line Interface Driver Register (Address = 0x72) will cause this output pin to toggle "High". Writing a "0" to this bit-field will cause this output pin to toggle "Low".  NOTES: |

|                      |                      |      | <ol> <li>The user is advised to disable the B3ZS encoder (within the XRT7300 IC) if the Transmit and Receive DS3 Framers (within the UNI) are configured to operate in the B3ZS line code.</li> <li>If the designer is not using the XRT7300 DS3/E3/STS-1 Line Transmitter IC, then output pin can be used for other purposes.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 23                   | D2                   | I/O  | Bi-Directional Data bus (Microprocessor Interface Section): Please see description for D15, pin1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| PIN No. | SYMBOL | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------|--------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 24      | TxLev  | O    | Transmit Line Build Enable/Disable Select (to be connected to the TxLev input pin of the XRT7300 E3/DS3/STS-1 LIU IC): This output pin is intended to be connected to the TxLev input pin of the XRT7300 E3/DS3/STS-1 LIU IC. The user can control the state of this output pin by writing a "0" or a "1" to Bit 2 (TxLev) within the Line Interface Driver Register (Address = 0x72). If the user commands this signal to toggle "High" then it will disable the "Transmit Line Build-Out" circuitry within the XRT7300. In this case, the XRT7300 will output unshaped (square-wave) pulses onto the "Transmit Line Signal". In order to insure that the XRT7300 generates a line signal that is compliant with the Bellcore GR-499-CORE Pulse Template requirements (at the DSX-3 Cross-Connect), the user is advised to set this output pin "High", if the cable length (between the Transmit Output of the XRT7300 and the DSX-3 Cross-Connect) is greater than 225 feet.  Conversely, if the user commands this signal to toggle "High", then it will enable the "Transmit Line Build-Out" circuitry within the XRT7300. In this case, the XRT7300 will output shaped pulses onto the "Transmit Line Signal". In order to ensure that the XRT7300 generates a line signal that is compliant with the Bellcore GR-499-CORE Pulse Template requirements (at the DSX-3 Cross-Connect), the user is advised to set this output pin "Low", if the cable length (between the Transmit Output of the XRT7300 and the DSX-3 Cross Connect) is less than 225 ft. of cable.  Writing a "1" to Bit 2 of the Line Interface Drive Register (Address = 0x72) will cause this output pin to toggle "High". Writing a "0" to this bit-field will cause this output pin to toggle "How".  Note: If the customer is not using the XRT7300 DS3/E3/STS-1 LIU IC, then this output pin can be used for other purposes. |

| 25      | D1     | I/O  | <b>Bi-Directional Data bus (Microprocessor Interface Section):</b> Please see description for D15, pin1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |