Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

#### E3/DS3/STS-1 LINE INTERFACE UNIT

MAY 2011 REV. 1.1.2

#### GENERAL DESCRIPTION

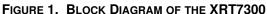

The XRT7300 DS3/E3/STS-1 Line Interface Unit is designed to be used in DS3, E3 or SONET STS-1 applications and consists of a line transmitter and receiver integrated on a single chip.

XRT7300 can be configured to support the E3 (34.368 Mbps), DS3 (44.736 Mbps) or the SONET STS-1 (51.84 Mbps) rates.

In the transmit direction, the XRT7300 encodes input data to either B3ZS (for DS3/STS-1 applications) or HDB3 (for E3 applications) format and converts the data into the appropriate pulse shapes for transmission over coaxial cable via a 1:1 transformer.

In the receive direction the XRT7300 performs equalization on incoming signals, performs Clock Recovery, decodes data from either B3ZS or HDB3 format, converts the receive data into TTL/CMOS format, checks for LOS or LOL conditions and detects and declares the occurrence of line code violations.

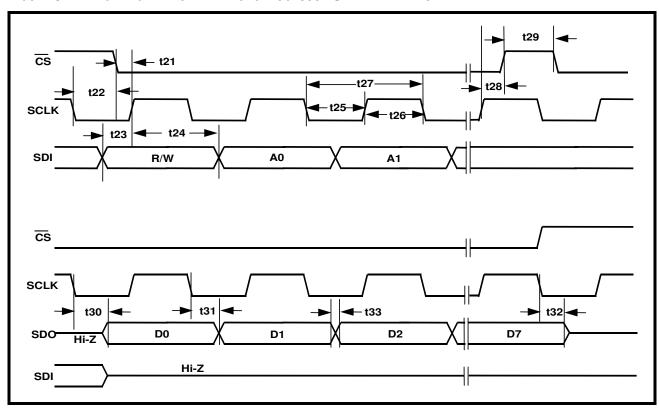

The XRT7300 also contains a 4-Wire Microprocessor Serial Interface for accessing the on-chip Command registers.

#### **FEATURES**

- Meets E3/DS3/STS-1 Jitter Tolerance Requirements

- Full Loop-Back Capability

- · Transmit and Receive Power Down Modes

- Full Redundancy Support

- Contains a 4-Wire Microprocessor Serial Interface

- · Uses Minimum External components

- Requires Single +5V Power Supply

- -40°C to +85°C Operating Temperature Range

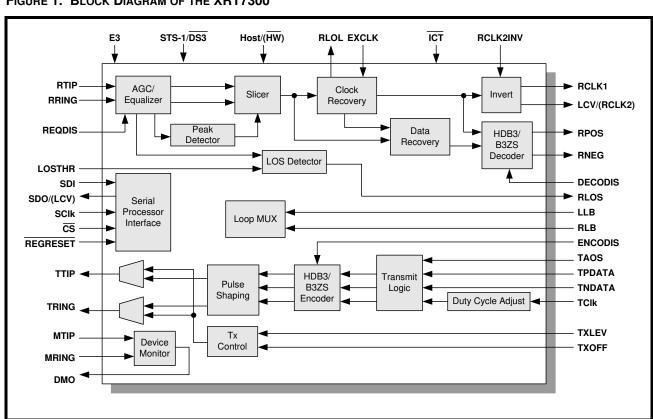

- · Available in a 44 pin TQFP package

#### APPLICATIONS

- Interfaces to E3. DS3 or SONET STS-1 Networks

- CSU/DSU Equipment

- PCM Test Equipment

- · Fiber Optic Terminals

- Multiplexers

NOTE: This Device is Protected by US Patent # 6,157,270

### **ORDERING INFORMATION**

| PART NUMBER | PACKAGE TYPE              | OPERATING TEMPERATURE RANGE |

|-------------|---------------------------|-----------------------------|

| XRT7300IV   | 44 Pin TQFP (10mm x 10mm) | -40°C to +85°C              |

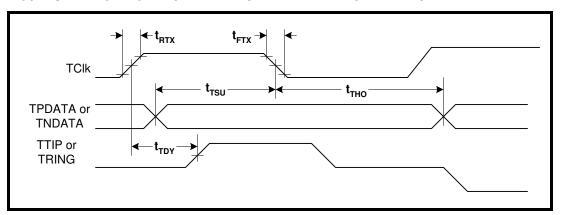

FIGURE 2. PIN OUT OF THE XRT7300 IN THE 44 PIN TQFP

## **TABLE OF CONTENTS**

| General description 1                                                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FEATURES1 APPLICATIONS                                                                                                                                             |

| Figure 1.Block Diagram of the XRT73001                                                                                                                             |

| Ordering Information 2                                                                                                                                             |

| Figure 2.Pin Out of the XRT7300 in the 44 Pin TQFP2                                                                                                                |

| TABLE OF CONTENTS                                                                                                                                                  |

| Pin Description 3                                                                                                                                                  |

| Electrical Characteristics 10                                                                                                                                      |

| DC ELECTRICAL CHARACTERISTICS (TA = 25°C, VDD = 5.0V + 5%, UNLESS OTHERWISE SPECI-FIED)                                                                            |

| AC ELECTRICAL CHARACTERISTICS (TA = 25°C, VDD = 5.0V + 5%, UNLESS OTHERWISE SPECI-FIED)                                                                            |

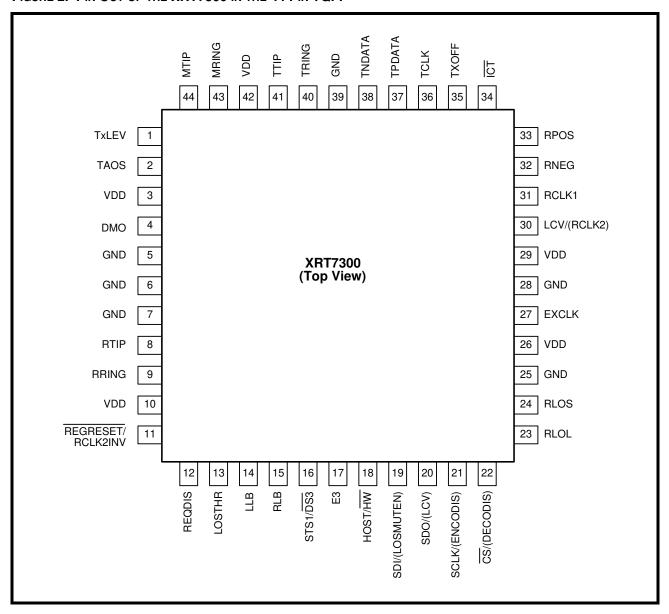

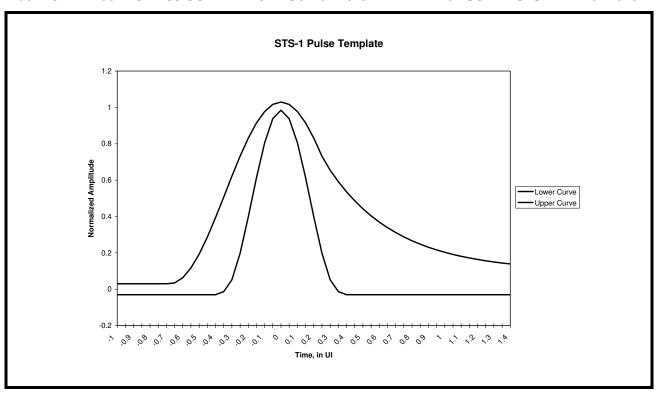

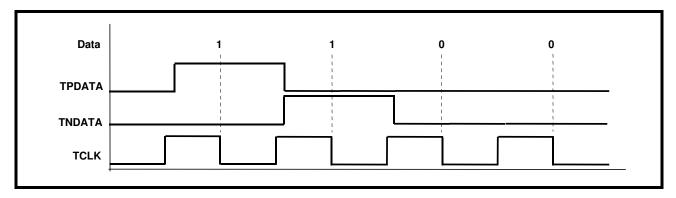

| Figure 3.Timing Diagram of the Transmit Terminal Input Interface                                                                                                   |

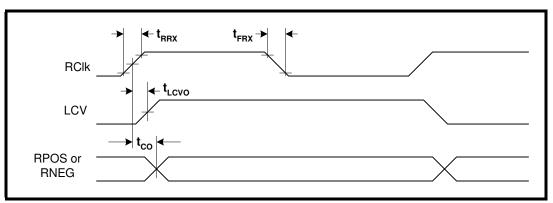

| Figure 4.Timing Diagram of the Receive Terminal Output Interface                                                                                                   |

| AC ELECTRICAL CHARACTERISTICS (CONTINUED) (TA = 25°C, VDD = 5.0V + 5%, UNLESS OTHER-WISE SPECIFIED)                                                                |

| ABSOLUTE MAXIMUM RATINGS14                                                                                                                                         |

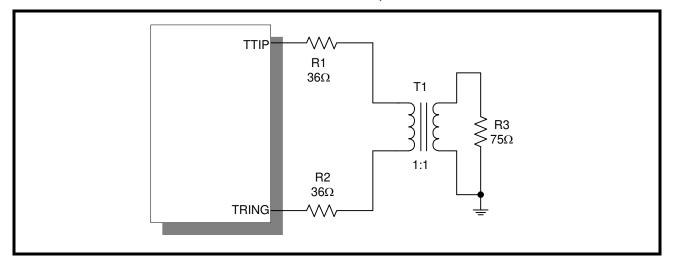

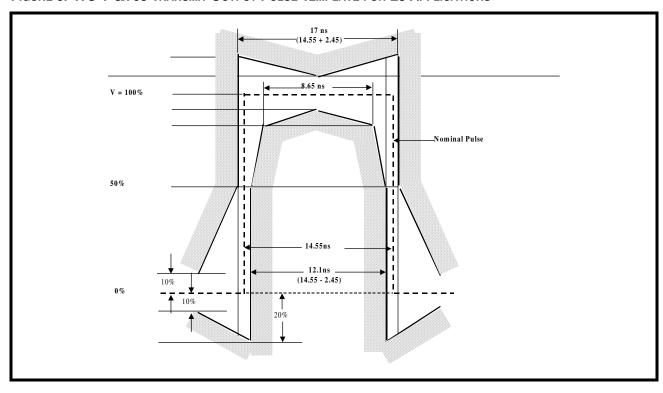

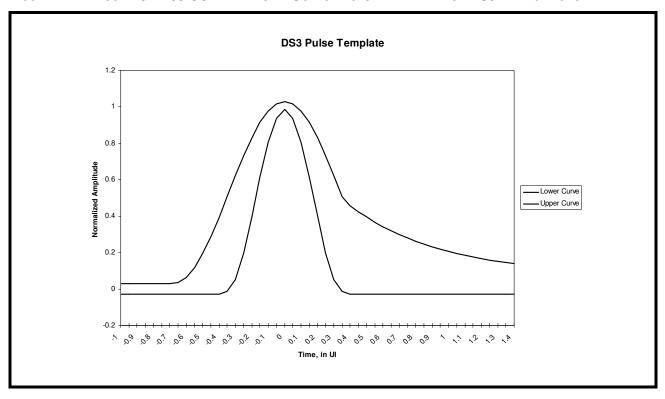

| Figure 5.Transmit Pulse Amplitude Test Circuit for DS3, E3 and STS-1 Rates                                                                                         |

| System Description                                                                                                                                                 |

| THE TRANSMIT SECTION                                                                                                                                               |

| 1.0 SELECTING THE DATA RATE                                                                                                                                        |

| Table 2:Selecting the Data Rate for the XRT7300 via the E3 and STS-1/DS3 input pins (Hardware Mode) 19 COMMAND REGISTER CR4 (ADDRESS = 0X04)                       |

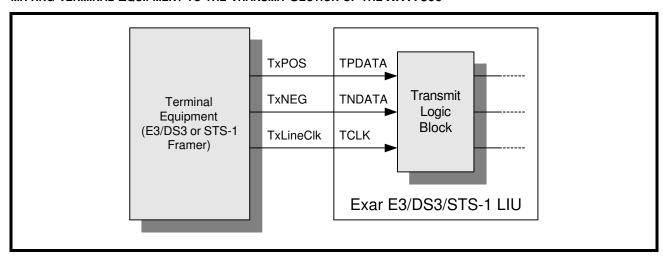

| 2.0 THE TRANSMIT SECTION                                                                                                                                           |

| 2.1 THE TRANSMIT LOGIC BLOCK                                                                                                                                       |

| Figure 10.The Typical Interface for the Transmission of Data in a Dual-Rail Format From the Transmitting Terminal Equipment to the Transmit Section of the XRT7300 |

| Accepting Single-Rail Data from the Terminal Equipment                                                                                                             |

# E3/DS3/STS-1 LINE INTERFACE UNIT

| 2.2 THE TRANSMIT CLOCK DUTY CYCLE ADJUST CIRCUITRY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 21                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 2.3 THE HDB3/B3ZS ENCODER BLOCK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 22                                                 |

| B3ZS Encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 22                                                 |

| Figure 13.An Example of B3ZS Encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 22                                                 |

| HDB3 Encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 22                                                 |

| Figure 14.An Example of HDB3 Encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 23                                                 |

| Enabling/Disabling the HDB3/B3ZS Encoder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 23                                                 |

| COMMAND REGISTER CR2 (ADDRESS = 0X02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                    |

| 2.4 THE TRANSMIT PULSE SHAPER CIRCUITRY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 23                                                 |

| Enabling the Transmit Line Build-Out Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 23                                                 |

| COMMAND REGISTER CR1 (ADDRESS = 0X01)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 23                                                 |

| Disabling the Transmit Line Build-Out Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 23                                                 |

| COMMAND REGISTER CR1 (ADDRESS = 0X01)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 24                                                 |

| Design Guideline for Setting the Transmit Line Build-Out Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 24                                                 |

| The Transmit Line Build-Out Circuit and E3 Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 24                                                 |

| 2.5 Interfacing the Transmit Section of the XRT7300 to the Line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 24                                                 |

| Figure 15.Recommended Schematic for Interfacing the Transmit Section of the XRT7300 to the Line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 24                                                 |

| TRANSFORMER RECOMMENDATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 25                                                 |

| 3.0 THE RECEIVE SECTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 25                                                 |

| 3.1 INTERFACING THE RECEIVE SECTION OF THE XRT7300 TO THE LINE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 25                                                 |

| Figure 16.Recommended Schematic for Interfacing the Receive Section of the XRT7300 to the Line (Transer-Coupling)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                    |

| Figure 17.Recommended Schematic for Interfacing the Receive Section of the XRT7300 to the Line (Cap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                    |

| tive-Coupling)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                    |

| uve-00upinig/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                    |

| 3.2 The Receive Equalizer Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                    |

| 3.2 THE RECEIVE EQUALIZER BLOCK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 26<br>27                                           |

| 3.2 THE RECEIVE EQUALIZER BLOCK  Figure 18. The Typical Application for the System Installer  COMMAND REGISTER CR2 (ADDRESS = 0X02)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 26<br>27                                           |

| 3.2 THE RECEIVE EQUALIZER BLOCK  Figure 18. The Typical Application for the System Installer  COMMAND REGISTER CR2 (ADDRESS = 0X02)  3.3 PEAK DETECTOR AND SLICER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 26<br>27<br>28                                     |

| 3.2 THE RECEIVE EQUALIZER BLOCK  Figure 18. The Typical Application for the System Installer  COMMAND REGISTER CR2 (ADDRESS = 0X02)  3.3 PEAK DETECTOR AND SLICER  3.4 CLOCK RECOVERY PLL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 26<br>27<br>28<br>28                               |

| 3.2 THE RECEIVE EQUALIZER BLOCK  Figure 18. The Typical Application for the System Installer  COMMAND REGISTER CR2 (ADDRESS = 0X02)  3.3 PEAK DETECTOR AND SLICER  3.4 CLOCK RECOVERY PLL  3.5 THE HDB3/B3ZS DECODER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 26<br>28<br>28<br>28                               |

| 3.2 THE RECEIVE EQUALIZER BLOCK  Figure 18. The Typical Application for the System Installer  COMMAND REGISTER CR2 (ADDRESS = 0X02)  3.3 PEAK DETECTOR AND SLICER  3.4 CLOCK RECOVERY PLL  3.5 THE HDB3/B3ZS DECODER  B3ZS Decoding DS3/STS-1 Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 26<br>28<br>28<br>28<br>28                         |

| 3.2 THE RECEIVE EQUALIZER BLOCK  Figure 18. The Typical Application for the System Installer  COMMAND REGISTER CR2 (ADDRESS = 0X02)  3.3 PEAK DETECTOR AND SLICER  3.4 CLOCK RECOVERY PLL  3.5 THE HDB3/B3ZS DECODER  B3ZS Decoding DS3/STS-1 Applications  Figure 19.An Example of B3ZS Decoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 26<br>28<br>28<br>28<br>28<br>29                   |

| 3.2 THE RECEIVE EQUALIZER BLOCK  Figure 18. The Typical Application for the System Installer  COMMAND REGISTER CR2 (ADDRESS = 0X02)  3.3 PEAK DETECTOR AND SLICER  3.4 CLOCK RECOVERY PLL  3.5 THE HDB3/B3ZS DECODER  B3ZS Decoding DS3/STS-1 Applications  Figure 19.An Example of B3ZS Decoding  HDB3 Decoding E3 Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 26<br>28<br>28<br>28<br>29<br>29                   |

| 3.2 THE RECEIVE EQUALIZER BLOCK  Figure 18. The Typical Application for the System Installer  COMMAND REGISTER CR2 (ADDRESS = 0X02)  3.3 PEAK DETECTOR AND SLICER  3.4 CLOCK RECOVERY PLL  3.5 THE HDB3/B3ZS DECODER  B3ZS Decoding DS3/STS-1 Applications  Figure 19.An Example of B3ZS Decoding  HDB3 Decoding E3 Applications  Figure 20.An Example of HDB3 Decoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 26<br>28<br>28<br>28<br>29<br>29                   |