# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## **XRT75L03**

THREE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER ATTENUATOR

#### JULY 2003

**XPEXAR**

#### **GENERAL DESCRIPTION**

The XRT75L03 is a three-channel fully integrated Line Interface Unit (LIU) with Jitter Attenuator for E3/ DS3/STS-1 applications. It incorporates 3 independent Receivers, Transmitters and Jitter Attenuators in a single 128 pin LQFP package.

Each channel of the XRT75L03 can be independently configured to operate in the data rate, E3 (34.368 MHz), DS3 (44.736 MHz) or STS-1 (51.84 MHz). Each transmitter can be turned off and tri-stated for redundancy support or for conserving power.

The XRT75L03's differential receiver provides high noise interference margin and is able to receive the data over 1000 feet of cable or with up to 12 dB of cable attenuation.

The XRT75L03 incorporates an advanced crystalless jitter attenuator per channel that can be selected either in the transmit or receive path. The jitter attenuator performance meets the ETSI TBR-24 and Bellcore GR-499 specifications.

The XRT75L03 provides both Serial Microprocessor Interface as well as Hardware mode for programming and control.

The XRT75L03 supports local, remote and digital loop-backs. The device also has a built-in Pseudo Random Binary Sequence (PRBS) generator and detector with the ability to insert and detect single bit error for diagnostic purposes.

#### FEATURES

#### **RECEIVER:**

- On chip Clock and Data Recovery circuit for high input jitter tolerance

- Meets E3/DS3/STS-1 Jitter Tolerance Requirement

- Detects and Clears LOS as per G.775

- Receiver Monitor mode handles up to 20 dB flat loss with 6 dB cable attenuation

- On chip B3ZS/HDB3 encoder and decoder that can be either enabled or disabled

- On-chip clock synthesizer provides the appropriate rate clock from a single 12.288 MHz Clock

- Provides low jitter output clock

#### TRANSMITTER:

- Compliant with Bellcore GR-499, GR-253 and ANSI T1.102 Specification for transmit pulse

- Tri-state Transmit output capability for redundancy applications

- Each Transmitter can be turned on or off

- Transmitters provide Current Output Drive

#### JITTER ATTENUATOR:

- On chip advanced crystal-less Jitter Attenuator for each channel

- Jitter Attenuator can be selected in Receive or Transmit paths

- Meets ETSI TBR 24 Jitter Transfer Requirements

- Compliant with jitter transfer template outlined in ITU G.751, G.752, G.755 and GR-499-CORE,1995 standards

- 16 or 32 bits selectable FIFO size

- Jitter Attenuator can be disabled

#### CONTROL AND DIAGNOSTICS:

- 5 wire Serial Microprocessor Interface for control and configuration

- Supports optional internal Transmit driver monitoring

- Hardware Mode for control and configuration

- Each channel supports Local, Remote and Digital Loop-backs

- Single 3.3 V ± 5% power supply

- 5 V Tolerant digital inputs

- Available in 128 pin LQFP Package

- - 40°C to 85°C Industrial Temperature Range

#### APPLICATIONS

- E3/DS3 Access Equipment

- DSLAMs

- Digital Cross Connect Systems

- CSU/DSU Equipment

- Routers

- Fiber Optic Terminals

REV. 1.0.4

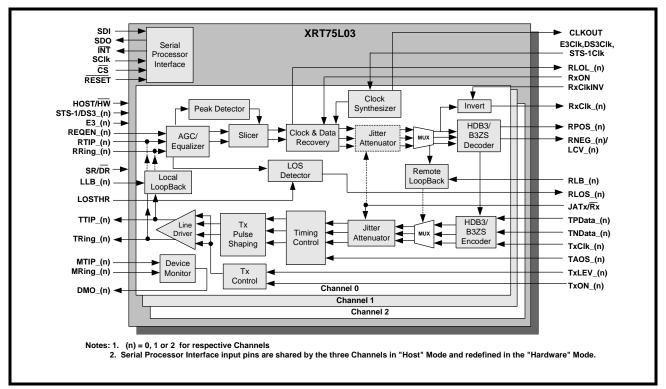

#### FIGURE 1. BLOCK DIAGRAM OF THE XRT 75L03

## TRANSMIT INTERFACE CHARACTERISTICS

- Accepts either Single-Rail or Dual-Rail data from Terminal Equipment and generates a bipolar signal to the line

- Integrated Pulse Shaping Circuit

- Built-in B3ZS/HDB3 Encoder (which can be disabled)

- Accepts Transmit Clock with duty cycle of 30%-70%

- Generates pulses that comply with the ITU-T G.703 pulse template for E3 applications

- Generates pulses that comply with the DSX-3 pulse template, as specified in Bellcore GR-499-CORE and ANSI T1.102\_1993

- Generates pulses that comply with the STSX-1 pulse template, as specified in Bellcore GR-253-CORE

- Transmitter can be turned off in order to support redundancy designs

#### **RECEIVE INTERFACE CHARACTERISTICS**

- Integrated Adaptive Receive Equalization (optional) for optimal Clock and Data Recovery

- Declares and Clears the LOS defect per ITU-T G.775 requirements for E3 and DS3 applications

- Meets Jitter Tolerance Requirements, as specified in ITU-T G.823\_1993 for E3 Applications

- Meets Jitter Tolerance Requirements, as specified in Bellcore GR-499-CORE for DS3 Applications

- Declares Loss of Signal (LOS) and Loss of Lock (LOL) Alarms

- Built-in B3ZS/HDB3 Decoder (which can be disabled)

- Recovered Data can be muted while the LOS Condition is declared

- Outputs either Single-Rail or Dual-Rail data to the Terminal Equipment

XRT75L03 REV. 1.0.4

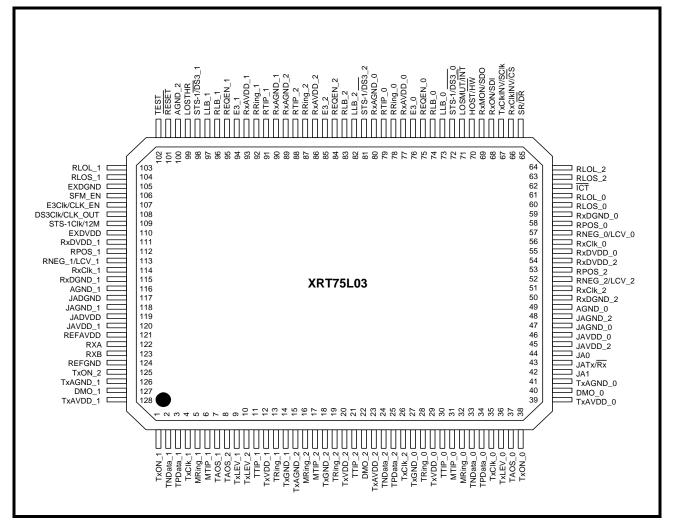

#### FIGURE 2. PIN OUT OF THE XRT75L03

#### ORDERING INFORMATION

| PART NUMBER | Package      | OPERATING TEMPERATURE RANGE |

|-------------|--------------|-----------------------------|

| XRT75L03IV  | 128 Pin LQFP | - 40°C to + 85°C            |

## TABLE OF CONTENTS

| GENERAL DESCRIPTION                                                                              | . 1  |

|--------------------------------------------------------------------------------------------------|------|

| Features                                                                                         | 1    |

| APPLICATIONS                                                                                     |      |

| TRANSMIT INTERFACE CHARACTERISTICS                                                               |      |

| Receive Interface Characteristics                                                                |      |

| Figure 1. Block Diagram of the XRT 75L03                                                         |      |

| Figure 2. Pin Out of the XRT75L03                                                                |      |

| ORDERING INFORMATION                                                                             |      |

| TABLE OF CONTENTS                                                                                |      |

| PIN DESCRIPTIONS (BY FUNCTION)                                                                   | . 4  |

| System-Side Transmit Input and Transmit Control Pins                                             |      |

| TRANSMIT LINE SIDE PINS                                                                          |      |

| SYSTEM-SIDE RECEIVE OUTPUT AND RECEIVE CONTROL PINS                                              |      |

| Receive Line Side Pins                                                                           |      |

| CLOCK INTERFACE                                                                                  |      |

| General Control Pins                                                                             |      |

| Control and Alarm Interface                                                                      |      |

| JITTER ATTENUATOR INTERFACE                                                                      |      |

| Power Supply and Ground Pins                                                                     |      |

| XRT75L03 Pin Listing in Numerical Order                                                          |      |

| 1.0 ELECTRICAL CHARACTERISTICS                                                                   |      |

| TABLE 1: ABSOLUTE MAXIMUM RATINGS                                                                |      |

| TABLE 2: DC ELECTRICAL CHARACTERISTICS:                                                          |      |

| 2.0 TIMING CHARACTERISTICS                                                                       |      |

| Figure 3. Typical interface between terminal equipment and the XRT75L03 (dual-rail data)         |      |

| Figure 4. Transmitter Terminal Input Timing                                                      | 32   |

| Figure 5. Receiver Data output and code violation timing                                         |      |

| Figure 6. Transmit Pulse Amplitude test circuit for E3, DS3 and STS-1 Rates                      |      |

| 3.0 LINE SIDE CHARACTERISTICS:                                                                   |      |

| 3.1 E3 LINE SIDE PARAMETERS:                                                                     |      |

| Figure 7. Pulse Mask for E3 (34.368 mbits/s) interface as per itu-t G.703                        |      |

| TABLE 3: E3 TRANSMITTER LINE SIDE OUTPUT AND RECEIVER LINE SIDE INPUT SPECIFICATIONS             |      |

| Figure 8. Bellcore GR-253 CORE Transmit Output Pulse Template for SONET STS-1 Applications       |      |

| TABLE 4: STS-1 PULSE MASK EQUATIONS                                                              |      |

| TABLE 5: STS-1 TRANSMITTER LINE SIDE OUTPUT AND RECEIVER LINE SIDE INPUT SPECIFICATIONS (GR-253) |      |

| Figure 9. Transmit Ouput Pulse Template for DS3 as per Bellcore GR-499                           |      |

| TABLE 6: DS3 PULSE MASK EQUATIONS                                                                |      |

| TABLE 7: DS3 TRANSMITTER LINE SIDE OUTPUT AND RECEIVER LINE SIDE INPUT SPECIFICATIONS (GR-499)   |      |

| Figure 10. Microprocessor Serial Interface Structure                                             |      |

| Figure 11. Timing Diagram for the Microprocessor Serial Interface                                |      |

| TABLE 8: MICROPROCESSOR SERIAL INTERFACE TIMINGS (TA = 250C, VDD=3.3V± 5% AND LOAD = 10PF)       |      |

| FUNCTIONAL DESCRIPTION:                                                                          |      |

| 4.0 The Transmitter Section:                                                                     |      |

| Figure 12. Single-Rail or NRZ Data Format (Encoder and Decoder are Enabled)                      |      |

| Figure 13. Dual-Rail Data Format (encoder and decoder are disabled)                              |      |

| 4.1 TRANSMIT CLOCK:                                                                              |      |

| 4.2 B3ZS/HDB3 Encoder:                                                                           |      |

| 4.2.1 B3ZS Encoding:                                                                             |      |

| 4.2.2 HDB3 Encoding:                                                                             |      |

| Figure 14. B3ZS Encoding Format                                                                  |      |

| Figure 15. HDB3 Encoding Format                                                                  |      |

| 4.3 TRANSMIT PULSE SHAPER:                                                                       | 43   |

| 4.3.1 Guidelines for using Transmit Build Out Circuit:                                           | . 43 |

#### XRT75L03

| THREE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER ATTENUATOR                                         | 5LU3<br>.1.0.4 |

|---------------------------------------------------------------------------------------------------------------|----------------|

| 4.3.2 Interfacing to the line:                                                                                | 43             |

| 4.4 Transmit Drive Monitor:                                                                                   | 44             |

| 4.5 TRANSMITTER SECTION ON/OFF:                                                                               | 44             |

| 5.0 The Receiver Section:                                                                                     | 44             |

| 5.1 AGC/Equalizer:                                                                                            | 44             |

| Figure 16. Transmit Driver Monitor set-up.                                                                    | 44             |

| 5.1.1 Interference Tolerance:                                                                                 | 45             |

| Figure 17. Interference Margin Test Set up for DS3/STS-1                                                      |                |

| 5.2 CLOCK AND DATA RECOVERY:                                                                                  |                |

| Figure 18. Interference Margin Test Set up for E3.                                                            |                |

| TABLE 9: INTERFERENCE MARGIN TEST RESULTS                                                                     | 46             |

| 5.3 B3ZS/HDB3 DECODER:                                                                                        |                |

| 5.4 LOS (Loss of Signal) DETECTOR:                                                                            |                |

| 5.4.1 DS3/STS-1 LOS Condition:                                                                                |                |

| DISABLING ALOS/DLOS DETECTION:                                                                                |                |

| 5.4.2 E3 LOS Condition:                                                                                       | 47             |

| TABLE 10: THE ALOS (ANALOG LOS) DECLARATION AND CLEARANCE THRESHOLDS FOR A GIVEN SETTING OF                   |                |

| LOSTHR AND REQEN (DS3 AND STS-1 APPLICATIONS)                                                                 |                |

| Figure 19. Loss Of Signal Definition for E3 as per ITU-T G.775                                                | 48             |

| Figure 20. Loss of Signal Definition for E3 as per ITU-T G.775.                                               |                |

| 5.4.3 Muting the Recovered Data with LOS condition:                                                           |                |

| 6.0 Jitter:                                                                                                   |                |

| 6.1 JITTER TOLERANCE - RECEIVER:                                                                              |                |

| 6.1.1 DS3/STS-1 Jitter Tolerance Requirements:                                                                |                |

| Figure 21. Jitter Tolerance Measurements                                                                      |                |

| 6.1.2 E3 Jitter Tolerance Requirements:                                                                       |                |

| Figure 22. Input Jitter Tolerance For DS3/STS-1                                                               |                |

| Figure 23. Input Jitter Tolerance for E3                                                                      | 50             |

| 6.2 JITTER TRANSFER - RECEIVER/TRANSMITTER:                                                                   |                |

| 6.3 JITTER ATTENUATOR:                                                                                        |                |

| TABLE 11: JITTER AMPLITUDE VERSUS MODULATION FREQUENCY (JITTER TOLERANCE)                                     |                |

| TABLE 12: JITTER TRANSFER SPECIFICATION/REFERENCES                                                            |                |

| 6.3.1 Jitter Generation:                                                                                      |                |

| 7.0 Serial Host interface:                                                                                    |                |

| TABLE 13: JITTER TRANSFER PASS MASKS                                                                          |                |

| Figure 24. Jitter Transfer Requirements and Jitter Attenuator Performance                                     |                |

| TABLE 14: FUNCTIONS OF SHARED PINS                                                                            |                |

| TABLE 15: XRT75L03 REGISTER MAP - QUICK LOOK                                                                  | 54             |

|                                                                                                               |                |

| THE REGISTER MAP AND DESCRIPTION FOR THE XRT75L03 3-CHANNEL DS3/E3/STS-1 LIU I<br>Legend:                     | 56             |

| TABLE 16: COMMAND REGISTER ADDRESS MAP, WITHIN THE XRT75L03 3-CHANNEL DS3/E3/STS-1 LIU w/ JI<br>ATTENUATOR IC |                |

| THE GLOBAL/CHIP-LEVEL REGISTERS                                                                               |                |

|                                                                                                               |                |

| REGISTER DESCRIPTION - GLOBAL REGISTERS                                                                       |                |

| TABLE 17: LIST AND ADDRESS LOCATIONS OF GLOBAL REGISTERS                                                      |                |

| TABLE 18: APS/REDUNDANCY CONTROL REGISTER - CR0 (ADDRESS LOCATION = 0x00)                                     |                |

| TABLE 19: BLOCK LEVEL INTERRUPT ENABLE REGISTER - CR32 (Address Location = 0x20)                              |                |

| TABLE 10: BLOCK LEVEL INTERRUPT STATUS REGISTER - CR33 (Address Location = 0x21)                              |                |

| TABLE 21: DEVICE/PART NUMBER REGISTER - CR62 (ADDRESS LOCATION = $0x3E$ )                                     |                |

| TABLE 21. DEVICE/TART NOWBER REGISTER - CROZ (ADDRESS ECCATION - 0.05L)                                       |                |

| THE PER-CHANNEL REGISTERS                                                                                     |                |

| TABLE 22: CHIP REVISION NUMBER REGISTER - CR63 (Address Location = 0x3F)                                      |                |

|                                                                                                               |                |

| TABLE 23: COMMAND REGISTER ADDRESS MAP, WITHIN THE XRT75L03 3-CHANNEL DS3/E3/STS-1 LIU W/ JI                  |                |

|                                                                                                               |                |

| REGISTER DESCRIPTION - PER CHANNEL REGISTERS                                                                  | 66             |

|                                                                                                               |                |

**X** EXAR

## XRT75L03 **XRT75L03 THREE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER ATTENUATOR**

| TABLE 24: SOURCE LEVEL INTERRUPT ENABLE REGISTER - CHANNEL 0 ADDRESS LOCATION = 0x01 | 66 |

|--------------------------------------------------------------------------------------|----|

| TABLE 25: SOURCE LEVEL INTERRUPT STATUS REGISTER - CHANNEL 0 ADDRESS LOCATION = 0x02 | 68 |

| TABLE 26: ALARM STATUS REGISTER - CHANNEL 0 ADDRESS LOCATION = 0x03                  | 70 |

| TABLE 27: TRANSMIT CONTROL REGISTER - CHANNEL 0 ADDRESS LOCATION = 0x04              | 75 |

| TABLE 28: RECEIVE CONTROL REGISTER - CHANNEL 0 ADDRESS LOCATION = 0x05               | 78 |

| TABLE 29: CHANNEL CONTROL REGISTER - CHANNEL 0 ADDRESS LOCATION = 0x06               | 80 |

| TABLE 30: JITTER ATTENUATOR CONTROL REGISTER - CHANNEL 0 ADDRESS LOCATION = 0x07     | 83 |

| 8.0 Diagnostic Features:                                                             | 84 |

| 8.1 PRBS GENERATOR AND DETECTOR:                                                     | 84 |

| 8.2 LOOPBACKS:                                                                       |    |

| Figure 25. PRBS MODE                                                                 | 84 |

| 8.2.1 ANALOG LOOPBACK:                                                               |    |

| Figure 26. Analog Loopback                                                           |    |

| 8.2.2 DIGITAL LOOPBACK:                                                              |    |

| 8.2.3 REMOTE LOOPBACK:                                                               |    |

| Figure 27. Digital Loopback                                                          |    |

| Figure 28. Remote Loopback                                                           |    |

| 8.3 TRANSMIT ALL ONES (TAOS):                                                        |    |

| Figure 29. Transmit All Ones (TAOS)                                                  |    |

| ORDERING INFORMATION                                                                 |    |

| PACKAGE DIMENSIONS - 14x20 MM, 128 PIN PACKAGE                                       | 88 |

| Revisions                                                                            | 89 |

## PIN DESCRIPTIONS (BY FUNCTION)

| Pin # | SIGNAL NAME | Түре | DESCRIPTION                                                                                                                                                                                                                                    |

|-------|-------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 38    | TxON_0      | I    | Transmitter ON Input - Channel 0:                                                                                                                                                                                                              |

| 1     | TxON_1      |      | Transmitter ON Input - Channel 1:                                                                                                                                                                                                              |

| 125   | TxON_2      |      | Transmitter ON Input - Channel 2:                                                                                                                                                                                                              |

|       |             |      | These input pins are used to either enable or disable the Transmit Output Driver corresponding to Channel_n.                                                                                                                                   |

|       |             |      | "Low" - Disables the Transmit Output Driver of the corresponding Channel.<br>In this setting, the corresponding TTIP_n and TRING_n output pins will be<br>tri-stated.                                                                          |

|       |             |      | "High" - Enables the Transmit Output Driver of the corresponding Channel.<br>In this setting, the corresponding TTIP_n and TRING_n output pins will be<br>enabled.                                                                             |

|       |             |      | Notes:                                                                                                                                                                                                                                         |

|       |             |      | <ol> <li>Even when the XRT75L03 is configured in HOST mode, these<br/>pins will be active. To enable software control of the Transmit<br/>Output Driver outputs, pull these pins "High".</li> </ol>                                            |

|       |             |      | <ol><li>When Transmitters are turned off either in Host or Hardware<br/>mode, the TTIP and TRing outputs are Tri-stated.</li></ol>                                                                                                             |

|       |             |      | 3. These pins are internally pulled "High"                                                                                                                                                                                                     |

| 35    | TxClk_0     | I    | Transmit Clock Input - Channel 0:                                                                                                                                                                                                              |

| 4     | TxClk_1     |      | Transmit Clock Input f - Channel 1:                                                                                                                                                                                                            |

| 26    | TxClk_2     |      | Transmit Clock Input - Channel 2:                                                                                                                                                                                                              |

|       |             |      | These input pins have two functions:                                                                                                                                                                                                           |

|       |             |      | • They function as the timing source for the Transmit Section of the corresponding channel within the XRT75L03.                                                                                                                                |

|       |             |      | • They also are used by the Transmit Section of the LIU IC to sample the corresponding TPDATA_n and TNDATA_n input pin.                                                                                                                        |

|       |             |      | <b>Note:</b> The user is expected to supply a 44.736MHz ± 20ppm clock signal (for DS3 applications), 34.368MHz ± 20 ppm clock signal (for E3 applications) or a 51.84MHz ± 4.6ppm clock signal (for STS-1, Stratum 3E or better applications). |

| Pin # | SIGNAL NAME       | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------|-------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 34    | TPDATA_0/TxDATA_0 | I    | Transmit Positive Data Input - Channel 0:                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3     | TPDATA_1/TxDATA_1 |      | Transmit Positive Data Input - Channel 1:                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 25    | TPDATA_2/TxDATA_2 |      | Transmit Positive Data Input - Channel 2:                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       |                   |      | Transmit Positive Data/Data Input - Channel n:                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|       |                   |      | The function of these input pins depends upon whether the corresponding channel has been configured to operate in the Single-Rail or Dual-Rail Mode.                                                                                                                                                                                                                                                                                                                                      |

|       |                   |      | Single Rail Mode - Transmit Data Input - Channel n:                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|       |                   |      | If the Channel has been configured to operate in the Single-Rail Mode, then<br>all transmit output data will be serially applied to this input pin. This signal<br>will latched into the Transmit Section circuitry upon either the rising or fall-<br>ing edge of the TxCLK_n signal, depending upon user configuration.<br>In the Single-Rail Mode, the Transmit Section of the LIU IC will then encode<br>this data into either the B3ZS line code (for DS3 and STS-1 applications) or |

|       |                   |      | the HDB3 line code (for E3 applications).                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       |                   |      | Dual Rail Mode - Transmit Positive Data Input - Channel n:                                                                                                                                                                                                                                                                                                                                                                                                                                |

|       |                   |      | If the Channel has been configured to operate in the Dual-Rail Mode, then<br>the user should apply a pulse to this input pin, anytime the Transmit Section<br>of the LIU IC is suppose to generate and transmit a positive-polarity pulse<br>onto the line. This signal will be latched into the Transmit Section circuitry<br>upon either the rising or falling edge of the TxCLK_n signal, depending<br>upon user configuration.                                                        |

|       |                   |      | In the Dual-Rail Mode, the Transmit Section of the LIU IC will NOT encode<br>this data into either the B3ZS or HDB3 line codes. If the user configures<br>the LIU IC to operate in the Dual-Rail Mode, then B3ZS/HDB3 encoding<br>must have already been done prior to providing the transmit output data to<br>this input pin.                                                                                                                                                           |

| 33    | TNData_0          | I    | Transmit Negative Data Input - Channel 0:                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2     | TNData_1          |      | Transmit Negative Data Input - Channel 1:                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 24    | TNData_2          |      | Transmit Negative Data Input - Channel 2:                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       |                   |      | If a Channel has been configured to operate in the Dual-Rail Mode, then<br>the user should apply a pulse to this input pin anytime the Transmit Section<br>of the LIU IC is suppose to generate and transmit a negative-polarity pulse<br>onto the line. This signal will be latched into the Transmit Section circuitry<br>upon either the rising or falling edge of the TxCLK_n signal, depending<br>upon user configuration.                                                           |

|       |                   |      | <b>Note:</b> If the Channel has been configured operate in the Single-Rail Mode, then this input pin has no function, and should be tied to GND.                                                                                                                                                                                                                                                                                                                                          |

#### XRT75L03 *REV. 1.0.4*

## THREE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER ATTENUATOR

| PIN # | SIGNAL NAME | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                           |

|-------|-------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 37    | TAOS_0      | I    | Transmit "All Ones" Input - Channel 0:                                                                                                                                                                                                                                                                                |

| 7     | TAOS_1      |      | Transmit "All Ones" Input - Channel 1:                                                                                                                                                                                                                                                                                |

| 8     | TAOS_2      |      | Transmit "All Ones" Input - Channel 2:                                                                                                                                                                                                                                                                                |

|       |             |      | These input pin are used to configure the Transmit Section of the corre-<br>sponding channel to generate and transmit an unframed "All Ones" pattern<br>via the DS3, E3 or STS-1 line signal to the remote terminal equipment.                                                                                        |

|       |             |      | When this configuration is implemented the Transmit Section will ignore the data that it is accepting from the System-side equipment and will overwrite this data will the "All Ones" Pattern.                                                                                                                        |

|       |             |      | "Low" - Does not configure the channel to transmit an unframed "All Ones"<br>Pattern to the remote terminal equipment. In this mode, the Transmit Sec-<br>tion of the Channel will output data based upon the signals that are applied<br>to the TxPOS_n and TxNEG_n input pins.                                      |

|       |             |      | "High" - Configures the Channel to transmit an unframed "All Ones" Pattern to the remote terminal equipment. In this mode, the Transmit Section will override the data that is applied to the TxPOS_n and TxNEG_n input pins, and will proceed to generate and transmit an unframed "All Ones" pattern.               |

|       |             |      | 4. This input pin is ignored if the XRT75L03 is operating in the HOST Mode and should be tied to GND.                                                                                                                                                                                                                 |

|       |             |      | 5. These input pins are internally pulled down.                                                                                                                                                                                                                                                                       |

| 36    | TxLEV_0     |      | Transmit Line Build-Out Enable/Disable Select - Channel 0:                                                                                                                                                                                                                                                            |

| 9     | TxLEV_1     |      | Transmit Line Build-Out Enable/Disable Select - Channel 1:                                                                                                                                                                                                                                                            |

| 10    | TxLEV_2     |      | Transmit Line Build-Out Enable/Disable Select - Channel 2:                                                                                                                                                                                                                                                            |

|       |             |      | These input pins are used to enable or disable the Transmit Line Build-Out (e.g., pulse-shaping) circuit within the corresponding channel. The user should set these input pins either "High" or "Low" based upon the following guidelines.                                                                           |

|       |             |      | "Low" - If the cable length between the Transmit Output of the correspond-<br>ing Channel and the DSX-3/STSX-1 location is 225 feet or less.                                                                                                                                                                          |

|       |             |      | "High" - If the cable length between the Transmit Output of the correspond-<br>ing Channel and the DSX-3/STSX-1 location is 225 feet or more.                                                                                                                                                                         |

|       |             |      | Notes:                                                                                                                                                                                                                                                                                                                |

|       |             |      | 1. These guidelines must be followed in order to insure that the Transmit Section of Channel_n will always generate a DS3 pulse that complies with the Isolated Pulse Template requirements per Bellcore GR-499-CORE, or an STS-1 pulse that complies with the Pulse Template requirements per Telcordia GR-253-CORE. |

|       |             |      | <ol> <li>This input pin is inactive if the XRT75L03 has been configured to<br/>operate in the Host Mode, or if the corresponding channel has<br/>been configured to operate in the E3 Mode. If either of these<br/>cases are true, then tie this input pin to GND.</li> </ol>                                         |

|       |             |      | 3. These input pins are internally pulled "Low".                                                                                                                                                                                                                                                                      |

| PIN # | SIGNAL NAME | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                           |

|-------|-------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 40    | DMO_0       | 0    | Drive Monitor Output - Channel 0:                                                                                                                                                                                                                                                                     |

| 127   | DMO_1       |      | Drive Monitor Output - Channel 1:                                                                                                                                                                                                                                                                     |

| 22    | DMO_2       |      | Drive Monitor Output - Channel 2:                                                                                                                                                                                                                                                                     |

|       |             |      | These output signals are used to indicate some sort of fault condition within the Transmit Output signal path.                                                                                                                                                                                        |

|       |             |      | This output pin will toggle "High" anytime the Transmit Drive Monitor cir-<br>cuitry either, via the corresponding MTIP and MRING input pins or inter-<br>nally, detects no bipolar pulses via the Transmit Output line signal (e.g., via<br>the TTIP_n and TRING_n output pins) for 128 bit-periods. |

|       |             |      | This output pin will be driven "Low" anytime the Transmit Drive Monitor cir-<br>cuitry has detected at least one bipolar pulse via the Transmit Output line<br>signal within the last 128 bit periods.                                                                                                |

| 67    | TxClkINV/   | I    | Hardware Mode: Transmit Clock Invert                                                                                                                                                                                                                                                                  |

|       | SClk        |      | Host Mode: Serial Clock Input:                                                                                                                                                                                                                                                                        |

|       |             |      | Hardware mode                                                                                                                                                                                                                                                                                         |

|       |             |      | This input pin is used to select the edge of the TxCLK_n input that the Transmit Section of all channels will use to sample the TPDATA_n and TNDATA_n input pins.                                                                                                                                     |

|       |             |      | Setting this input pin "High" configures all three Transmitters to sample the TPData_n and TNData_n data on the rising edge of the $TxClk_n$ .                                                                                                                                                        |

|       |             |      | Setting this input pin "Low" configures all three Transmitters to sample the TPData_n and TNData_n data on the falling edge of the TxClk_n .                                                                                                                                                          |

|       |             |      | Host Mode                                                                                                                                                                                                                                                                                             |

|       |             |      | In the Host Mode this pin functions as SClk input pin please refer to the pin descriptions for the Microprocessor interface.                                                                                                                                                                          |

## TRANSMIT LINE SIDE PINS

| Pin # | SIGNAL NAME | Түре | DESCRIPTION                                                                                                                                                                                                                     |

|-------|-------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 30    | TTIP_0      | 0    | Transmit TTIP Output - Positive Polarity Signal - Channel 0:                                                                                                                                                                    |

| 11    | TTIP_1      |      | Transmit TTIP Output - Positive Polarity Signal - Channel 1:                                                                                                                                                                    |

| 21    | TTIP_2      |      | Transmit TTIP Output - Positive Polarity Signal - Channel 2:                                                                                                                                                                    |

|       |             |      | These output pins along with the corresponding TRING_n output pins, function as the Transmit DS3/E3/STS-1 Line output signal drivers for a given channel, of the XRT75L03.                                                      |

|       |             |      | Connect this signal and the corresponding TRING_n output signal to a 1:1 transformer.                                                                                                                                           |

|       |             |      | Whenever the Transmit Section of the Channel generates and transmits a posi-<br>tive-polarity pulse onto the line, this output pin will be pulsed to a "higher-volt-<br>age" than its corresponding TRING_n output pins.        |

|       |             |      | Conversely, whenever the Transmit Section of the Channel generates and trans-<br>mit a negative-polarity pulse onto the line, this output pin will be pulsed to a<br>"lower-voltage" than its corresponding TRING_n output pin. |

|       |             |      | <b>Note:</b> This output pin will be tri-stated whenever the corresponding TxON_n input pin or bit-field is set to "0".                                                                                                         |

| 28    | TRing_0     | 0    | Transmit Ring Output - Negative Polarity Signal - Channel 0:                                                                                                                                                                    |

| 13    | TRing_1     |      | Transmit Ring Output - Negative Polarity Signal - Channel 1:                                                                                                                                                                    |

| 19    | TRing_2     |      | Transmit Ring Output - Negative Polarity Signal - Channel 2:                                                                                                                                                                    |

|       |             |      | These output pins along with the corresponding TTIP_n output pins, function as the Transmit DS3/E3/STS-1 Line output signal drivers for a given channel, within the XRT75L03.                                                   |

|       |             |      | Connect this signal and the corresponding TTIP_n output signal to a 1:1 transformer.                                                                                                                                            |

|       |             |      | Whenever the Transmit Section of the Channel generates and transmits a posi-<br>tive-polarity pulse onto the line. This output pin will be pulsed to a "lower-volt-<br>age" than its corresponding TTIP_n output pins.          |

|       |             |      | Conversely, whenever the Transmit Section of the Channel generates and trans-<br>mit a negative-polarity pulse onto the line. This output pin will be pulsed to a<br>"higher-voltage" than its corresponding TTIP_n output pin. |

|       |             |      | <b>Note:</b> This output pin will be tri-stated whenever the corresponding TxON_n input pin or bit-field is set to "0".                                                                                                         |

XRT75L03

## REV. 1.0.4

THREE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER ATTENUATOR

## TRANSMIT LINE SIDE PINS

| Pin # | SIGNAL NAME | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------|-------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31    | MTIP_0      | I    | Monitor Tip Input - Positive Polarity Signal - Channel 0:                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6     | MTIP_1      |      | Monitor Tip Input - Positive Polarity Signal - Channel 1:                                                                                                                                                                                                                                                                                                                                                                                                           |

| 17    | MTIP_2      |      | Monitor Tip Input - Positive Polarity Signal - Channel 2:                                                                                                                                                                                                                                                                                                                                                                                                           |

|       |             |      | These input pins along with MRING_n function as the Transmit Drive Monitor<br>Output (DMO) input monitoring pins. To (1) monitor the Transmit Output line<br>signal and (2) to perform this monitoring externally, then this pin MUST be con-<br>nected to the corresponding TTIP_n output pin via a 274 ohm series resistor.<br>Similarly, the MRING_n input pin MUST also be connected to its corresponding<br>TRING_n output pin via a 274 ohm series resistor.  |

|       |             |      | The MTIP_n and MRING_n input pins will continuously monitor the Transmit<br>Output line signal via the TTIP_n and TRING_n output pins for bipolar activity. If<br>these pins do not detect any bipolar activity for 128 bit periods, then the Trans-<br>mit Drive Monitor circuit will drive the corresponding DMO_n output pin "High" in<br>order to denote a possible fault condition in the Transmit Output Line signal<br>path.                                 |

|       |             |      | <ol> <li>These input pins are inactive if the user choose to internally monitor<br/>the Transmit Output line signal.</li> </ol>                                                                                                                                                                                                                                                                                                                                     |

|       |             |      | 2. Internal Monitoring is only available as an option if the XRT75L03 in is being operated in the Host Mode.                                                                                                                                                                                                                                                                                                                                                        |

| 32    | MRing_0     | I    | Monitor Ring Input - Channel 0:                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5     | MRing_1     |      | Monitor Ring Input - Channel 1:                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 16    | MRing_2     |      | Monitor Ring Input - Channel 2:                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|       |             |      | These input pins along with MTIP_n function as the Transmit Drive Monitor Out-<br>put (DMO) input monitoring pins. To (1) monitor the Transmit Output line signal<br>and (2) to perform this monitoring externally, then this input pin MUST be con-<br>nected to the corresponding TRING_n output pin via a 274 ohm series resistor.<br>Similarly, the MTIP_n input pin MUST be connected to its corresponding<br>TTIP_n output pin via a 274 ohm series resistor. |

|       |             |      | The MTIP_n and MRING_n input pins will continuously monitor the Transmit<br>Output line signal via the TTIP_n and TRING_n output pins for bipolar activity. If<br>these pins do not detect any bipolar activity for 128 bit periods, then the Trans-<br>mit Drive Monitor circuit will drive the corresponding DMO_n output pin "High" to<br>indicate a possible fault condition in the Transmit Output Line signal path.                                           |

|       |             |      | <b>Notes:</b><br>1. These input pins are inactive if the user chooses to internally monitor                                                                                                                                                                                                                                                                                                                                                                         |

|       |             |      | the Transmit Output line signal.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       |             |      | 2. Internal Monitoring is only available as an option if the XRT75L03 is being operated in the Host Mode.                                                                                                                                                                                                                                                                                                                                                           |

| Pin # | SIGNAL NAME    | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------|----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 60    | RLOS_0         | 0    | Receive Loss of Signal Output Indicator - Channel 0:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 104   | RLOS_1         |      | Receive Loss of Signal Output Indicator - Channel 1:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 63    | RLOS_2         |      | Receive Loss of Signal Output Indicator - Channel 2:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|       |                |      | This output pin indicates whether or not the corresponding channel is declaring the Loss of Signal (LOS) Defect condition.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|       |                |      | "Low" - Indicates that the corresponding Channel is NOT currently declaring the LOS defect condition.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|       |                |      | "High" - Indicates that the corresponding Channel is currently declaring the LOS defect condition.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 61    | RLOL_0         | 0    | Receive Loss of Lock Output Indicator - Channel 0:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 103   | RLOL_1         |      | Receive Loss of Lock Output Indicator - Channel 1:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 64    | RLOL_2         |      | Receive Loss of Lock Output Indicator - Channel 2:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       |                |      | This output pin indicates whether or not the corresponding channel is declaring the Loss of Lock (LOL) Condition.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|       |                |      | "Low" - Indicates that the corresponding Channel is NOT declaring the LOL con-<br>dition.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|       |                |      | "High" - Indicates that the corresponding Channel is currently declaring the LOL condition.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|       |                |      | <b>Note:</b> The Receive Section of a given channel will declare the LOL condition<br>anytime the frequency of the Recovered Clock (RCLK) signal differs<br>from that of the E3CLK input clock signal (if the channel is operating in<br>the E3 Mode), the DS3CLK input clock signal (if the channel is<br>operating in the DS3 Mode) the STS-1CLK input clock signal (if the<br>channel is operating in the STS-1 Mode), or that clock signal which is<br>derived from the SFM Clock Synthesizer block (if the chip is operating in<br>the Single-Frequency Mode) by 0.5% (or 5000ppm) or more. |

| 58    | RPOS_0/RDATA_0 | 0    | Receive Positive Data Output - Receive Data Output - Channel 0:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 112   | RPOS_1/RDATA_1 |      | Receive Positive Data Output - Receive Data Output - Channel 1:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 53    | RPOS_2/RDATA_2 |      | Receive Positive Data Output - Receive Data Output - Channel 2:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|       |                |      | The function of these output pins depends upon whether the channel/device has been configured to operate in the Single-Rail or Dual-Rail Mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|       |                |      | Dual-Rail Mode - Receive Positive Polarity Data Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       |                |      | If the channel/device has been configured to operate in the Dual-Rail Mode,<br>then all positive-polarity data will be output via this output pin. The negative-<br>polarity data will be output via the corresponding RNEG_n output pin. In other<br>words, the Receive Section of the corresponding Channel will pulse this output<br>pin "High" for one period of RCLK_n anytime it receives a positive-polarity pulse<br>via the RTIP/RRING input pins.                                                                                                                                      |

|       |                |      | The data that is output via this pin is updated upon a user-selectable edge of the RCLK_n output clock signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|       |                |      | Single-Rail Mode - Receive Data Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       |                |      | If the channel/device has been configured to operate in the Single-Rail Mode, then all Receive (or Recovered) data will be output via this output pin.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       |                |      | The data that is output via this pin is updated upon a user-selectable edge of the RCLK_n output clock signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Pin # | SIGNAL NAME  | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                 |