Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

AUGUST 2010 REV. 1.0.1

### GENERAL DESCRIPTION

The XRT83VL38 is a fully integrated Octal (eight channel) long-haul and short-haul line interface unit for T1 (1.544Mbps)  $100\Omega$ , E1 (2.048Mbps)  $75\Omega$  or  $120\Omega$ , J1  $110\Omega$  or BITS Timing applications.

In long-haul applications the XRT83VL38 accepts signals that have been attenuated from 0 to 36dB at 772kHz in T1 mode (equivalent of 0 to 6000 feet of cable loss) or 0 to 43dB at 1024kHz in E1 mode.

In T1 applications, the XRT83VL38 can generate five transmit pulse shapes to meet the short-haul Digital Cross-Connect (DSX-1) template requirements as well as for Channel Service Units (CSU) Line Build Out (LBO) filters of 0dB, -7.5dB -15dB and -22.5dB as required by FCC rules. It also provides programmable transmit pulse generators for each channel that can be used for output pulse shaping allowing performance improvement over a wide variety of conditions (The arbitrary pulse generators are available in both T1 and E1 modes).

The XRT83VL38 provides both a parallel/serial **Host** microprocessor interface as well as a **Hardware** mode for programming and control.

Both the B8ZS and HDB3 encoding and decoding functions are selectable as well as AMI. Two on-chip

crystal-less jitter attenuators with a 32 or 64 bit FIFO can be placed in the receive and the transmit paths with loop bandwidths of less than 3Hz. The XRT83VL38 provides a variety of loop-back and diagnostic features as well as transmit driver short circuit detection and receive loss of signal monitoring. It supports internal impedance matching for  $75\Omega,100\Omega,110\Omega$  and  $120\Omega$  for both transmitter and receiver. In the absence of the power supply, the transmit outputs and receive inputs are tri-stated allowing for redundancy applications. The chip includes an integrated programmable clock multiplier that can synthesize T1 or E1 master.

### **APPLICATIONS**

- BITS Timing

- T1 Digital Cross-Connects (DSX-1)

- ISDN Primary Rate Interface

- CSU/DSU E1/T1/J1 Interface

- T1/E1/J1 LAN/WAN Routers

- Public switching Systems and PBX Interfaces

- T1/E1/J1 Multiplexer and Channel Banks

### Features (See Page 2)

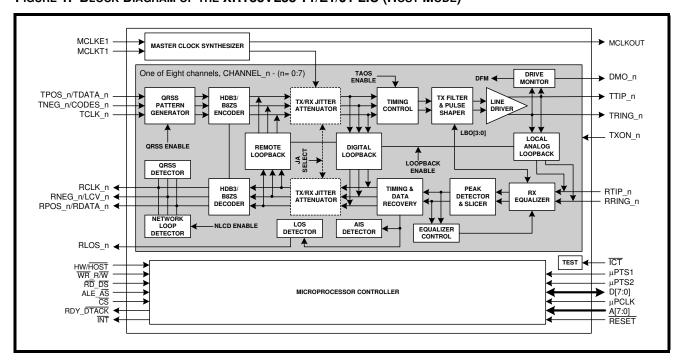

FIGURE 1. BLOCK DIAGRAM OF THE XRT83VL38 T1/E1/J1 LIU (HOST MODE)

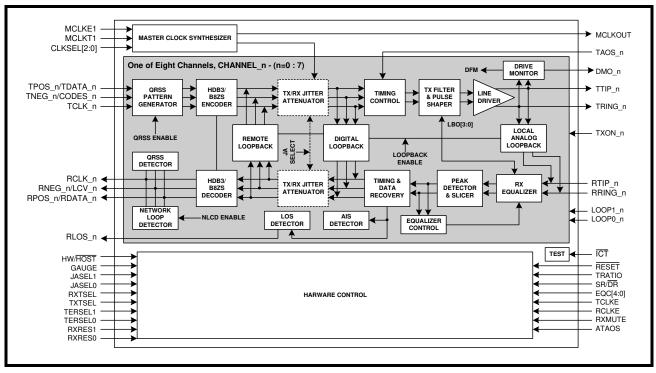

FIGURE 2. BLOCK DIAGRAM OF THE XRT83VL38 T1/E1/J1 LIU (HARDWARE MODE)

### **FEATURES**

- Supports Section 13 Synchronization Interface in ITU G.703 for both Transmit and Receive Paths

- Fully integrated eight channel long-haul or short-haul transceivers for E1,T1 or J1 applications

- Adaptive Receive Equalizer for up to 36dB cable attenuation

- Programable Transmit Pulse Shaper for E1,T1 or J1 short-haul interfaces

- Five fixed transmit pulse settings for T1 short-haul applications plus a fully programmable waveform generator for transmit output pulse shaping available for both T1 and E1 modes

- Transmit Line Build-Outs (LBO) for T1 long-haul application from 0dB to -22.5dB in three 7.5dB steps

- Selectable receiver sensitivity from 0 to 36dB cable loss for T1 @772kHz and 0 to 43dB for E1 @1024kHz

- Receive monitor mode handles 0 to 29dB resistive attenuation along with 0 to 6dB of cable attenuation for E1 and 0 to 3dB of cable attenuation for T1 modes

- Supports  $75\Omega$  and  $120\Omega$  (E1),  $100\Omega$  (T1) and  $110\Omega$  (J1) applications

- Internal and/or external impedance matching for  $75\Omega$ ,  $100\Omega$ ,  $110\Omega$  and  $120\Omega$

- Tri-State transmit output and receive input capability for redundancy applications

- Provides High Impedance for Tx and Rx during power off

- Transmit return loss meets or exceeds ETSI 300-166 standard

- On-chip digital clock recovery circuit for high input jitter tolerance

- Crystal-less digital jitter attenuator with 32-bit or 64-bit FIFO selectable in transmit or receive paths

- On-chip frequency multiplier generates T1 or E1 Master clocks

- High receiver interference immunity

- On-chip transmit short-circuit protection and limiting, and driver fail monitor output (DMO)

- Receive loss of signal (RLOS) output

- On-chip HDB3/B8ZS/AMI encoder/decoder functions

- QRSS pattern generator and detection for testing and monitoring

- Error and Bipolar Violation Insertion and Detection

- Receiver Line Attenuation Indication Output in 1dB steps

- Network Loop-Code Detection for automatic Loop-Back Activation/Deactivation

- Transmit All Ones (TAOS) and In-Band Network Loop Up and Down code generators

- Supports Local Analog, Remote, Digital and Dual Loop-Back Modes

- Meets or exceeds T1 and E1 short-haul and long-haul network access specifications in ITU G.703, G.775, G.736 and G.823; TR-TSY-000499; ANSI T1.403 and T1.408; ETSI 300-166 and AT&T Pub 62411

- Supports both Hardware and Host (parallel or serial) Microprocessor interface for programming

- Programmable Interrupt

- Low power dissipation

- Logic inputs accept either 3.3V or 5V levels

- Dual 3.3V and 1.8V Supply Operation

- 225 ball BGA package

- -40°C to +85°C Temperature Range

### ORDERING INFORMATION

| PART NUMBER | PACKAGE      | OPERATING TEMPERATURE RANGE |  |  |

|-------------|--------------|-----------------------------|--|--|

| XRT83VL38IB | 225 Ball BGA | -40°C to +85°C              |  |  |

FIGURE 3. PACKAGE PIN OUT

| Α | DGND     | RNEG_0   | TCLK_1   | TPOS_1   | TAOS_2 | RDY_DTACK  | ALE_AS | CLKSEL0  | DVDD    | A[1]     | A[3]    | A[7]   | TXON_0 | JASEL0  | TCLK_2  | RLOS_3    | RCLK_3    | DVDD_DR |

|---|----------|----------|----------|----------|--------|------------|--------|----------|---------|----------|---------|--------|--------|---------|---------|-----------|-----------|---------|

| В | TDO      | RPOS_0   | RCLK_0   | TCLK_0   | TNEG_1 | TAOS_1     | CS     | CLKSEL1  | DGND    | A[2]     | A[6]    | TX0N_3 | JASEL1 | TPOS_2  | TNEG_3  | RNEG_3    | RPOS_3    | NC12    |

| С | RTIP_0   | RVDD_0   | RLOS_0   | TNEG_0   | TPOS_0 | TAOS_3     | RD_DS  | CLKSEL2  | DGND    | A[0]     | A[5]    | TXON_2 | DMO_3  | TCLK_3  | DMO_2   | TTIP_3    | TGND_3    | RTIP_3  |

| D | RRING_0  | RGND_0   | TGND_0   | DMO_1    | DMO_0  | TAOS_0     | WR_R/W | DGND     | DVDD_DR | DVDD_PDR | A[4]    | TXON_1 | TNEG_2 | TPOS_3  | RPOS_2  | RVDDD_3   | RGND_3    | RRING_3 |

| Ε | TMS      | TRING_O  | TTIP_0   | TVDD_0   | RVDD_1 |            |        |          |         |          |         |        |        |         | TGND_2  | TRING_3   | TVDD_3    | NC11    |

| F | RRING_1  | TGND_1   | TRING_1  | TVDD_1   |        |            |        |          |         |          |         |        |        |         | TRING_2 | TVDD_2    | TTIP_2    | RRING_2 |

| G | RTIP_1   | RPOS_1   | RGND_1   | TTIP_1   |        |            |        |          |         |          |         |        |        |         | DGND    | RVDD_2    | RGND_2    | RTIP_2  |

| Н | MCLKOUT  | RNEG_1   | RCLK_1   | RLOS_1   |        |            |        |          |         |          |         |        |        |         | RLOS_2  | RCLK_2    | DGND      | RNEG_2  |

| J | MCLKE1   | VDDPLL_2 | VDDPLL_1 | DVDD_DR  |        |            |        | <b>)</b> | KRT83   | VL38     |         |        |        |         | RLOS_6  | PTS1      | AGND_BIAS | GAUGE   |

| K | MCLKT1   | DGND     | GNDPLL_1 | SR_DR    |        | (Top View) |        |          |         |          |         |        |        | DVDD_DR | RXON    | AVDD_BIAS | DVDDD_μP  |         |

| L | RTIP_5   | RLOS_5   | RCLK_5   | GNDPLL_2 |        |            |        | 2        | 225 Bal | I BGA    |         |        |        |         | PTS2    | ĪNT       | RPOS_6    | RTIP_6  |

| М | RRING_5  | RGND_5   | RPOS_5   | RNEG_5   |        |            |        |          |         |          |         |        |        |         | RCLK_6  | RNEG_6    | RGND_6    | RRING_6 |

| N | TCK      | TTIP_5   | RVDD_5   | TRING_5  |        |            |        |          |         |          |         |        |        |         | TVDD_6  | TTIP_6    | RVDD_6    | SENSE   |

| Р | TVDD_5   | TRING_4  | TGND_5   | DMO_5    |        |            |        |          |         |          |         |        |        |         | TVDD_7  | TTIP_7    | TRING_7   | SER_PAR |

| R | TDI      | TTIP_4   | TGND_4   | TVDD_4   | DMO_4  | TAOS_7     | D[0]   | DGND     | DVDD_DR | RXRES1   | TERSEL0 | TXON_6 | TXON_7 | TNEG_7  | TRING_6 | TGND_7    | RGND_7    | RRING_7 |

| Т | RRING_4  | RGND_4   | TCLK_4   | RNEG_4   | TCLK_5 | TAOS_4     | D[7]   | RESET    | DGND    | HW_HOST  | TERSEL1 | RXMUTE | μPCLK  | TPOS_7  | RLOS_7  | TGND_6    | RPOS_7    | RTIP_7  |

| U | RTIP_4   | RPOS_4   | RCLK_4   | TNEG_4   | TPOS_5 | TAOS_5     | D[6]   | D[2]     | D[1]    | DVDD_PDR | RXTSEL  | TEST   | TXON_5 | TNEG_6  | TCLK_7  | RCLK_7    | DMO_6     | RVDD_7  |

| ٧ | DVDD_PDR | RVDD_4   | RLOS_4   | TPOS_4   | TNEG_5 | TAOS_6     | D[5]   | D[4]     | D[3]    | RXRES0   | TXTSEL  | ĪCT    | TXON_4 | DMO_7   | TPOS_6  | TCLK_6    | RNEG_7    | DGND    |

|   | 1        | 2        | 3        | 4        | 5      | 6          | 7      | 8        | 9       | 10       | 11      | 12     | 13     | 14      | 15      | 16        | 17        | 18      |

# REV. 1.0.1

# **GENERAL DESCRIPTION 1**

Applications 1

Block Diagram of the XRT83VL38 T1/E1/J1 LIU (Host Mode) 1

Block Diagram of the XRT83VL38 T1/E1/J1 LIU (Hardware Mode) 2

Features 2

Ordering Information 3

Package Pin Out 4

PIN DESCRIPTION BY FUNCTION 5

Receive Sections 5

**Transmitter Sections 7**

Microprocessor Interface 11

jitter Attenuator 14

Clock Synthesizer 14

Alarm Functions/Redundancy Support 16

Serial Microprocessor Interface 20

Power and Ground 21

**FUNCTIONAL DESCRIPTION 23**

Master Clock Generator 23

Two Input Clock Source 23

One Input Clock Source 23

Master Clock Generator 24

24

**RECEIVER 24**

Receiver Input 24

Receive Monitor Mode 25

Receiver Loss of Signal (RLOS) 25

Simplified Diagram of -15dB T1/E1 Short Haul Mode and RLOS Condition 25

Simplified Diagram of -29dB T1/E1 Gain Mode and RLOS Condition 26

Simplified Diagram of -36dB T1/E1 Long Haul Mode and RLOS Condition 26

Simplified Diagram of Extended RLOS mode (E1 Only) 27

Receive HDB3/B8ZS Decoder 27

Recovered Clock (RCLK) Sampling Edge 27

Receive Clock and Output Data Timing 28

Jitter Attenuator 28

Gapped Clock (JA Must be Enabled in the Transmit Path) 28

Maximum Gap Width for Multiplexer/Mapper Applications 28

Arbitrary Pulse Generator for T1 and e1 29

Arbitrary Pulse Segment Assignment 29

**TRANSMITTER 29**

Digital Data Format 29

Transmit Clock (TCLK) Sampling Edge 29

Transmit Clock and Input Data Timing 30

Transmit HDB3/B8ZS Encoder 30

Examples of HDB3 Encoding 30

Examples of B8ZS Encoding 30

30

Driver Failure Monitor (DMO) 31

### XRT83VL38

# EXAR Powering Connectivity\*

### OCTAL T1/E1/J1 LH/SH TRANSCEIVER WITH CLOCK RECOVERY AND JITTER ATTENUATOR

REV. 1.0.1

Transmit Pulse Shaper & Line Build Out (LBO) circuit 31

Receive Equalizer Control and Transmit Line Build-Out Settings 31

Transmit and Receive Terminations 33

RECEIVER (Channels 0 - 7) 33

**Internal Receive Termination Mode 33**

Receive Termination Control 33

Simplified Diagram for the Internal Receive and Transmit Termination Mode 33

Receive Terminations 34

Simplified Diagram for T1 in the External Termination Mode (RXTSEL= 0 & TXTSEL= 0) 34

Simplified Diagram for E1 in External Receive Termination Mode (RXTSEL= 0) and Internal Trans-

mit Termination Mode (TXTEL= 1) 35

TRANSMITTER (Channels 0 - 7) 35

**Transmit Termination Mode 35**

**Termination Select Control 35**

**External Transmit Termination Mode 35**

**Transmit Terminations 36**

36

36

**REDUNDANCY APPLICATIONS 36**

TYPICAL REDUNDANCY SCHEMES 37

Simplified Block Diagram of the Transmit Section for 1:1 & 1+1 Redundancy 38

Simplified Block Diagram - Receive Section for 1:1 and 1+1 Redundancy 38

Simplified Block Diagram - Transmit Section for N+1 Redundancy 39

Simplified Block Diagram - Receive Section for N+1 Redundancy 40

Pattern Transmit and Detect Function 41

Pattern transmission control 41

Transmit All Ones (TAOS) 41

Network Loop Code Detection and Transmission 41

Loop-Code Detection Control 41

Transmit and Detect Quasi-Random Signal Source (TDQRSS) 42

Loop-Back Modes 43

Loop-back control in Hardware mode 43

Loop-back control in Host mode 43

Local Analog Loop-Back (ALOOP) 43

Local Analog Loop-back signal flow 43

Remote Loop-Back (RLOOP) 44

Remote Loop-back mode with jitter attenuator selected in receive path 44

Remote Loop-back mode with jitter attenuator selected in Transmit path 44

Digital Loop-Back (DLOOP) 45

Digital Loop-back mode with jitter attenuator selected in Transmit path 45

Dual Loop-Back 45

Signal flow in Dual loop-back mode 45

**MICROPROCESSOR INTERFACE 46**

Serial Microprocessor Interface Block 46

Simplified Block Diagram of the Serial Microprocessor Interface 46

Serial Timing Information 46

Timing Diagram for the Serial Microprocessor Interface 46

### OCTAL T1/E1/J1 LH/SH TRANSCEIVER WITH CLOCK RECOVERY AND JITTER ATTENUATOR

24-Bit Serial Data Input Descritption 46

ADDR[7:0] (SCLK1 - SCLK8) 47

R/W (SCLK9) 47

Dummy Bits (SCLK10 - SCLK16) 47

DATA[7:0] (SCLK17 - SCLK24) 47

8-Bit Serial Data Output Description 47

Timing Diagram for the Microprocessor Serial Interface 47

Microprocessor Serial Interface Timings ( TA = 250C,  $VDD=3.3V\pm5\%$  and load = 10pF) 48

Parallel Microprocessor Interface Block 48

Selecting the Microprocessor Interface Mode 48

Simplified Block Diagram of the Microprocessor Interface Block 49

The Microprocessor Interface Block Signals 49

XRT83VL38 Microprocessor Interface Signals that exhibit constant roles in both Intel and Motorola Modes 49

Intel mode: Microprocessor Interface Signals 50

Motorola Mode: Microprocessor Interface Signals 50

Intel Mode Programmed I/O Access (Asynchronous) 50

Intel µP Interface Signals During Programmed I/O Read and Write Operations 51

Motorola Mode Programmed I/O Access (Asynchronous) 52

Intel Microprocessor Interface Timing Specifications 52

Motorola 68K µP Interface Signals During Programmed I/O Read and Write Operations 53

Motorola 68K Microprocessor Interface Timing Specifications 53

Microprocessor Register Tables 53

Microprocessor Register Address 54

Microprocessor Register Bit Description 54

Microprocessor Register Descriptions 57

Microprocessor Register #0, Bit Description 57

Microprocessor Register #1, Bit Description 59

Microprocessor Register #2, Bit Description 61

Microprocessor Register #3, Bit Description 63

Microprocessor Register #4, Bit Description 64

Microprocessor Register #5, Bit Description 66

Microprocessor Register #6, Bit Description 68

Microprocessor Register #7, Bit Description 69

Microprocessor Register #8, Bit Description 70

Microprocessor Register #9, Bit Description 70

Microprocessor Register #10, Bit Description 71

Microprocessor Register #11, Bit Description 71

Microprocessor Register #12, Bit Description 72

Microprocessor Register #13, Bit Description 72

Microprocessor Register #14, Bit Description 73

Microprocessor Register #15, Bit Description 73

Microprocessor Register #128, Bit Description 74

clock select register 75

Register 0x81h Sub Registers 75

Microprocessor Register #129, Bit Description 75

### XRT83VL38

# EXAR Powering Connectivity

### OCTAL T1/E1/J1 LH/SH TRANSCEIVER WITH CLOCK RECOVERY AND JITTER ATTENUATOR

REV. 1.0.1

Microprocessor Register #130, Bit Description 76

Microprocessor Register #131, Bit Description 77

Microprocessor Register #192, Bit Description 78

**ELECTRICAL CHARACTERISTICS 79**

**Absolute Maximum Ratings 79**

DC Digital Input and Output Electrical Characteristics 79

XRT83VL38 Power Consumption 79

E1 Receiver Electrical Characteristics 80

T1 Receiver Electrical Characteristics 81

E1 Transmit Return Loss Requirement 81

E1 Transmitter Electrical Characteristics 82

T1 Transmitter Electrical Characteristics 82

ITU G.703 Pulse Template 83

Transmit Pulse Mask Specification 83

ITU G.703 Section 13 Synchronous Interface Pulse Template 84

E1 Synchronous Interface Transmit Pulse Mask Specification 84

DSX-1 Pulse Template (normalized amplitude) 85

DSX1 Interface Isolated pulse mask and corner points 85

AC Electrical Characteristics 86

Transmit Clock and Input Data Timing 86

Receive Clock and Output Data Timing 87

Microprocessor Interface I/O Timing 87

Intel Interface Timing - Asynchronous 87

Intel Asynchronous Programmed I/O Interface Timing 87

Asynchronous Mode 1 - Intel 8051 and 80188 Interface Timing 88

Motorola Asychronous Interface Timing 89

Motorola 68K Asynchronous Programmed I/O Interface Timing 89

Asynchronous - Motorola 68K - Interface Timing Specification 89

Microprocessor Interface Timing - Reset Pulse Width 89

Package dimensions 90

225 Ball Plastic Ball Grid Array (Bottom View) 90

(19.0 x 19.0 x 1.0mm) 90

**ORDERING INFORMATION 91**

**REVISIONS 91**

# PIN DESCRIPTION BY FUNCTION

# **RECEIVE SECTIONS**

| SIGNAL NAME      | LEAD#      | Түре | DESCRIPTION                                                                                                                                                                                                                                                            |

|------------------|------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RxON             | K16        | I    | Receiver On - Harware Mode                                                                                                                                                                                                                                             |

|                  |            |      | Writing a "1" to this pin in <b>Hardware</b> mode turns on the Receive Sections of all channels. Writing a "0" shuts off the Receiver Sections of all channels.                                                                                                        |

| RLOS_0           | C3         | 0    | Receiver Loss of Signal for Channel_ 0:                                                                                                                                                                                                                                |

|                  |            |      | This output signal goes "High" for at least one RCLK_0 cycle to indicate loss of signal at the receive 0 input. RLOS will remain "High" for the entire duration of the Loss of Signal detected by the receiver logic.  SEE"RECEIVER LOSS OF SIGNAL (RLOS)" ON PAGE 25. |

| DI 00 4          | 114        |      | Receiver Loss of Signal for Channel _1                                                                                                                                                                                                                                 |

| RLOS_1           | H4         |      | Receiver Loss of Signal for Channel 2                                                                                                                                                                                                                                  |

| RLOS_2<br>RLOS_3 | H15<br>A16 |      | Receiver Loss of Signal for Channel _3                                                                                                                                                                                                                                 |

| RLOS_3           | V3         |      | Receiver Loss of Signal for Channel _4                                                                                                                                                                                                                                 |

| RLOS_4<br>RLOS 5 | L2         |      | Receiver Loss of Signal for Channel 5                                                                                                                                                                                                                                  |

| RLOS_5           | J15        |      | Receiver Loss of Signal for Channel _6                                                                                                                                                                                                                                 |

| RLOS_7           | T15        |      | Receiver Loss of Signal for Channel _7                                                                                                                                                                                                                                 |

| RCLK 0           | B3         | 0    | Receiver Clock Output for Channel _0                                                                                                                                                                                                                                   |

| RCLK_1           | НЗ         |      | Receiver Clock Output for Channel _1                                                                                                                                                                                                                                   |

| RCLK_2           | H16        |      | Receiver Clock Output for Channel _2                                                                                                                                                                                                                                   |

| RCLK_3           | A17        |      | Receiver Clock Output for Channel _3                                                                                                                                                                                                                                   |

| RCLK_4           | U3         |      | Receiver Clock Output for Channel _4                                                                                                                                                                                                                                   |

| RCLK_5           | L3         |      | Receiver Clock Output for Channel _5                                                                                                                                                                                                                                   |

| RCLK_6           | M15        |      | Receiver Clock Output for Channel _6                                                                                                                                                                                                                                   |

| RCLK_7           | U16        |      | Receiver Clock Output for Channel _7                                                                                                                                                                                                                                   |

| RNEG_0           | A2         | 0    | Receiver Negative Data Output for Channel_0 - Dual-Rail mode                                                                                                                                                                                                           |

| 1.00/.0          | 4.0        |      | This signal is the receive negative-rail output data.                                                                                                                                                                                                                  |

| LCV_0            | A2         |      | Line Code Violation Output for Channel_0 - Single-Rail mode                                                                                                                                                                                                            |

|                  |            |      | This signal goes "High" for one RCLK_0 cycle to indicate a code violation is detected in the received data of Channel 0. If AMI coding is selected, every bipolar violation                                                                                            |

|                  |            |      | received will cause this pin to go "High".                                                                                                                                                                                                                             |

| RNEG 1           | H2         |      | Receiver Negative Data Output for Channel _1                                                                                                                                                                                                                           |

| LCV_1            | 112        |      | Line Code Violation Output for Channel _1                                                                                                                                                                                                                              |

| RNEG 2           | H18        |      | Receiver Negative Data Output for Channel _2                                                                                                                                                                                                                           |

| LCV_2            | 1110       |      | Line Code Violation Output for Channel _2                                                                                                                                                                                                                              |

| RNEG 3           | B16        |      | Receiver Negative Data Output for Channel _3                                                                                                                                                                                                                           |

| LCV_3            | 2.0        |      | Line Code Violation Output for Channel _3                                                                                                                                                                                                                              |

| RNEG 4           | T4         |      | Receiver Negative Data Output for Channel _4                                                                                                                                                                                                                           |

| LCV 4            |            |      | Line Code Violation Output for Channel _4                                                                                                                                                                                                                              |

| RNEG_5           | M4         |      | Receiver Negative Data Output for Channel _5                                                                                                                                                                                                                           |

| LCV_5            |            |      | Line Code Violation Output for Channel _5                                                                                                                                                                                                                              |

| RNEG_6           | M16        |      | Receiver Negative Data Output for Channel _6                                                                                                                                                                                                                           |

| LCV_6            |            |      | Line Code Violation Output for Channel _6                                                                                                                                                                                                                              |

| RNEG_7           | V17        |      | Receiver Negative Data Output for Channel _7                                                                                                                                                                                                                           |

| LCV_7            |            |      | Line Code Violation Output for Channel _7                                                                                                                                                                                                                              |

| RE   | <i>V</i> | 1  | n  | 1 |

|------|----------|----|----|---|

| / II | ν.       | Ι. | v. |   |

| SIGNAL NAME | LEAD# | Түре | DESCRIPTION                                                                      |

|-------------|-------|------|----------------------------------------------------------------------------------|

| RPOS_0      | B2    | 0    | Receiver Positive Data Output for Channel _0 - Dual-Rail mode                    |

|             |       |      | This signal is the receive positive-rail output data sent to the Framer.         |

|             |       |      | Receiver NRZ Data Output for Channel _0 - Single-Rail mode                       |

| RDATA_0     | B2    |      | This signal is the receive output data.                                          |

|             |       |      | Receiver Positive Data Output for Channel _1                                     |

| RPOS_1      | G2    |      | Receiver NRZ Data Output for Channel _1                                          |

| RDATA_1     |       |      | Receiver Positive Data Output for Channel _2                                     |

| RPOS_2      | D15   |      | Receiver NRZ Data Output for Channel _2                                          |

| RDATA_2     |       |      | Receiver Positive Data Output for Channel _3                                     |

| RPOS_3      | B17   |      | Receiver NRZ Data Output for Channel _3                                          |

| RDATA_3     |       |      | Receiver Positive Data Output for Channel _4                                     |

| RPOS_4      | U2    |      | Receiver NRZ Data Output for Channel _4                                          |

| RDATA_4     |       |      | Receiver Positive Data Output for Channel _5                                     |

| RPOS_5      | M3    |      | Receiver NRZ Data Output for Channel _5                                          |

| RDATA_5     |       |      | Receiver Positive Data Output for Channel _6                                     |

| RPOS_6      | L17   |      | Receiver NRZ Data Output for Channel 6                                           |

| RDATA_6     |       |      | Receiver Positive Data Output for Channel _7                                     |

| RPOS_7      | T17   |      | Receiver NRZ Data Output for Channel _7                                          |

| RDATA_7     |       |      |                                                                                  |

| RTIP_0      | C1    | ı    | Receiver Differential Tip Input for Channel _0                                   |

|             |       |      | Positive differential receive input from the line                                |

| RTIP_1      | G1    |      | Receiver Differential Tip Input for Channel _1                                   |

| RTIP_2      | G18   |      | Receiver Differential Tip Input for Channel _2                                   |

| RTIP_3      | C18   |      | Receiver Differential Tip Input for Channel _3                                   |

| RTIP_4      | U1    |      | Receiver Differential Tip Input for Channel _4                                   |

| RTIP_5      | L1    |      | Receiver Differential Tip Input for Channel _5                                   |

| RTIP_6      | L18   |      | Receiver Differential Tip Input for Channel _6                                   |

| RTIP_7      | T18   |      | Receiver Differential Tip Input for Channel _7                                   |

| RRING_0     | D1    | ı    | Receiver Differential Ring Input for Channel _0                                  |

|             |       |      | Negative differential receive input from the line                                |

| RRING_1     | F1    |      | Receiver Differential Ring Input for Channel _1                                  |

| RRING_2     | F18   |      | Receiver Differential Ring Input for Channel _2                                  |

| RRING_3     | D18   |      | Receiver Differential Ring Input for Channel _3                                  |

| RRING_4     | T1    |      | Receiver Differential Ring Input for Channel _4                                  |

| RRING_5     | M1    |      | Receiver Differential Ring Input for Channel _5                                  |

| RRING_6     | M18   |      | Receiver Differential Ring Input for Channel _6                                  |

| RRING_7     | R18   |      | Receiver Differential Ring Input for Channel _7                                  |

| RXMUTE      | T12   | I    | Receive Data Muting                                                              |

|             |       |      | When a LOS condition occurs, the outputs RPOS_n/RNEG_n will be muted, (forced to |

|             |       |      | ground) to prevent data chattering.                                              |

|             |       |      | Tie this pin "Low" to disable the muting function.  Notes:                       |

|             |       |      | 1. This pin is internally pulled "High" with a $50k\Omega$ resistor.             |

|             |       |      | 2. In <b>Hardware mode</b> , all receive channels share the same RXMUTE control  |

|             |       |      | function.                                                                        |

OCTAL T1/E1/J1 LH/SH TRANSCEIVER WITH CLOCK RECOVERY AND JITTER ATTENUATOR

| SIGNAL NAME      | LEAD #     | TYPE |                                                                                                                                                                                                                                                                                                                                                                                                         | DES                                                                              | CRIPTION                               |  |  |  |  |  |

|------------------|------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------|--|--|--|--|--|

| RXRES1<br>RXRES0 | R10<br>V10 | 1    | Receive External Resistor Control Pins - Hardware mode Receive External Resistor Control Pin 1: Receive External Resistor Control Pin 0: These pins determine the value of the external Receive fixed resistor according to the following table:                                                                                                                                                        |                                                                                  |                                        |  |  |  |  |  |

|                  |            |      | RXRES                                                                                                                                                                                                                                                                                                                                                                                                   | 1 RXRESO                                                                         | Required Fixed External<br>RX Resistor |  |  |  |  |  |

|                  |            |      | 0                                                                                                                                                                                                                                                                                                                                                                                                       | 0                                                                                | No External Fixed Resistor             |  |  |  |  |  |

|                  |            |      | 0                                                                                                                                                                                                                                                                                                                                                                                                       | 1                                                                                | 240Ω                                   |  |  |  |  |  |

|                  |            |      | 1                                                                                                                                                                                                                                                                                                                                                                                                       | 0                                                                                | 210Ω                                   |  |  |  |  |  |

|                  |            |      | 1                                                                                                                                                                                                                                                                                                                                                                                                       | 1                                                                                | 150Ω                                   |  |  |  |  |  |

|                  |            |      | Note: These pins are                                                                                                                                                                                                                                                                                                                                                                                    | <b>Note:</b> These pins are internally pulled "Low" with a $50k\Omega$ resistor. |                                        |  |  |  |  |  |

| RCLKE<br>µPTS1   | J16        | ı    | Receive Clock Edge - Hardware mode  Set this pin "High" to sample RPOS_N/RNEG_n on the falling edge of RCLK_n. With this pin tied "Low", output data are updated on the rising edge of RCLK_n.  Microprocessor Type Select Input pin 1 - Host mode  This pin along with µPTS2 (pin 128) is used to select the microprocessor type.  SEE"MICROPROCESSOR TYPE SELECT INPUT PINS - HOST MODE:" ON PAGE 12. |                                                                                  |                                        |  |  |  |  |  |

# TRANSMITTER SECTIONS

| SIGNAL NAME | LEAD# | Түре | DESCRIPTION                                                                                                                                                     |

|-------------|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E           | L15   | ı    | Transmit Clock Edge - Hardware mode                                                                                                                             |

|             |       |      | Set this pin "High" to sample transmit input data on the rising edge of TCLK_n. With this pin tied "Low", input data are sampled on the falling edge of TCLK_n. |

|             |       |      | Microprocessor Type Select Input pin 2 - Host mode                                                                                                              |

| μPTS2       | L15   |      | This pin along with µPTS1 (pin 133) selects the microprocessor type. SEE"MICRO-PROCESSOR TYPE SELECT INPUT PINS - HOST MODE:" ON PAGE 12.                       |

|             |       |      | <b>Note:</b> This pin is internally pulled "Low" with a 50kΩ resistor.                                                                                          |

| TTIP_0      | E3    | 0    | Transmitter Tip Output for Channel _0                                                                                                                           |

|             |       |      | Positive differential transmit output to the line.                                                                                                              |

| TTIP_1      | G4    |      | Transmitter Tip Output for Channel _1                                                                                                                           |

| TTIP_2      | F17   |      | Transmitter Tip Output for Channel _2                                                                                                                           |

| TTIP_3      | C16   |      | Transmitter Tip Output for Channel _3                                                                                                                           |

| TTIP_4      | R2    |      | Transmitter Tip Output for Channel _4                                                                                                                           |

| TTIP_5      | N2    |      | Transmitter Tip Output for Channel _5                                                                                                                           |

| TTIP_6      | N16   |      | Transmitter Tip Output for Channel _6                                                                                                                           |

| TTIP_7      | P16   |      | Transmitter Tip Output for Channel _7                                                                                                                           |

# EXAR Powering Connectivity

# OCTAL T1/E1/J1 LH/SH TRANSCEIVER WITH CLOCK RECOVERY AND JITTER ATTENUATOR

REV. 1.0.1

| SIGNAL NAME | LEAD# | Түре | DESCRIPTION                                                                        |  |

|-------------|-------|------|------------------------------------------------------------------------------------|--|

| TRING_0     | E2    | 0    | Transmitter Ring Output for Channel _0                                             |  |

|             |       |      | Negative differential transmit output to the line.                                 |  |

| TRING_1     | F3    |      | Transmitter Ring Output for Channel _1                                             |  |

| TRING_2     | F15   |      | Transmitter Ring Output for Channel _2                                             |  |

| TRING_3     | E16   |      | Transmitter Ring Output for Channel _3                                             |  |

| TRING_4     | P2    |      | Transmitter Ring Output for Channel _4                                             |  |

| TRING_5     | N4    |      | Transmitter Ring Output for Channel _5                                             |  |

| TRING_6     | R15   |      | Transmitter Ring Output for Channel _6                                             |  |

| TRING_7     | P17   |      | Transmitter Ring Output for Channel _7                                             |  |

| TPOS_0      | C5    | ı    | Transmitter Positive Data Input for Channel _0 - Dual-Rail mode                    |  |

|             |       |      | This signal is the positive-rail input data for transmitter 0.                     |  |

| TDATA_0     |       |      | Transmitter 0 Data Input - Single-Rail mode                                        |  |

|             |       |      | This pin is used as the NRZ input data for transmitter 0.                          |  |

| TPOS_1      | A4    |      | Transmitter Positive Data Input for Channel _1                                     |  |

| TDATA_1     |       |      | Transmitter 1 Data Input                                                           |  |

| TPOS_2      | B14   |      | Transmitter Positive Data Input for Channel _2                                     |  |

| TDATA_2     |       |      | Transmitter 2 Data Input                                                           |  |

| TPOS_3      | D14   |      | Transmitter Positive Data Input for Channel _3                                     |  |

| TDATA_3     |       |      | Transmitter 3 Data Input                                                           |  |

| TPOS_4      | V4    |      | Transmitter Positive Data Input for Channel _4                                     |  |

| TDATA_4     |       |      | Transmitter 4 Data Input                                                           |  |

| TPOS_5      | U5    |      | Transmitter Positive Data Input for Channel _5                                     |  |

| TDATA_5     |       |      | Transmitter 5 Data Input                                                           |  |

| TPOS_6      | V15   |      | Transmitter Positive Data Input for Channel _6                                     |  |

| TDATA_6     |       |      | Transmitter 6 Data Input                                                           |  |

| TPOS_7      | T14   |      | Transmitter Positive Data Input for Channel _7                                     |  |

| TDATA_7     |       |      | Transmitter 7 Data Input                                                           |  |

|             |       |      | <b>Note:</b> Internally pulled "Low" with a $50k\Omega$ resistor for each channel. |  |

| SIGNAL NAME            | LEAD#      | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                     |

|------------------------|------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TNEG_0                 | C4         | ı    | Transmitter Negative NRZ Data Input for Channel _0 Dual-Rail mode This signal is the negative-rail input data for transmitter 0. Single-Rail mode This pin can be left unconnected.                                                                                                                                                                             |

| CODES_0                | C4         |      | Coding Select for Channel _0 - Hardware mode and Single-Rail mode  Connecting this pin "Low" enables HDB3 in E1 or B8ZS in T1 encoding and decoding for Channel _0. Connecting this pin "High" selects AMI data format.                                                                                                                                         |

| TNEG_1                 | B5         |      | Transmitter Negative NRZ Data Input for Channel _1 Coding Select for Channel _1                                                                                                                                                                                                                                                                                 |

| CODES_1 TNEG_2         | D13        |      | Transmitter Negative NRZ Data Input for Channel _2 Coding Select for Channel _2                                                                                                                                                                                                                                                                                 |

| CODES_2 TNEG_3         | B15        |      | Transmitter Negative NRZ Data Input for Channel _3 Coding Select for Channel _3                                                                                                                                                                                                                                                                                 |

| CODES_3 TNEG_4         | U4         |      | Transmitter Negative NRZ Data Input for Channel _4 Coding Select for Channel _4                                                                                                                                                                                                                                                                                 |

| CODES_4 TNEG_5 CODES_5 | V5         |      | Transmitter Negative NRZ Data Input for Channel _5  Coding Select for Channel _5                                                                                                                                                                                                                                                                                |

| TNEG_6                 | U14        |      | Transmitter Negative NRZ Data Input for Channel _6 Coding Select for Channel _6                                                                                                                                                                                                                                                                                 |

| CODES_6<br>TNEG_7      | R14        |      | Transmitter Negative NRZ Data Input for Channel _7 Coding Select for Channel _7                                                                                                                                                                                                                                                                                 |

| CODES_7                |            |      | <b>Note:</b> Internally pulled "Low" with a $50k\Omega$ resistor for each channel.                                                                                                                                                                                                                                                                              |

| TCLK_0                 | B4         | I    | Transmitter Clock Input for Channel _0 - Host mode and Hardware mode E1 rate at 2.048MHz ± 50ppm. T1 rate at 1.544MHz ± 32ppm.  During normal operation TCLK_0 is used for sampling input data at TPOS_0/ TDATA_0 and TNEG_0/CODES_0 while MCLK is used as the timing reference for the transmit pulse shaping circuit.  Transmitter Clock Input for Channel _1 |

| TCLK_1                 | A3         |      | Transmitter Clock Input for Channel _2 Transmitter Clock Input for Channel _3                                                                                                                                                                                                                                                                                   |

| TCLK_2<br>TCLK_3       | A15<br>C14 |      | Transmitter Clock Input for Channel _4                                                                                                                                                                                                                                                                                                                          |

| TCLK_4                 | T3         |      | Transmitter Clock Input for Channel _5                                                                                                                                                                                                                                                                                                                          |

| TCLK_5                 | T5         |      | Transmitter Clock Input for Channel _6                                                                                                                                                                                                                                                                                                                          |

| TCLK_6<br>TCLK_7       | V16<br>U15 |      | Transmitter Clock Input for Channel _7  Note: Internally pulled "Low" with a 50kΩ resistor for all channels.                                                                                                                                                                                                                                                    |

REV. 1.0.1

| SIGNAL NAME                                              | LEAD#                                         | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------------------------------------------|-----------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TAOS_0                                                   | D6                                            | I    | Transmit All Ones for Channel _0 - Hardware mode  Setting this pin "High" enables the transmission of an "All Ones" Pattern from Channel _0. A "Low" level stops the transmission of the "All Ones" Pattern.  Transmit All Ones for Channel _1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| TAOS_1 TAOS_2 TAOS_3 TAOS_4 TAOS_5 TAOS_6 TAOS_7         | B6<br>A5<br>C6<br>T6<br>U6<br>V6<br>R6        |      | Transmit All Ones for Channel _2 Transmit All Ones for Channel _3 Transmit All Ones for Channel _4 Transmit All Ones for Channel _5 Transmit All Ones for Channel _6 Transmit All Ones for Channel _7 Note: Internally pulled "Low" with a 50kΩ resistor for all channels.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| TXON_0  TXON_1 TXON_2 TXON_3 TXON_4 TXON_5 TXON_6 TXON_7 | D12<br>C12<br>B12<br>V13<br>U13<br>R12<br>R13 |      | Transmitter Turn On for Channel _0 Hardware mode  Setting this pin "High" turns on the Transmit and Receive Sections of Channel _0. When TXON_0 = "0" then TTIP_0 and TRING_0 driver outputs will be tri-stated.  In Host mode  The TXON_n bits in the channel control registers turn each channel Transmit and Receive section ON or OFF. However, control of the on/off function can be transferred to the Hardware pins by setting the TXONCNTL bit (bit 7) to "1" in the register at address hex 0x82.  Transmitter Turn On for Channel _1 Transmitter Turn On for Channel _2 Transmitter Turn On for Channel _3 Transmitter Turn On for Channel _4 Transmitter Turn On for Channel _5 Transmitter Turn On for Channel _6 Transmitter Turn On for Channel _7  Note: Internally pulled "Low" with a 50kΩ resistor for all channels. |

# OCTAL T1/E1/J1 LH/SH TRANSCEIVER WITH CLOCK RECOVERY AND JITTER ATTENUATOR

# MICROPROCESSOR INTERFACE

| SIGNAL NAME | LEAD#      | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|-------------|------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| HW_HOST     | T10        | I    | Mode Control Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|             |            |      | This pin selects <b>Hardware</b> or <b>Host mode</b> . Leave this pin unconnected or tie "High" to select <b>Hardware mode</b> .                                                                                                                                                                                                                                                                                                                                                        |  |

|             |            |      | For <b>Host mode</b> , this pin must be tied "Low".                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|             |            |      | <b>Note:</b> Internally pulled "High" with a $50k\Omega$ resistor.                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| WR_R/W      | D7         | I    | Write Input (Read/Write) - Host mode: Intel bus timing: A "Low" pulse on WR selects a write operation when CS pin is "Low".  Motorola bus timing: A "High" pulse on R/W selects a read operation and a "Low"                                                                                                                                                                                                                                                                            |  |

| EQC0        | D7         |      | pulse on R/W selects a write operation when $\overline{CS}$ is "Low". <b>Equalizer Control Input pin 0 - Hardware mode</b> Pins EQC0, EQC1, EQC2, EQC3 and EQC4 select the Receive Equalizer and Transmitter Line Build Out. <b>SEE</b> "RECEIVE EQUALIZER CONTROL AND TRANSMIT LINE BUILD-OUT SETTINGS" ON PAGE 31. <b>Note:</b> Internally pulled "Low" with a 50kΩ resistor.                                                                                                         |  |

| RD_DS       | C7         | I    | Read Input (Data Strobe) - Host mode                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| EQC1        | <b>C</b> 7 |      | Intel bus timing: A "Low" pulse on RD selects a read operation when the CS pin is "Low".  Motorola bus timing: A "Low" pulse on DS indicates a read or write operation when the CS pin is "Low".  Equalizer Control Input pin 1 - Hardware mode  Pins EQC0, EQC1, EQC2, EQC3 and EQC4 select the Receive Equalizer and Transmitter Line Build Out. SEE"RECEIVE EQUALIZER CONTROL AND TRANSMIT LINE BUILD-OUT SETTINGS" ON PAGE 31.  Note: Internally pulled "Low" with a 50kΩ resistor. |  |

| ALE_AS      | A7         | ı    | Address Latch Input (Address Strobe) - Host mode Intel bus timing: The address inputs are latched into the internal register on the falling edge of ALE.  Motorola bus timing: The address inputs are latched into the internal register on the falling edge of AS.                                                                                                                                                                                                                     |  |

| EQC2        | A7         |      | Equalizer Control Input pin 2 - Hardware mode  Pins EQC0, EQC1, EQC2, EQC3 and EQC4 select the Receive Equalizer and  Transmitter Line Build Out. SEE"RECEIVE EQUALIZER CONTROL AND  TRANSMIT LINE BUILD-OUT SETTINGS" ON PAGE 31.  Note: Internally pulled "Low" with a 50kΩ resistor.                                                                                                                                                                                                 |  |

| CS          | B7         | I    | Chip Select Input - Host mode:                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| EQC3        | В7         |      | This signal must be "Low" in order to access the parallel port. <b>Equalizer Control Input pin 3 - Hardware mode:</b> Pins EQC0, EQC1, EQC2, EQC3 and EQC4 select the Receive Equalizer and Transmitter Line Build Out. <b>SEE"RECEIVE EQUALIZER CONTROL AND TRANSMIT LINE BUILD-OUT SETTINGS" ON PAGE 31. Note:</b> Internally pulled "Low" with a 50kΩ resistor.                                                                                                                      |  |

| SIGNAL NAME                                                                                  | LEAD#                                   | Түре |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                   | DESCRIPTION                                                                                                                                                                                                |  |  |

|----------------------------------------------------------------------------------------------|-----------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| RDY_DTACK                                                                                    | A6<br>A6                                | ı    | Ready Output (Data Transfer Acknowledge Output) - Host mode Intel bus timing: RDY is asserted "High" to indicate the device has completed a read or write operation.  Motorola bus timing: DTACK is asserted "Low" to indicate the device has completed a read or write cycle.  Equalizer Control Input pin 4 - Hardware mode  Pins EQC0, EQC1, EQC2, EQC3 and EQC4 select the Receive Equalizer and Transmitter Line Build Out. SEE"RECEIVE EQUALIZER CONTROL AND TRANSMIT LINE BUILD-OUT SETTINGS" ON PAGE 31.  Note: Internally pulled "Low" with a 50kΩ resistor. |                                                                   |                                                                                                                                                                                                            |  |  |

| μPTS1<br>μPTS2                                                                               | J16<br>L15                              | ı    | Microprocessor Microprocessor Microprocessor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Type Select                                                       |                                                                                                                                                                                                            |  |  |

|                                                                                              |                                         |      | μPTS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | μPTS1                                                             | <b>µ</b> Р Туре                                                                                                                                                                                            |  |  |

|                                                                                              |                                         |      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                                                 | Intel 8051 Asynchronous                                                                                                                                                                                    |  |  |

|                                                                                              |                                         |      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                                                 | Motorola Asynchronous                                                                                                                                                                                      |  |  |

|                                                                                              |                                         |      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                                                 | Power PC Synchronous                                                                                                                                                                                       |  |  |

|                                                                                              |                                         |      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                                                 | MPC8xx Motorola Synchronous                                                                                                                                                                                |  |  |

| RCLKE<br>TCLKE                                                                               | J16<br>L15                              |      | Transmit Clock SEE"TRANSM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | E CLOCK E<br>Edge - Hardv<br>IIT CLOCK I                          | DGE - HARDWARE MODE" ON PAGE 7.                                                                                                                                                                            |  |  |