Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

### Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

#### XRT83VSH28

#### 8-CHANNEL E1 SHORT-HAUL LINE INTERFACE UNIT

MARCH 2010 REV. 2.0.0

#### **GENERAL DESCRIPTION**

The XRT83VSH28 is a fully integrated 8-channel short-haul line interface unit (LIU) that operates from a 1.8V and a 3.3V power supply. Using internal termination, the LIU provides one bill of materials to operate in E1  $75\Omega$  or  $120\Omega$  mode with minimum external components. The LIU features are programmed through a standard parallel or serial microprocessor interface. EXAR's LIU has patented high impedance circuits that allow the transmitter outputs and receiver inputs to be high impedance when experiencing a power failure or when the LIU is powered off. Key design features within the LIU optimize 1:1 or 1+1 redundancy and non-intrusive monitoring applications to ensure reliability without using relays.

The on-chip clock synthesizer generates an E1 clock reference.

Additional features include RLOS, a 16-bit LCV counter for each channel, AIS, QRSS generation/detection, TAOS, DMO, and diagnostic loopback modes.

#### **APPLICATIONS**

- ISDN Primary Rate Interface

- CSU/DSU E1 Interface

- E1 LAN/WAN Routers

- Public switching Systems and PBX Interfaces

- E1 Multiplexer and Channel Banks

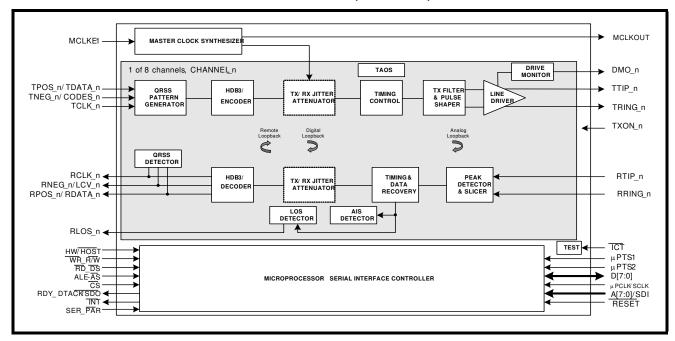

FIGURE 1. BLOCK DIAGRAM OF THE XRT83VSH28 E1 LIU (HOST MODE)

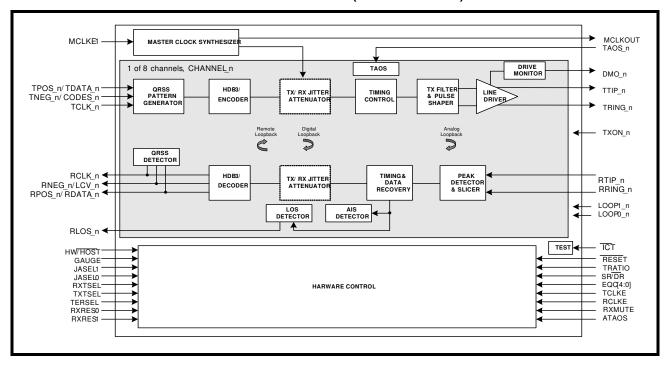

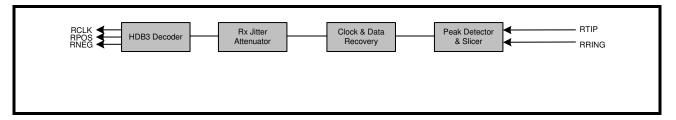

#### FIGURE 2. BLOCK DIAGRAM OF THE XRT83VSH28 E1 LIU (HARDWARE MODE)

#### **FEATURES**

- Fully integrated eight channel short-haul transceivers for E1 (2.048MHz) applications

- Internal Impedance matching on both receive and transmit for 75Ω (E1) and 120Ω (E1) applications are per port selectable through software without changing components

- Power down on a per channel basis with independent receive and transmit selection

- User programable Arbitrary Pulse mode

- On-Chip transmit short-circuit protection and limiting protects line drivers from damage on a per channel basis

- Selectable Crystal-Less digital jitter attenuators (JA) with 32-Bit or 64-Bit FIFO for the receive or transmit

path

- Driver failure monitor output (DMO) alerts of possible system or external component problems

- Transmit outputs and receive inputs may be "High" impedance for protection or redundancy applications on a per channel basis

- Support for automatic protection switching

- 1:1 and 1+1 protection without relays

- Receive monitor mode handles 0 to 6dB resistive attenuation (flat loss) along with 0 to 6dB cable loss

- Loss of signal (RLOS) according to ITU-T G.775/ETS300233 (E1)

- Programmable data stream muting upon RLOS detection

- On-Chip HDB3 encoder/decoder with an internal 16-bit LCV counter for each channel

- On-Chip digital clock recovery circuit for high input jitter tolerance

- QRSS/PRBS pattern generator and detection for testing and monitoring

- Error and bipolar violation insertion and detection

- Transmit all ones (TAOS) Generators and Detectors

- Supports local analog, remote, digital, and dual loopback modes

- Supports gapped clocks for mapper/multiplexer applications

- 1.8V Inner Core

- 3.3V I/O Supply Operation

- 225 ball BGA package

- -40°C to +85°C Temperature Range

#### ORDERING INFORMATION

| PART NUMBER  | PACKAGE      | OPERATING TEMPERATURE RANGE |  |  |

|--------------|--------------|-----------------------------|--|--|

| XRT83VSH28IB | 225 Ball BGA | -40°C to +85°C              |  |  |

| Powering  |

|-----------|

| Connectiv |

|           |

| Α | DGND     | RNEG_0  | TCLK_1  | TPOS_1  | TAOS_2 | RDY    | ALE    | Reserved | DVDD1v8 | A[1]    | A[3]     | A[7]   | TXON_0 | JASEL0 | TCLK_2  | RLOS_3  | RCLK_3  | DVDD3v3  |

|---|----------|---------|---------|---------|--------|--------|--------|----------|---------|---------|----------|--------|--------|--------|---------|---------|---------|----------|

| В | TDO      | RPOS_0  | RCLK_0  | TCLK_0  | TNEG_1 | TAOS_1 | CS     | Reserved | DGND    | A[2]    | A[6]     | TX0N_3 | JASEL1 | TPOS_2 | TNEG_3  | RNEG_3  | RPOS_3  | JTAGRing |

| С | RTIP_0   | RVDD    | RLOS_0  | TNEG_0  | TPOS_0 | TAOS_3 | RD_DS  | Reserved | DGND    | A[0]    | A[5]     | TXON_2 | DMO_3  | TCLK_3 | DMO_2   | TTIP_3  | TGND    | RTIP_3   |

| D | RRING_0  | RGND    | TGND    | DMO_1   | DMO_0  | TAOS_0 | WR_R/W | DGND     | DVDD3v3 | DVDD1v8 | A[4]     | TXON_1 | TNEG_2 | TPOS_3 | RPOS_2  | RVDD    | RGND    | RRING_3  |

| Ε | TMS      | TRING_O | TTIP_0  | TVDD    | RVDD   |        |        |          |         |         |          |        |        |        | TGND    | TRING_3 | TVDD    | JTAGTip  |

| F | RRING_1  | TGND    | TRING_1 | TVDD    |        |        |        |          |         |         |          |        |        |        | TRING_2 | TVDD    | TTIP_2  | RRING_2  |

| G | RTIP_1   | RPOS_1  | RGND    | TTIP_1  |        |        |        |          |         |         |          |        |        |        | DGND    | RVDD    | RGND    | RTIP_2   |

| Н | MCLKOUT  | RNEG_1  | RCLK_1  | RLOS_1  |        |        |        |          |         |         |          |        |        |        | RLOS_2  | RCLK_2  | DGND    | RNEG_2   |

| J | MCLKE1   | AVDD    | AVDD    | DVDD3v3 |        |        |        | )        | (RT83   | SVSH2   | В        |        |        |        | RLOS_6  | μPTS1   | AGND    | GAUGE    |

| K | Reserved | DGND    | AGND    | SR/DR   |        |        |        |          | (Тор    | View)   |          |        |        |        | DVDD3v3 | RXON    | AVDDS   | DVDD1v8  |

| L | RTIP_5   | RLOS_5  | RCLK_5  | AGND    |        |        |        |          | 225 Ba  | all BGA |          |        |        |        | μPTS2   | ĪNT     | RPOS_6  | RTIP_6   |

| М | RRING_5  | RGND    | RPOS_5  | RNEG_5  |        |        |        |          |         |         |          |        |        |        | RCLK_6  | RNEG_6  | RGND    | RRING_6  |

| N | TCK      | TTIP_5  | RVDD    | TRING_5 |        |        |        |          |         |         |          |        |        |        | TVDD    | TTIP_6  | RVDD    | NC       |

| Ρ | TVDD     | TRING_4 | TGND    | DMO_5   |        |        |        |          |         |         |          |        |        |        | TVDD    | TTIP_7  | TRING_7 | SER_PAR  |

| R | TDI      | TTIP_4  | TGND    | TVDD    | DMO_4  | TAOS_7 | D[0]   | DGND     | DVDD3v3 | RXRES1  | TERSEL   | TXON_6 | TXON_7 | TNEG_7 | TRING_6 | TGND    | RGND    | RRING_7  |

| Т | RRING_4  | RGND    | TCLK_4  | RNEG_4  | TCLK_5 | TAOS_4 | D[7]   | RESET    | DGND    | HW_HOST | Reserved | RXMUTE | μPCLK  | TPOS_7 | RLOS_7  | TGND    | RPOS_7  | RTIP_7   |

| U | RTIP_4   | RPOS_4  | RCLK_4  | TNEG_4  | TPOS_5 | TAOS_5 | D[6]   | D[2]     | D[1]    | DVDD1v8 | RXTSEL   | TEST   | TXON_5 | TNEG_6 | TCLK_7  | RCLK_7  | DMO_6   | RVDD     |

| ٧ | DVDD1v8  | RVDD    | RLOS_4  | TPOS_4  | TNEG_5 | TAOS_6 | D[5]   | D[4]     | D[3]    | RXRES0  | TXTSEL   | ĪCT    | TXON_4 | DMO_7  | TPOS_6  | TCLK_6  | RNEG_7  | DGND     |

| ľ | 1        | 2       | 3       | 4       | 5      | 6      | 7      | 8        | 9       | 10      | 11       | 12     | 13     | 14     | 15      | 16      | 17      | 18       |

| GENERAL DESCRIPTION                                                               | 1        |

|-----------------------------------------------------------------------------------|----------|

| Applications                                                                      | 1        |

| FIGURE 1. BLOCK DIAGRAM OF THE XRT83VSH28 E1 LIU (HOST MODE)                      |          |

| FIGURE 2. BLOCK DIAGRAM OF THE XRT83VSH28 E1 LIU (HARDWARE MODE)                  |          |

| FEATURES                                                                          |          |

| ORDERING INFORMATION                                                              |          |

| PIN DESCRIPTION BY FUNCTION                                                       | 5        |

| RECEIVE SECTION                                                                   | 5        |

| TRANSMIT SECTION                                                                  | 8        |

| PARALLEL MICROPROCESSOR INTERFACE                                                 |          |

| JITTER ATTENUATOR                                                                 |          |

|                                                                                   | 13       |

| CLOCK SYNTHESIZER                                                                 |          |

| ALARM FUNCTIONS/REDUNDANCY SUPPORT                                                | 14       |

| SERIAL MICROPROCESSOR INTERFACE                                                   |          |

| POWER AND GROUND                                                                  |          |

| FUNCTIONAL DESCRIPTION                                                            |          |

| 1.0 HARDWARE MODE VS HOST MODE                                                    |          |

| 1.1 FEATURE DIFFERENCES IN HARDWARE MODE                                          |          |

| TABLE 1: DIFFERENCES BETWEEN HARDWARE MODE AND HOST MODE                          |          |

| 2.0 RECEIVE PATH LINE INTERFACE                                                   | 20       |

| FIGURE 3. SIMPLIFIED BLOCK DIAGRAM OF THE RECEIVE PATH                            | 20       |

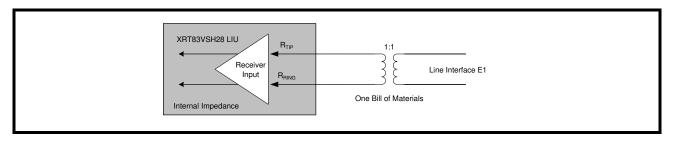

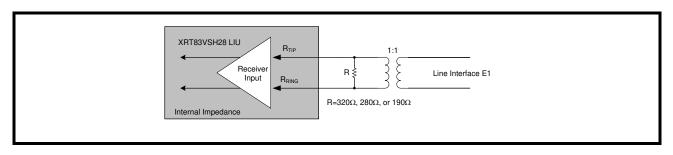

| 2.1 LINE TERMINATION (RTIP/RRING)                                                 |          |

| 2.1.1 CASE 1: INTERNAL TERMINATION                                                |          |

| TABLE 2: SELECTING THE INTERNAL IMPEDANCE                                         |          |

| 2.1.2 CASE 2: INTERNAL TERMINATION WITH ONE EXTERNAL FIXED RESISTOR FOR ALL MODES |          |

| TABLE 3: SELECTING THE VALUE OF THE EXTERNAL FIXED RESISTOR                       |          |

| FIGURE 5. TYPICAL CONNECTION DIAGRAM USING ONE EXTERNAL FIXED RESISTOR            |          |

| 2.2 CLOCK AND DATA RECOVERY                                                       |          |

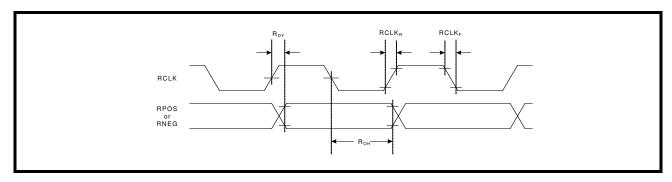

| FIGURE 6. RECEIVE DATA UPDATED ON THE RISING EDGE OF RCLK                         |          |

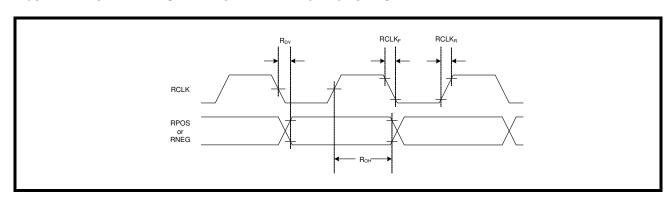

| FIGURE 7. RECEIVE DATA UPDATED ON THE FALLING EDGE OF RCLK                        | 22<br>22 |

| 2.2.1 RECEIVE SENSITIVITY                                                         |          |

| FIGURE 8. TEST CONFIGURATION FOR MEASURING RECEIVE SENSITIVITY                    |          |

| 2.2.2 INTERFERENCE MARGIN                                                         |          |

| FIGURE 9. TEST CONFIGURATION FOR MEASURING INTERFERENCE MARGIN                    |          |

| 2.2.3 GENERAL ALARM DETECTION AND INTERRUPT GENERATION                            |          |

| 2.4 HDB3 DECODER                                                                  |          |

| 2.5 RPOS/RNEG/RCLK                                                                |          |

| Figure 10. Single Rail Mode With a Fixed Repeating "0011" Pattern                 |          |

| Figure 11. Dual Rail Mode With a Fixed Repeating "0011" Pattern                   | _        |

| 2.6 RXMUTE (RECEIVER LOS WITH DATA MUTING)                                        |          |

| FIGURE 12. SIMPLIFIED BLOCK DIAGRAM OF THE RXMUTE FUNCTION                        |          |

| 3.0 TRANSMIT PATH LINE INTERFACE                                                  |          |

| 3.1 TCLK/TPOS/TNEG DIGITAL INPUTS                                                 |          |

| FIGURE 14. TRANSMIT DATA SAMPLED ON FALLING EDGE OF TCLK                          |          |

| FIGURE 15. TRANSMIT DATA SAMPLED ON RISING EDGE OF TCLK                           |          |

| TABLE 5: TIMING SPECIFICATIONS FOR TCLK/TPOS/TNEG                                 |          |

| 3.2 HDB3 ENCODER                                                                  |          |

| TABLE 6: EXAMPLES OF HDB3 ENCODING                                                | _        |

| 3.3 TRANSMIT JITTER ATTENUATOR                                                    |          |

| 3.4 TAOS (TRANSMIT ALL ONES)                                                      |          |

| FIGURE 16. TAOS (TRANSMIT ALL ONES)                                               |          |

| 3.5 TRANSMIT DIAGNOSTIC FEATURES                                                  | 29       |

| 3.5.1 ATAOS (AUTOMATIC TRANSMIT ALL ONES)                                         |          |

| FIGURE 17. SIMPLIFIED BLOCK DIAGRAM OF THE ATAOS FUNCTION                         |          |

| 3.5.2 QRSS GENERATION                                                             | 30       |

| 8-CHANNEL | F1 SHORT-HALL | I INF INTERFACE LINIT |

|-----------|---------------|-----------------------|

| XRT83VSH28                                                                          | Powering Connectivity |

|-------------------------------------------------------------------------------------|-----------------------|

| 8-CHANNEL E1 SHORT-HAUL LINE INTERFACE UNIT                                         | REV. 2.0.0            |

| TABLE 8: RANDOM BIT SEQUENCE POLYNOMIALS                                            |                       |

| 3.6 DMO (DIGITAL MONITOR OUTPUT)                                                    | 31                    |

| 3.7 LINE TERMINATION (TTIP/TRING)                                                   |                       |

| FIGURE 18. TYPICAL CONNECTION DIAGRAM USING INTERNAL TERMINATION                    | 31                    |

| 4.0 E1 APPLICATIONS                                                                 | 32                    |

| 4.1 LOOPBACK DIAGNOSTICS                                                            |                       |

| 4.1.1 LOCAL ANALOG LOOPBACK                                                         | 32                    |

| FIGURE 19. SIMPLIFIED BLOCK DIAGRAM OF LOCAL ANALOG LOOPBACK                        |                       |

| 4.1.2 REMOTE LOOPBACK                                                               |                       |

| FIGURE 20. SIMPLIFIED BLOCK DIAGRAM OF REMOTE LOOPBACK                              |                       |

| 4.1.3 DIGITAL LOOPBACK                                                              |                       |

| FIGURE 21. SIMPLIFIED BLOCK DIAGRAM OF DIGITAL LOOPBACK                             |                       |

| 4.1.4 DUAL LOOPBACK                                                                 |                       |

| FIGURE 22. SIMPLIFIED BLOCK DIAGRAM OF DUAL LOOPBACK                                |                       |

| 4.2 LINE CARD REDUNDANCY                                                            | 34                    |

| 4.2.1 1:1 AND 1+1 REDUNDANCY WITHOUT RELAYS                                         |                       |

| 4.2.2 TRANSMIT INTERFACE WITH 1:1 AND 1+1 REDUNDANCY                                |                       |

| FIGURE 23. SIMPLIFIED BLOCK DIAGRAM OF THE TRANSMIT INTERFACE FOR 1:1 AND 1+1 REDUN |                       |

| 4.2.3 RECEIVE INTERFACE WITH 1:1 AND 1+1 REDUNDANCY                                 |                       |

| FIGURE 24. SIMPLIFIED BLOCK DIAGRAM OF THE RECEIVE INTERFACE FOR 1:1 AND 1+1 REDUND |                       |

| 4.2.4 N+1 REDUNDANCY USING EXTERNAL RELAYS                                          |                       |

| 4.2.5 TRANSMIT INTERFACE WITH N+1 REDUNDANCY                                        |                       |

| 4.2.6 RECEIVE INTERFACE WITH N+1 REDUNDANCY                                         |                       |

| FIGURE 26. SIMPLIFIED BLOCK DIAGRAM OF THE RECEIVE INTERFACE FOR N+1 REDUNDANCY     |                       |

| 4.3 POWER FAILURE PROTECTION                                                        |                       |

| 4.4 OVERVOLTAGE AND OVERCURRENT PROTECTION                                          |                       |

| 4.5 NON-INTRUSIVE MONITORING                                                        |                       |

| FIGURE 27. SIMPLIFIED BLOCK DIAGRAM OF A NON-INTRUSIVE MONITORING APPLICATION       |                       |

|                                                                                     |                       |

| 5.0 MICROPROCESSOR INTERFACE                                                        |                       |

| 5.1 SERIAL MICROPROCESSOR INTERFACE BLOCK (BGA PACKAGE ONLY                         |                       |

| FIGURE 28. SIMPLIFIED BLOCK DIAGRAM OF THE SERIAL MICROPROCESSOR INTERFACE          |                       |

| 5.1.1 SERIAL TIMING INFORMATION                                                     |                       |

| FIGURE 29. TIMING DIAGRAM FOR THE SERIAL MICROPROCESSOR INTERFACE                   |                       |

| •                                                                                   |                       |

| 5.1.3 ADDR[7:0] (SCLK1 - SCLK8)                                                     |                       |

| 5.1.5 DUMMY BITS (SCLK10 - SCLK16)                                                  |                       |

| 5.1.6 DATA[7:0] (SCLK10 - SCLK24)                                                   |                       |

| 5.1.7 8-BIT SERIAL DATA OUTPUT DESCRIPTION                                          |                       |

| FIGURE 30. TIMING DIAGRAM FOR THE MICROPROCESSOR SERIAL INTERFACE                   |                       |

| TABLE 9: MICROPROCESSOR SERIAL INTERFACE TIMINGS (TA = 250C, VDD=3.3V± 5% AND LC    |                       |

| 5.2 PARALLEL MICROPROCESSOR INTERFACE BLOCK                                         |                       |

| TABLE 10: SELECTING THE MICROPROCESSOR INTERFACE MODE                               |                       |

| FIGURE 31. SIMPLIFIED BLOCK DIAGRAM OF THE MICROPROCESSOR INTERFACE BLOCK           |                       |

| 5.3 THE MICROPROCESSOR INTERFACE BLOCK SIGNALS                                      |                       |

| TABLE 11: XRT83VSH28 MICROPROCESSOR INTERFACE SIGNALS THAT EXHIBIT CONSTANT ROLE 43 |                       |

| TABLE 12: INTEL MODE: MICROPROCESSOR INTERFACE SIGNALS                              |                       |

| TABLE 13: MOTOROLA MODE: MICROPROCESSOR INTERFACE SIGNALS                           |                       |

| 5.4 INTEL MODE PROGRAMMED I/O ACCESS (ASYNCHRONOUS)                                 | 45                    |

| FIGURE 32. INTEL μP INTERFACE SIGNALS DURING PROGRAMMED I/O READ AND WRITE OPERA    | TIONS46               |

| TABLE 14: INTEL MICROPROCESSOR INTERFACE TIMING SPECIFICATIONS                      | 46                    |

| 5.5 MOTOROLA MODE PROGRAMMED I/O ACCESS (ASYNCHRONOUS)                              | 47                    |

| FIGURE 33. MOTOROLA 68K μP INTERFACE SIGNALS DURING PROGRAMMED I/O READ AND WRI     | ITE OPERATIONS48      |

| TABLE 15: MOTOROLA 68K MICROPROCESSOR INTERFACE TIMING SPECIFICATIONS               | 48                    |

| 5.6 POWERPC 403 SYNCHRONOUS MODE:                                                   | 49                    |

#### 8-CHANNEL E1 SHORT-HAUL LINE INTERFACE UNIT

| F1011PE 07    | MDC0CV Mons Turno Dean Openation                       |     |

|---------------|--------------------------------------------------------|-----|

|               | MPC86X MODE TIMING - READ OPERATION                    |     |

|               | MICROPHOCESSOR REGISTER CHANNEL DESCRIPTION            |     |

|               | INEL CONTROL REGISTERS                                 |     |

|               | MICROPROCESSOR REGISTER 0x00h BIT DESCRIPTION          |     |

|               | CABLE LENGTH SETTING                                   |     |

|               | MICROPROCESSOR REGISTER 0x01H BIT DESCRIPTION          |     |

|               | MICROPROCESSOR REGISTER 0x01H BIT DESCRIPTION          |     |

| -             | MICROPROCESSOR REGISTER 0x02H BIT DESCRIPTION          | -   |

|               | MICROPROCESSOR REGISTER 0x004 BIT DESCRIPTION          |     |

|               | MICROPROCESSOR REGISTER 0x04A BIT DESCRIPTION          |     |

|               | MICROPROCESSOR REGISTER 0x00H BIT DESCRIPTION          |     |

|               | BAL CONTROL REGISTERS                                  |     |

|               | MICROPROCESSOR REGISTER 0x80H, BIT DESCRIPTION         |     |

|               | MICROPROCESSOR REGISTER 0x81H. BIT DESCRIPTION         |     |

| _             | MICROPROCESSOR REGISTER 0x82H BIT DESCRIPTION          | -   |

|               | MICROPROCESSOR REGISTER 0x8CH BIT DESCRIPTION.         |     |

|               | MICROPROCESSOR REGISTER 0x8DH BIT DESCRIPTION          |     |

|               | MICROPROCESSOR REGISTER 0x8EH BIT DESCRIPTION          |     |

|               | MICROPROCESSOR REGISTER 0XFEH BIT DESCRIPTION          |     |

|               | MICROPROCESSOR REGISTER 0xFFH BIT DESCRIPTION          |     |

| 6.0 ELECTR    | ICAL CHARACTERISTICS                                   | 68  |

|               | ABSOLUTE MAXIMUM RATINGS                               |     |

|               | DC DIGITAL INPUT AND OUTPUT ELECTRICAL CHARACTERISTICS |     |

| TABLE 40:     | AC ELECTRICAL CHARACTERISTICS                          | 68  |

|               | POWER CONSUMPTION                                      |     |

| TABLE 42:     | E1 RECEIVER ELECTRICAL CHARACTERISTICS                 | 69  |

| TABLE 43:     | E1 Transmitter Electrical Characteristics              | 70  |

| PACKAGE DI    | IMENSIONS                                              | 71  |

| 225 B         | ALL PLASTIC BALL GRID ARRAY (BOTTOM VIEW)              | 71  |

|               | x 19.0 x 1.0mm)                                        |     |

| `             | S INFORMATION                                          |     |

|               | S                                                      |     |

| I IL VIOIOIVO | /                                                      | , _ |

## EXAR Powering Connectivity\*

#### PIN DESCRIPTION BY FUNCTION

#### RECEIVE SECTION

| SIGNAL NAME                                                                                          | BGA<br>LEAD#                                     | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------------------------------------------------------------------------------------------|--------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RXON                                                                                                 | K16                                              | ı    | Receiver On  Hardware Mode Only  This pin is used to enable the receivers for all channels. By default, the receivers are turned ON in hardware mode. To turn the receivers OFF, pull this pin "Low".  Note: Internally pulled "High" with a 50kΩ resistor.                                                                                                                                                                                                                                                                                                                                                                   |

| RLOS0<br>RLOS1<br>RLOS2<br>RLOS3<br>RLOS4<br>RLOS5<br>RLOS6<br>RLOS7                                 | C3<br>H4<br>H15<br>A16<br>V3<br>L2<br>J15<br>T15 | 0    | Receive Loss of Signal  When a receive loss of signal occurs according to ITU-T G.775, the RLOS pin will go "High" for a minimum of one RCLK cycle. RLOS will remain "High" until the loss of signal condition clears. See the Receive Loss of Signal section of this datasheet for more details.  Note: This pin can be used for redundancy applications to initiate an automatic switch to a backup card.                                                                                                                                                                                                                   |

| RCLK0<br>RCLK1<br>RCLK2<br>RCLK3<br>RCLK4<br>RCLK5<br>RCLK6<br>RCLK7                                 | B3<br>H3<br>H16<br>A17<br>U3<br>L3<br>M15<br>U16 | 0    | Receive Clock Output  RCLK is the recovered clock from the incoming data stream. If the incoming signal is absent or RTIP/RRING are in "High-Z", RCLK maintains its timing by using an internal master clock as its reference. RPOS/RNEG data can be updated on either edge of RCLK selected by RCLKE.  Note: RCLKE is a global setting that applies to all 8 channels.                                                                                                                                                                                                                                                       |

| RNEG/LCV0<br>RNEG/LCV1<br>RNEG/LCV2<br>RNEG/LCV3<br>RNEG/LCV4<br>RNEG/LCV5<br>RNEG/LCV6<br>RNEG/LCV7 | A2<br>H2<br>H18<br>B16<br>T4<br>M4<br>W16        | 0    | RNEG/LCV_OF Output In dual rail mode, this pin is the receive negative data output. In single rail mode, this pin is a Line Code Violation / Counter Overflow indicator. If LCV is selected by programming the appropriate global register and if a line code violation, a bi-polar violation, or excessive zeros occur, the LCV pin will pull "High" for a minimum of one RCLK cycle. LCV will remain "High" until there are no more violations. However, if OF (Overflow) is selected the LCV pin will pull "High" if the internal LCV counter is saturated. The LCV pin will remain "High" until the LCV counter is reset. |

| RPOS0<br>RPOS1<br>RPOS2<br>RPOS3<br>RPOS4<br>RPOS5<br>RPOS6<br>RPOS7                                 | B2<br>G2<br>D15<br>B17<br>U2<br>M3<br>L17        | 0    | RPOS/RDATA Output  Receive digital output pin. In dual rail mode, this pin is the receive positive data output. In single rail mode, this pin is the receive non-return to zero (NRZ) data output.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SIGNAL NAME | BGA<br>LEAD# | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------|--------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RTIP0       | C1           | ı    | Receive Differential Tip Input                                                                                                                                                                                                                                                                                                                                                                             |

| RTIP1       | G1           |      | RTIP is the positive differential input from the line interface. Along with the RRING                                                                                                                                                                                                                                                                                                                      |

| RTIP2       | G18          |      | signal, these pins should be coupled to a 1:1 transformer for proper operation.                                                                                                                                                                                                                                                                                                                            |

| RTIP3       | C18          |      |                                                                                                                                                                                                                                                                                                                                                                                                            |

| RTIP4       | U1           |      |                                                                                                                                                                                                                                                                                                                                                                                                            |

| RTIP5       | L1           |      |                                                                                                                                                                                                                                                                                                                                                                                                            |

| RTIP6       | L18          |      |                                                                                                                                                                                                                                                                                                                                                                                                            |

| RTIP7       | T18          |      |                                                                                                                                                                                                                                                                                                                                                                                                            |

| RRING0      | D1           | ı    | Receive Differential Ring Input                                                                                                                                                                                                                                                                                                                                                                            |

| RRING1      | F1           |      | RRING is the negative differential input from the line interface. Along with the RTIP-                                                                                                                                                                                                                                                                                                                     |

| RRING2      | F18          |      | signal, these pins should be coupled to a 1:1 transformer for proper operation.                                                                                                                                                                                                                                                                                                                            |

| RRING3      | D18          |      |                                                                                                                                                                                                                                                                                                                                                                                                            |

| RRING4      | T1           |      |                                                                                                                                                                                                                                                                                                                                                                                                            |

| RRING5      | M1           |      |                                                                                                                                                                                                                                                                                                                                                                                                            |

| RRING6      | M18          |      |                                                                                                                                                                                                                                                                                                                                                                                                            |

| RRING7      | R18          |      |                                                                                                                                                                                                                                                                                                                                                                                                            |

| RXMUTE      | T12          | I    | Receive Data Muting                                                                                                                                                                                                                                                                                                                                                                                        |

|             |              |      | Hardware Mode Only                                                                                                                                                                                                                                                                                                                                                                                         |

|             |              |      | This pin is AND-ed with each of the RLOS functions on a per channel basis. Therefore, if this pin is pulled "High" and a given channel experiences a loss of signal, then the RPOS/RNEG output pins are automatically pulled "Low" to prevent data chattering. To disable this feature, the RxMUTE pin must be pulled "Low". <b>Note:</b> This pin is internally pulled "High" with a $50k\Omega$ resistor |

|             |              |      | NOTE: This pin is internally pulled "High" with a 50KL2 resistor                                                                                                                                                                                                                                                                                                                                           |

| SIGNAL NAME      | BGA<br>LEAD# | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------|--------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RXRES1<br>RXRES0 | R10<br>V10   | ı    | Receive External Resistor Control Pins<br>Hardware mode Only<br>These pins are used in the Receive Internal Impedance mode for unique applications where an accurate resistor can be used to achieve optimal return loss. When RxRES[1:0] are used, the LIU automatically sets the internal impedance to match the line build out. For example: if $240\Omega$ is selected, the LIU chooses an internal impedance such that the parallel combination equals the impedance chosen by TERSEL[1:0].<br>"00" = No External Fixed Resistor<br>"01" = $320\Omega$<br>"10" = $280\Omega$<br>"11" = $190\Omega$                                                                                                                                                                                     |

| RCLKE/<br>μPTS1  | J16          | I    | <ul> <li>Note: These pins are internally pulled "Low" with a 50kΩ resistor. This feature is available in Host mode by programming the appropriate channel register.</li> <li>Receive Clock Edge  Hardware Mode  This pin is used to select which edge of the recovered clock is used to update data to the receiver on the RPOS/RNEG outputs. By default, data is updated on the risinge edge. To udpdate data on the falling edge, this pin must be pulled "High".  Host Mode  µPTS[2:1] pins are used to select the type of microprocessor to be used for Host communication.  "00" = 8051 Intel Asynchronous "01" = 68K Motorola Asynchronous "10" = Power PC 403 "11" = MPC8xx Power PC Synchronous</li> <li>Note: This pin is internally pulled "Low" with a 50kΩ resistor.</li> </ul> |

#### TRANSMIT SECTION

| SIGNAL NAME                                             | BGA<br>LEAD#                                     | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------------------------------------------------|--------------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TCLKE/μPTS2                                             | L15                                              | I    | Transmit Clock Edge<br><u>Hardware Mode</u> This pin is used to select which edge of the transmit clock is used to sample data on the transmitter on the TPOS/TNEG inputs. By default, data is sampled on the falling edge. To sample data on the rising edge, this pin must be pulled "High".<br><u>Host Mode</u> $\mu$ PTS[2:1] pins are used to select the type of microprocessor to be used for Host communication.  "00" = 8051 Intel Asynchronous  "01" = 68K Motorola Asynchronous  "10" = Power PC 403  "11" = MPC8xx Power PC Synchronous  Note: This pin is internally pulled "Low" with a 50kΩ resistor. |

| TTIP0 TTIP1 TTIP2 TTIP3 TTIP4 TTIP5 TTIP6 TTIP7         | E3<br>G4<br>F17<br>C16<br>R2<br>N2<br>N16<br>P16 | 0    | Transmit Differential Tip Output  TTIP is the positive differential output to the line interface. Along with the TRING signal, these pins should be coupled to a 1:2 step up transformer for proper operation.                                                                                                                                                                                                                                                                                                                                                                                                      |

| TRING0 TRING1 TRING2 TRING3 TRING4 TRING5 TRING6 TRING7 | E2<br>F3<br>F15<br>E16<br>P2<br>N4<br>R15<br>P17 | 0    | Transmit Differential Ring Output TRING is the negative differential output to the line interface. Along with the TTIP signal, these pins should be coupled to a 1:2 step up transformer for proper operation.                                                                                                                                                                                                                                                                                                                                                                                                      |

| TPOS0 TPOS1 TPOS2 TPOS3 TPOS4 TPOS5 TPOS6 TPOS7         | C5<br>A4<br>B14<br>D14<br>V4<br>U5<br>V15<br>T14 | I    | TPOS/TDATA Input Transmit digital input pin. In dual rail mode, this pin is the transmit positive data input. In single rail mode, this pin is the transmit non-return to zero (NRZ) data input.  Note: Internally pulled "Low" with a $50 \text{K}\Omega$ resistor.                                                                                                                                                                                                                                                                                                                                                |

| TNEG0 TNEG1 TNEG2 TNEG3 TNEG4 TNEG5 TNEG6 TNEG6         | C4<br>B5<br>D13<br>B15<br>U4<br>V5<br>U14<br>R14 | I    | Transmitter Negative NRZ Data Input In dual rail mode, this signal is the negative-rail input data for the transmitter. In single rail mode, this pin can be left unconnected while in Host mode. However, in Hardware mode, this pin is used to select the type of encoding/decoding for the E1 data format. Connecting this pin "Low" enables HDB3. Connecting this pin "High" selects AMI data format.  Note: Internally pulled "Low" with a 50kΩ resistor.                                                                                                                                                      |

| SIGNAL NAME                                     | BGA<br>LEAD#                                         | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------------------------------------|------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TCLK0 TCLK1 TCLK2 TCLK3 TCLK4 TCLK5 TCLK6 TCLK6 | B4<br>A3<br>A15<br>C14<br>T3<br>T5<br>V16<br>U15     | I    | Transmit Clock Input  TCLK is the input facility clock used to sample the incoming TPOS/TNEG data. If  TCLK is absent, pulled "Low", or pulled "High", the transmitter outputs at TTIP/  TRING sends an all zero signal to the line. TPOS/TNEG data can be sampled on  either edge of TCLK selected by TCLKE.  Note: TCLKE is a global setting that applies to all 8 channels. These pins are  Internally pulled "Low" with 50kΩ resistors.                                                                                                                                       |

| TAOS0 TAOS1 TAOS2 TAOS3 TAOS4 TAOS5 TAOS6 TAOS7 | D6<br>B6<br>A5<br>C6<br>T6<br>U6<br>V6<br>R6         | ı    | Transmit All Ones for Channel  Hardware Mode Only  Setting this pin "High" enables the transmission of an all ones pattern to the line from TTIP/TRING. If this pin is pulled "Low", the transmitters operate in normal throughput mode.  Note: Internally pulled "Low" with a 50kΩ resistor for all channels. This feature is available in Host mode by programming the appropriate channel register.                                                                                                                                                                            |

| TXON0 TXON1 TXON2 TXON3 TXON4 TXON5 TXON6 TXON7 | A13<br>D12<br>C12<br>B12<br>V13<br>U13<br>R12<br>R13 | I    | Transmit On/Off Input  Upon power up, the transmitters are powered off. Turning the transmitters On or Off is selected through the microprocessor interface by programming the appropriate channel register while in Host mode. However, if TxONCNTL is set "High" in the appropriate global register or if in Hardware mode, the activity of the transmitter outputs is controlled by the TxON pins.  Note: TxON is ideal for redundancy applications. See the Redundancy Applications Section of this datasheet for more details. Internally pulled "Low" with a 50KΩ resistor. |

#### PARALLEL MICROPROCESSOR INTERFACE

| SIGNAL NAME | BGA<br>LEAD<br># | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                |

|-------------|------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HW/HOST     | T10              | ı    | Mode Control Input  This pin is used to select Host mode or Hardware mode. By default, the LIU is set in Hardware mode. To use Host mode, this pin must be pulled "Low".                                                                                                                                                                                                                   |

|             |                  |      | <b>Note:</b> Internally pulled "High" with a $50k\Omega$ resistor.                                                                                                                                                                                                                                                                                                                         |

| WR_R/W/EQC0 | D7               | I    | Write Input(R/W)/Equalizer Control Signal 0  Host Mode                                                                                                                                                                                                                                                                                                                                     |

|             |                  |      | This pin is used to communicate a Read or Write operation according to the which microprocessor is chosen. See the Microprocessor Section of this datasheet for details.                                                                                                                                                                                                                   |

|             |                  |      | Hardware Mode  EQC[4:0] are used to set the Receiver Gain, Receiver Impedance and the Transmit  Line Build Out. See Table 23 for more details.                                                                                                                                                                                                                                             |

|             |                  |      | <b>Note:</b> Internally pulled "Low" with a $50k\Omega$ resistor.                                                                                                                                                                                                                                                                                                                          |

| RD_DS/EQC1  | C7               | ı    | Read Input (Data Strobe)/Equalizer Control Signal 1  Host Mode  This pin is used to communicate a Read or Write operation according to the which microprocessor is chosen. See the Microprocessor Section of this datasheet for details.  Hardware Mode                                                                                                                                    |

|             |                  |      | EQC[4:0] are used to set the Receiver Gain, Receiver Impedance and the Transmit Line Build Out. See Table 23 for more details.                                                                                                                                                                                                                                                             |

|             |                  |      | <b>NOTE:</b> Internally pulled "Low" with a $50k\Omega$ resistor.                                                                                                                                                                                                                                                                                                                          |

| ALE/EQC2    | A7               | ı    | Address Latch Input (Address Strobe)  Host Mode  This pin is used to latch the address contents into the internal registers within the LIU device. See the Microprocessor Section of this datasheet for details.  Hardware Mode  EQC[4:0] are used to set the Receiver Gain, Receiver Impedance and the Transmit                                                                           |

|             |                  |      | Line Build Out. See <b>Table 23</b> for more details. <b>Note:</b> Internally pulled "Low" with a 50kΩ resistor.                                                                                                                                                                                                                                                                           |

| CS/EQC3     | B7               | ı    | Chip Select Input - Host mode:  Host Mode  This pin is used to initiate communication with the microprocessor interface. See the Microprocessor Section of this datasheet for details.  Hardware Mode  EQC[4:0] are used to set the Receiver Gain, Receiver Impedance and the Transmit Line Build Out. See Table 23 for more details.  Note: Internally pulled "Low" with a 50kΩ resistor. |

| SIGNAL NAME                                                                                                          | BGA<br>LEAD<br>#                                     | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RDY/EQC4                                                                                                             | A6                                                   | 1/0  | Ready Output (Data Transfer Acknowledge)  Host Mode (Parallel Microprocessor)  If Pin SER_PAR is pulled "Low", this output pin from the microprocessor block is used to inform the local $\mu P$ that the Read or Write operation has been completed and is waiting for the next command. See the Microprocessor Section of this datasheet for details.  Host Mode (Serial Interface)  If Pin SER_PAR is pulled "High", this output pin from the serial interface is used to read back the regsiter contents. See the Microprocessor Section of this datasheet for details.  Hardware Mode  EQC[4:0] are used to set the Receiver Gain, Receiver Impedance and the Transmit Line Build Out. See Table 23 for more details.  Note: Internally pulled "Low" with a $50k\Omega$ resistor. |

| D[7]/Loop14<br>D[6]/Loop04<br>D[5]/Loop15<br>D[4]/Loop05<br>D[3]/Loop16<br>D[2]/Loop06<br>D[1]/Loop17<br>D[0]/Loop07 | T7<br>U7<br>V8<br>V9<br>U8<br>U9<br>R7               | I/O  | Bi-Directional Data Bust/Loopback Mode Select  Host Mode  These pins are used for the 8-bit bi-directional data bus to allow data transfer to and from the microprocessor interface.  Hardware Mode (Channels 4 through 7)  These pins are used to select the loopback mode. Each channel has two loopback pins Loop[1:0].  "00" = No Loopback "01" = Analog Local Loopback "10" = Remote Loopback "11" = Digital Loopback  Note: Internally pulled "Low" with a 50kΩ resistor.                                                                                                                                                                                                                                                                                                        |

| A[7]/Loop13<br>A[6]/Loop03<br>A[5]/Loop12<br>A[4]/Loop02<br>A[3]/Loop11<br>A[2]/Loop01<br>A[1]/Loop10<br>A[0]/Loop00 | A12<br>B11<br>C11<br>D11<br>A11<br>B10<br>A10<br>C10 | ı    | Direct Address Bus/Loopback Mode Select  Host Mode  These pins are used for the 8-bit direct address bus to allow access to the internal registers within the microprocessor interface.  Hardware Mode (Channels 0 through 3)  These pins are used to select the loopback mode. Each channel has two loopback pins Loop[1:0].  "00" = No Loopback "01" = Analog Local Loopback "10" = Remote Loopback "11" = Digital Loopback  Note: Internally pulled "Low" with a 50kΩ resistor.                                                                                                                                                                                                                                                                                                     |

| SIGNAL NAME | BGA<br>LEAD<br># | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------|------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| μPCLK/ATAOS | T13              | ı    | Synchronous Microprocessor Clock/Automatic Transmit All Ones  Host Mode  This synchronous input clock is used as the internal master clock to the microprocessor interface when configured for in a synchronous mode.  Hardware Mode  This pin is used select an all ones signal to the line interface through TTIP/TRING any time that a loss of signal occurs. This feature is avaiable in Host mode by programming the appropriate global register.  Note: Internally pulled "Low" with a 50kΩ resistor. |

| ĪNT         | L16              | 0    | Interrupt Output  Host Mode  This signal is asserted "Low" when a change in alarm status occurs. Once the status registers have been read, the interrupt pin will return "High". GIE (Global Interrupt Enable) must be set "High" in the appropriate global register to enable interrupt generation.  Note: This pin is an open-drain output that requires an external 10KΩ pull-up resistor.                                                                                                               |

#### JITTER ATTENUATOR

| SIGNAL<br>NAME   | BGA<br>LEAD# | Түре |       | DESCRIPTION |              |                               |                               |                |                  |

|------------------|--------------|------|-------|-------------|--------------|-------------------------------|-------------------------------|----------------|------------------|

| JASEL0<br>JASEL1 | A14<br>B13   | I    | JASEL |             | are used to  | ns Hardware<br>place the jitt | • Mode<br>er attenuator in tl | he transmit pa | ath, the receive |

|                  |              |      |       | JASEL1      | JASELO       | JA Path                       | JA BW Hz<br>E1                | FIFO Size      |                  |

|                  |              |      |       | 0           | 0            | Disabled                      |                               |                |                  |

|                  |              |      |       | 0           | 1            | Transmit                      | 10                            | 32/32          |                  |

|                  |              |      |       | 1           | 0            | Receive                       | 10                            | 32/32          |                  |

|                  |              |      |       | 1           | 1            | Receive                       | 1.5                           | 64/64          |                  |

|                  |              |      | Note: | These pi    | ns are inter | nally pulled "                | 'Low" with $50$ k $\Omega$ r  | resistors.     |                  |

#### **CLOCK SYNTHESIZER**

| SIGNAL NAME | BGA<br>LEAD# | Түре | DESCRIPTION                                                                                                                                                                                                    |

|-------------|--------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MCLKOUT     | H1           | 0    | Synthesized Master Clock Output  This signal is the output of the Master Clock Synthesizer PLL which is at E1 rate.                                                                                            |

| MCLKE1      | J1           | ı    | E1 Master Clock Input A 2.048MHz clock for with an accuracy of better than ±50ppm and a duty cycle of 40% to 60% can be provided at this pin.  Note: This pin is internally pulled "Low" with a 50kΩ resistor. |

#### ALARM FUNCTIONS/REDUNDANCY SUPPORT

| SIGNAL NAME                                                  | BGA<br>LEAD#                                     | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------------------------------------------|--------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GAUGE                                                        | J18                                              | I    | Twisted Pair Cable Wire Gauge Select  Hardware Mode Only  This pin is used to match the frequency characteristics according to the gauge of wire used in Telecom circuits. By default, the LIU is matched to 22 gauge or 24 gauge wire. To select 26 gauge, this pin must be pulled "High".  Note: Internally pulled "Low" with a 50kΩ resistor.                                                                                                                                                                                                                                                                                                                                                                                                               |

| DMO0<br>DMO1<br>DMO2<br>DMO3<br>DMO4<br>DMO5<br>DMO6<br>DMO7 | D5<br>D4<br>C15<br>C13<br>R5<br>P4<br>U17<br>V14 | 0    | Digital Monitor Output  When no transmit output pulse is detected for more than 128 TCLK cycles within the transmit output buffer, the DMO pin will go "High" for a minimum of one TCLK cycle. DMO will remain "High" until the transmitter sends a valid pulse.  Note: This pin can be used for redundancy applications to initiate an automatic switch to a backup card.                                                                                                                                                                                                                                                                                                                                                                                     |

| RESET                                                        | T8                                               | I    | Hardware Reset Input  Active low signal. When this pin is pulled "Low" for more than 10μS, the internal registers are set to their default state. See the register description for the default values.  Note: Internally pulled "High" with a 50ΚΩ resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SR/DR                                                        | K4                                               | I    | Single-Rail/Dual-Rail Data Format  Hardware Mode Only This pin is used to control the data format on the facility side of the LIU to interface to a Framer or Mapper/ASIC device. By default, dual rail mode is selected which relies upon the Framer to handle the encoding/decoding functions. To select single rail mode, this pin must be pulled "High". If single rail mode is selected, the LIU can encode/decode AMI or HDB3 data formats.  Note: Internally pulled "Low" with a 50kΩ resistor.                                                                                                                                                                                                                                                         |

| RXTSEL                                                       | U11                                              | I    | Receiver Termination Select  Hardware Mode  This pin is used to select between the internal and external impedance modes for the receive path. By default, the receivers are configured for external impedance mode, which is ideal for redundancy applications without relays. To select internal impedance, this pin must be pulled "Hlgh".  Host Mode  Internal/External impedance can be selected by programming the appropriate channel registers. However, to assist in redundancy applications, this pin can be used for a hard switch if the RxTCNTL bit is set "High" in the appropriate global register. If RxTCNTL is set "High", the individual RxTSEL register bits are ignored.  Note: This pin is internally pulled "Low" with a 50kΩ resistor. |

| TXTSEL                                                       | V11                                              | I    | Transmitter Termination Select  Hardware Mode  This pin is used to select between the internal and external impedance modes for the transmit path. By default, the receivers are configured for external impedance mode, which is ideal for redundancy applications without relays. To select internal impedance, this pin must be pulled "Hgh".  Note: This pin is internally pulled "Low".                                                                                                                                                                                                                                                                                                                                                                   |

#### XRT83VSH28

# EXAR Powering Connectivity\* REV. 2.0.0

#### 8-CHANNEL E1 SHORT-HAUL LINE INTERFACE UNIT

| SIGNAL NAME | BGA<br>LEAD# | Түре | DESCRIPTION                                                                                                                                                                  |  |

|-------------|--------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| TERSEL      | R11          | I    | Termination Impedance Select                                                                                                                                                 |  |

| TEST        | U12          | I    | Factory Test Mode For normal operation, the TEST pin should be tied to ground.<br>Note: Internally pulled "Low" with a $50k\Omega$ resistor.                                 |  |

| ĪCT         | V12          | ı    | In Circuit Testing When this pin is tied "Low", all output pins are forced to "High" impedance for in circuit testing.  Note: Internally pulled "High" with a 50KΩ resistor. |  |

#### SERIAL MICROPROCESSOR INTERFACE

| SIGNAL NAME         | BGA<br>LEAD# | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                     |

|---------------------|--------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SER_PAR             | P18          | I    | Serial/Parallel Select Input (Host Mode Only) This pin is used in the Host mode to select between the parallel microprocessor or serial interface. By default, the Host mode operates in the parallel microprocessor mode. To configure the device for a serial interface, this pin must be pulled "Hlgh".  Note: Internally pulled "Low" with a 50kΩ resistor. |

| SCLK                | T13          | I    | Serial Clock Input (Host Mode Only)  If Pin SER_PAR is pulled "High", this input pin is used as the timing reference for the serial microprocessor interface. See the Microprocessor Section of this datasheet for details.                                                                                                                                     |

| SDI                 | C10          | ı    | Serial Data Input (Host Mode Only)  If Pin SER_PAR is pulled "High", this input pin from the serial interface is used to input the serial data for Read and Write operations. See the Microprocessor Section of this datasheet for details.                                                                                                                     |

| SDO                 | R7           | 0    | Serial Data Output (Host Mode Only)  If Pin SER_PAR is pulled "High", this output pin from the serial interface is used to read back the regsiter contents. See the Microprocessor Section of this datasheet for details.                                                                                                                                       |

| JTAGtip<br>JTAGring | E18<br>B18   |      | Analog JTAG Positive Pin Analog JTAG Negative Pin                                                                                                                                                                                                                                                                                                               |

| TDO                 | B1           |      | Test Data Out This pin is used as the output data pin for the boundary scan chain.                                                                                                                                                                                                                                                                              |

| TDI                 | R1           |      | Test Data In  This pin is used as the input data pin for the boundary scan chain.                                                                                                                                                                                                                                                                               |

| TCK                 | N1           |      | Test Clock Input This pin is used as the input clock source for the boundary scan chain.                                                                                                                                                                                                                                                                        |

| TMS                 | E1           |      | Test Mode Select This pin is used as the input mode select for the boundary scan chain.                                                                                                                                                                                                                                                                         |