Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

SEPTEMBER 2006 REV. 1.0.1

# **GENERAL DESCRIPTION**

The XRT83VSH314 is a fully integrated 14-channel short-haul line interface unit (LIU) that operates from a 1.8V Inner Core and 3.3V I/O power supplies. Using internal termination, the LIU provides one bill of materials to operate in T1, E1, or J1 mode independently on a per channel basis with minimum external components. The LIU features are programmed through a standard microprocessor interface. EXAR's LIU has patented high impedance circuits that allow the transmitter outputs and receiver inputs to be high impedance when experiencing a power failure or when the LIU is powered off. Key design features within the LIU optimize 1:1 or 1+1 redundancy and non-intrusive monitoring applications to ensure reliability without using relays.

The on-chip clock synthesizer generates T1/E1/J1 clock rates from a selectable external clock frequency and has five output clock references that can be used

for external timing (8kHz, 1.544Mhz, 2.048Mhz, nxT1/J1, nxE1).

Additional features include RLOS, a 16-bit LCV counter for each channel, AIS, QRSS/PRBS generation/detection, TAOS, DMO, and diagnostic loopback modes.

## **APPLICATIONS**

- T1 Digital Cross Connects (DSX-1)

- ISDN Primary Rate Interface

- CSU/DSU E1/T1/J1 Interface

- T1/E1/J1 LAN/WAN Routers

- Public Switching Systems and PBX Interfaces

- T1/E1/J1 Multiplexer and Channel Banks

- Integrated Multi-Service Access Platforms (IMAPs)

- Integrated Access Devices (IADs)

- Inverse Multiplexing for ATM (IMA)

- Wireless Base Stations

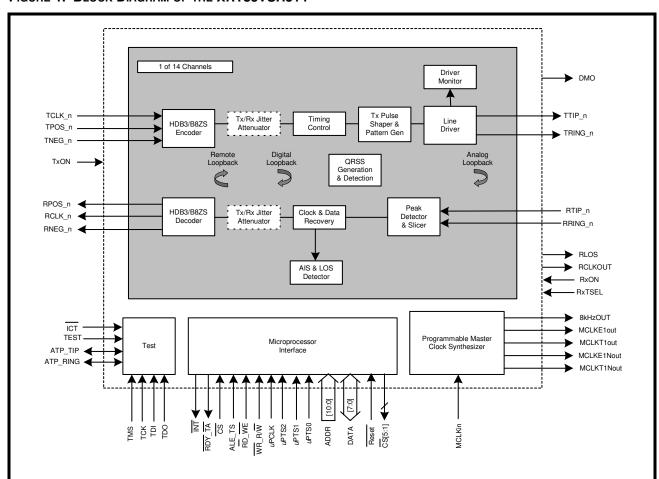

FIGURE 1. BLOCK DIAGRAM OF THE XRT83VSH314

# **XRT83VSH314**

### 14-CHANNEL T1/E1/J1 SHORT-HAUL LINE INTERFACE UNIT

### **FEATURES**

- Fully integrated 14-Channel short haul transceivers for T1/J1 (1.544MHz) and E1 (2.048MHz) applications

- T1/E1/J1 short haul and clock rate are per port selectable through software without changing components

- Internal Impedance matching on both receive and transmit for 75Ω (E1), 100Ω (T1), 110Ω (J1), and 120Ω (E1) applications are per port selectable through software without changing components

- Power down on a per channel basis with independent receive and transmit selection

- Five pre-programmed transmit pulse settings for T1 short haul applications per channel

- User programable Arbitrary Pulse mode

- On-Chip transmit short-circuit protection and limiting protects line drivers from damage on a per channel basis

- Selectable Crystal-Less digital jitter attenuators (JA) with 32-Bit or 64-Bit FIFO for the receive or transmit path

- Driver failure monitor output (DMO) alerts of possible system or external component problems

- Transmit outputs and receive inputs may be "High" impedance for protection or redundancy applications on a per channel basis

- Support for automatic protection switching

- 1:1 and 1+1 protection without relays

- Receive monitor mode handles 0 to 6dB resistive attenuation (flat loss) along with 0 to 6dB cable loss for both T1 and E1

- Loss of signal (RLOS) according to ITU-T G.775/ETS300233 (E1) and ANSI T1.403 (T1/J1)

- Programmable data stream muting upon RLOS detection

- On-Chip HDB3/B8ZS encoder/decoder with an internal 16-bit LCV counter for each channel

- On-Chip digital clock recovery circuit for high input jitter tolerance

- QRSS/PRBS pattern generator and detection for testing and monitoring

- Error and bipolar violation insertion and detection

- Transmit all ones (TAOS) Generators and Detectors

- Supports local analog, remote, digital, and dual loopback modes

- 1.8V Digital Core

- 3.3V I/O and Analog Core

- 304-Pin BGA package

- -40°C to +85°C Temperature Range

- Supports gapped clocks for mapper/multiplexer applications

## PRODUCT ORDERING INFORMATION

| PRODUCT NUMBER | PACKAGE TYPE  | OPERATING TEMPERATURE RANGE |

|----------------|---------------|-----------------------------|

| XRT83VSH314IB  | 304 Lead PBGA | -40°C to +85°C              |

# PIN OUT OF THE XRT83VSH314

| 23          | 22       | 21         | 20         | 19      | 18       | 17       | 16        | 15        | 14      | 13       | 12        | 11      | 10      | 9         | 8         | 7          | 6      | 5          | 4         | 3         | 2          | 1       | П  |

|-------------|----------|------------|------------|---------|----------|----------|-----------|-----------|---------|----------|-----------|---------|---------|-----------|-----------|------------|--------|------------|-----------|-----------|------------|---------|----|

| A[10]       | CS       | CS4        | WR_RW      | TCLK_8  | TPOS_10  | TPOS_7   | DGND_DRV  | RVDD_7    | RTIP_7  | RRING_7  | RGND_7    | RGND_6  | RRING_6 | RTIP_6    | RVDD_6    | MCLKOUT_T1 | MCLKIN | MCLKOUT_E1 | MCLKE1xN  | TCLK_5    | ĪCT        | TDI     | Α  |

| NC          | RESET    | CS1        | CS5        | TPOS_8  | TNEG_9   | TNEG_10  | TCLK_7    | VDDPLL_21 | RCLK_7  | TVDD_7   | TRING_7   | TRING_6 | TVDD_6  | RCLK_6    | MCLKT1xN  | TPOS_6     | TCLK_3 | TCLK_4     | TPOS_4    | ĪNT       | DGND_DRV   | тск     | В  |

| RGND_8      | A[8]     | DVDD_DRV   | CS3        | ALE_AS  | TNEG_8   | TCLK_9   | TNEG_7    | VDDPLL_22 | RNEG_7  | TTIP_7   | DGND_6_7  | TTIP_6  | RNEG_6  | GNDPLL_22 | GNDPLL_21 | TNEG_6     | TNEG_3 | TNEG_4     | TPOS_5    | DVD_PRE   | TRING_5    | RGND_5  | С  |

| RRING_8     | TRING_8  | ATP_TIP    | DVD_PRE    | CS2     | RD_WE    | TPOS_9   | TCLK_10   | DGND_PRE  | RPOS_7  | TGND_7   | DVDD_6_7  | TGND_6  | RPOS_6  | NC        | EIGHT_KHZ | TCLK_6     | TPOS_3 | TNEG_5     | TEST      | TDO       | TVDD_5     | RRING_5 | D  |

| RTIP_8      | RVDD_8   | TVDD_8     | A[9]       |         |          |          |           |           |         |          |           |         |         |           |           |            |        |            | TMS       | TTIP_5    | RVDD_5     | RTIP_5  | E  |

| RVDD_9      | RCLK_8   | TTIP_8     | TGND_8     |         |          |          |           |           |         |          |           |         |         |           |           |            |        |            | TGND_5    | RNEG_5    | RCLK_5     | RVDD_4  | F  |

| RTIP_9      | RCLK_9   | RNEG_8     | RPOS_8     |         |          |          |           |           |         |          |           |         |         |           |           |            |        |            | RPOS_5    | RNEG_4    | RCLK_4     | RTIP_4  | G  |

| RRING_9     | TVDD_9   | RNEG_9     | RPOS_9     |         |          |          |           |           |         |          |           |         |         |           |           |            |        |            | RPOS_4    | TTIP_4    | TRING_4    | RRING_4 | Н  |

| RGND_9      | TRING_9  | TTIP_9     | TGND_9     |         |          |          |           |           |         |          |           |         |         |           |           |            |        |            | TGND_4    | TVDD_4    | DVDD_3_4_5 | RGND_4  | J  |

| DVDD_8_9_10 | NC       | ATP_RING   | SENSE      |         |          |          |           |           |         |          |           |         |         |           |           |            |        |            | AVDD_BIAS | DVDD_DRV  | CMPOUT     | RCLKOUT | Κ  |

| DGND_8_9_10 | NC       | NC         | DGND_PRE   |         |          |          |           |           |         |          |           |         |         |           |           |            |        |            | NC        | AGND_BIAS | DGND_3_4_5 | PhDIN   | L  |

| RGND_10     | TRING_10 | TTIP_10    | TGND_10    |         |          |          |           |           |         | В        | ottom     | View    | '       |           |           |            |        |            | TGND_3    | TTIP_3    | TRING_3    | RGND_3  | М  |

| RRING_10    | TVDD_10  | RNEG_10    | RPOS_10    |         |          |          |           |           |         |          |           |         |         |           |           |            |        |            | RPOS_3    | RNEG_3    | TVDD_3     | RRING_3 | N  |

| RTIP_10     | RCLK_10  | RNEG_11    | RPOS_11    |         |          |          |           |           |         |          |           |         |         |           |           |            |        |            | RPOS_2    | RNEG_2    | RCLK_3     | RTIP_3  | Р  |

| RVDD_10     | RCLK_11  | TTIP_11    | TGND_11    |         |          |          |           |           |         |          |           |         |         |           |           |            |        |            | TGND_2    | TTIP_2    | RCLK_2     | RVDD_3  | R  |

| RTIP_11     | RVDD_11  | TVDD_11    | TRING_11   |         |          |          |           |           |         |          |           |         |         |           |           |            |        |            | DGND_1_2  | TVDD_2    | RVDD_2     | RTIP_2  | Т  |

| RRING_11    | DVDD_DRV | DVDD_11_12 | DGND_11_12 |         |          |          |           |           |         |          |           |         |         |           |           |            |        |            | TVDD_1    | DGND_DRV  | TRING_2    | RRING_2 | U  |

| RGND_11     | TRING_12 | TVDD_12    | TGND_12    |         |          |          |           |           |         |          |           |         |         |           |           |            |        |            | TGND_1    | TRING_1   | DVDD_1_2   | RGND_2  | ٧  |

| RRING_12    | RGND_12  | TTIP_12    | RPOS_12    |         | <b>r</b> | <b>r</b> |           |           |         | 1        | •         |         | ,       |           |           |            |        |            | RPOS_1    | TTIP_1    | RGND_1     | RRING_1 | W  |

| RTIP_12     | RCLK_12  | RNEG_12    | DVD_PRE    | A[1]    | A[7]     | TCLK_12  | TCLK_13   | RXTSEL    | RPOS_13 | TGND_13  | DGND_13_0 | TGND_0  | RPOS_0  | GNDPLL_12 | TPOS_0    | TNEG_1     | D[3]   | DVD_PRE    | DMO       | RNEG_1    | RVDD_1     | RTIP_1  | Υ  |

| RVDD_12     | NC       | UPTS0      | A[2]       | A[6]    | TPOS_12  | TNEG_11  | DVDD_DRV  | DVDD_UP   | RNEG_13 | TTIP_13  | DVDD_13_0 | TTIP_0  | RNEG_0  | RCLK_0    | DGND_DRV  | TNEG_2     | TPOS_1 | D[4]       | D[7]      | RDY_TA    | RCLK_1     | NC      | AA |

| DGND_DRV    | UPTS1    | A[3]       | A[5]       | RXON    | TPOS_11  | TPOS_13  | VDDPLL_12 | DGND_UP   | RCLK_13 | TVDD_13  | TRING_13  | TRING_0 | TVDD_0  | RVDD_0    | DGND_PRE  | TNEG_0     | TPOS_2 | D[0]       | D[2]      | D[6]      | UPCLK      | RLOS    | AB |

| UPTS2       | A[0]     | A[4]       | TxON       | TNEG_12 | TCLK_11  | TNEG_13  | VDDPLL_11 | RVDD_13   | RTIP_13 | RRING_13 | RGND_13   | RGND_0  | RRING_0 | RTIP_0    | GNDPLL_11 | TCLK_0     | TCLK_2 | TCLK_1     | D[1]      | D[5]      | DVD_DRV    | NC      | AC |

# **TABLE OF CONTENTS**

| GENERAL DESCRIPTION                                                                   | 1  |

|---------------------------------------------------------------------------------------|----|

| APPLICATIONS                                                                          |    |

| FIGURE 1. BLOCK DIAGRAM OF THE XRT83VSH314                                            |    |

| FEATURES                                                                              |    |

| PRODUCT ORDERING INFORMATION                                                          | 2  |

| PIN OUT OF THE XRT83VSH314                                                            | 3  |

| TABLE OF CONTENTS                                                                     |    |

| 1.0 PIN DESCRIPTIONS                                                                  |    |

|                                                                                       |    |

| MICROPROCESSOR                                                                        |    |

| RECEIVER SECTION                                                                      |    |

| TRANSMITTER SECTION                                                                   |    |

| CONTROL FUNCTION                                                                      |    |

| CLOCK SECTION                                                                         |    |

| JTAG Section                                                                          |    |

| Power and Ground                                                                      |    |

| No Connects                                                                           |    |

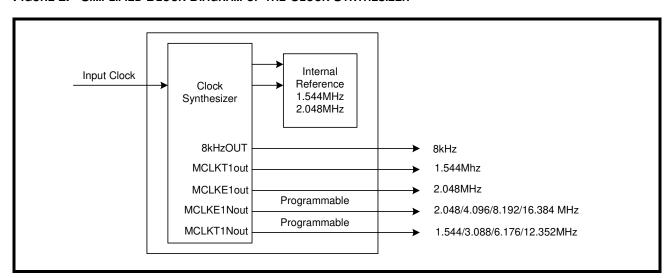

| 2.0 CLOCK SYNTHESIZER                                                                 |    |

| TABLE 1: INPUT CLOCK SOURCE SELECT                                                    |    |

| FIGURE 2. SIMPLIFIED BLOCK DIAGRAM OF THE CLOCK SYNTHESIZER                           |    |

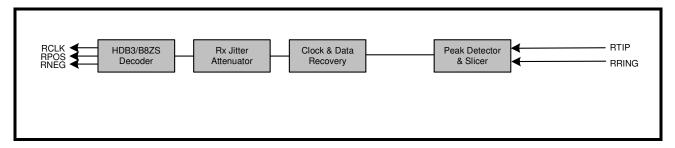

| 3.0 RECEIVE PATH LINE INTERFACE                                                       |    |

| FIGURE 3. SIMPLIFIED BLOCK DIAGRAM OF THE RECEIVE PATH                                |    |

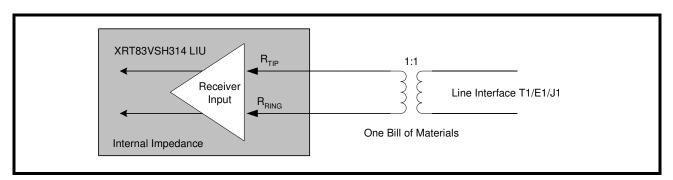

| 3.1 LINE TERMINATION (RTIP/RRING)                                                     |    |

| 3.1.1 INTERNAL TERMINATION                                                            |    |

| FIGURE 4. TYPICAL CONNECTION DIAGRAM USING INTERNAL TERMINATION                       |    |

| TABLE 3: RECEIVE TERMINATIONS                                                         |    |

| 3.2 CLOCK AND DATA RECOVERY                                                           |    |

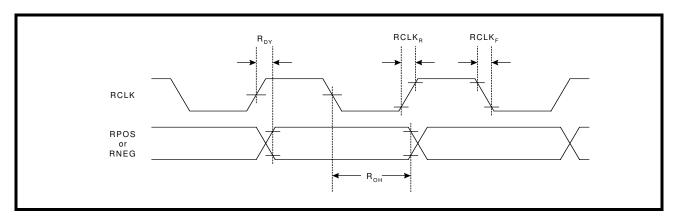

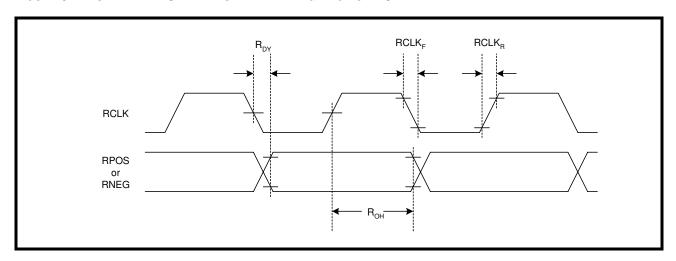

| FIGURE 5. RECEIVE DATA UPDATED ON THE RISING EDGE OF RCLK                             |    |

| FIGURE 6. RECEIVE DATA UPDATED ON THE FALLING EDGE OF RCLK                            |    |

| TABLE 4: TIMING SPECIFICATIONS FOR RCLK/RPOS/RNEG                                     |    |

| 3.2.1 RECEIVE SENSITIVITY                                                             |    |

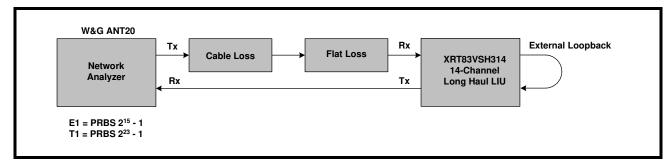

| FIGURE 7. TEST CONFIGURATION FOR MEASURING RECEIVE SENSITIVITY                        |    |

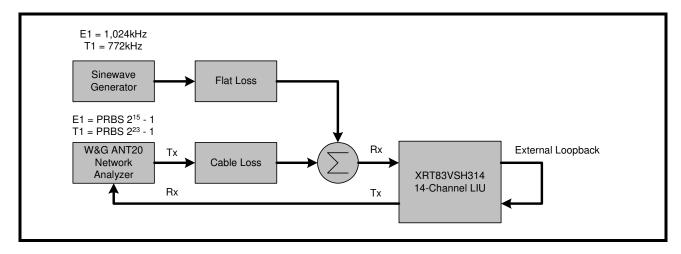

| FIGURE 8. TEST CONFIGURATION FOR MEASURING INTERFERENCE MARGIN                        |    |

| 3.2.3 GENERAL ALARM DETECTION AND INTERRUPT GENERATION                                |    |

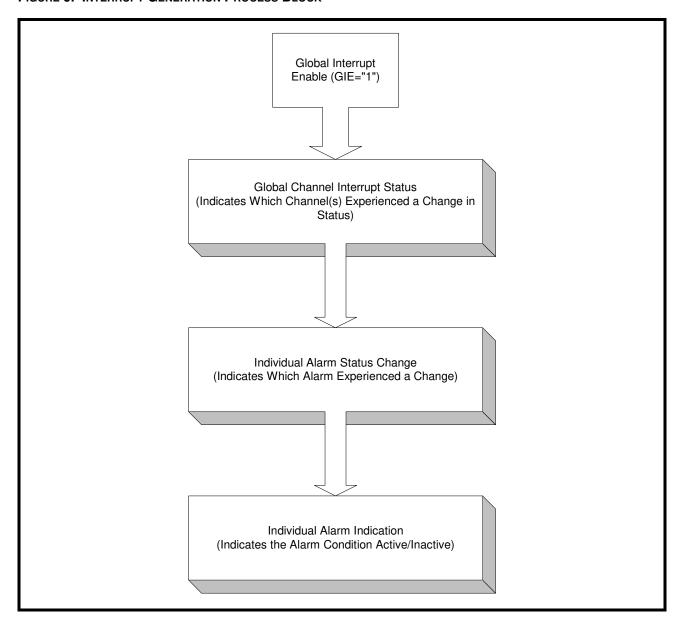

| FIGURE 9. INTERRUPT GENERATION PROCESS BLOCK                                          |    |

| 3.2.4 FLSD (FIFO LIMIT STATUS DETECTION)                                              | 22 |

| 3.3 JITTER ATTENUATOR                                                                 |    |

| 3.4 HDB3/B8ZS DECODER                                                                 |    |

| FIGURE 10. SINGLE RAIL MODE WITH A FIXED REPEATING "0011" PATTERN                     |    |

| FIGURE 11. DUAL RAIL MODE WITH A FIXED REPEATING "0011" PATTERN                       |    |

| 3.5 RXMUTE (RECEIVER LOS WITH DATA MUTING)                                            |    |

| 4.0 TRANSMIT PATH LINE INTERFACE                                                      |    |

| Figure 13. Simplified Block Diagram of the Transmit Path                              | _  |

| 4.1 TCLK/TPOS/TNEG DIGITAL INPUTS                                                     |    |

| FIGURE 14. TRANSMIT DATA SAMPLED ON FALLING EDGE OF TCLK                              |    |

| FIGURE 15. TRANSMIT DATA SAMPLED ON RISING EDGE OF TCLK                               |    |

| TABLE 5: TIMING SPECIFICATIONS FOR TCLK/TPOS/TNEG                                     |    |

| 4.2 HDB3/B8ZS ENCODER                                                                 |    |

| TABLE 6: EXAMPLES OF HDB3 ENCODING                                                    |    |

| TABLE 7: EXAMPLES OF B8ZS ENCODING                                                    |    |

| 4.3 JITTER ATTENUATOR  Table 8: Maximum Gap Width for Multiplexer/Mapper Applications |    |

| 1 ABLE 8: MAXIMUM GAP WIDTH FOR MULTIPLEXER/MAPPER APPLICATIONS                       |    |

| FIGURE 16. TAOS (TRANSMIT ALL ONES)                                                   |    |

| 4.5 TRANSMIT DIAGNOSTIC FEATURES                                                      |    |

| 4.5.1 ATAOS (AUTOMATIC TRANSMIT ALL ONES)                                             |    |

| FIGURE 17. SIMPLIFIED BLOCK DIAGRAM OF THE ATAOS FUNCTION                             |    |

REV. 1.0.1

# 14-CHANNEL T1/E1/J1 SHORT-HAUL LINE INTERFACE UNIT

|     | 4.5.2 QRSS/PRBS GENERATION                                                                      |      |

|-----|-------------------------------------------------------------------------------------------------|------|

|     | TABLE 9: RANDOM BIT SEQUENCE POLYNOMIALS                                                        |      |

|     | 4.6 TRANSMIT PULSE SHAPER AND FILTER                                                            |      |

|     | 4.6.1 T1 SHORT HAUL LINE BUILD OUT (LBO)                                                        |      |

|     | TABLE 10: SHORT HAUL LINE BUILD OUT                                                             |      |

|     | FIGURE 18. ARBITRARY PULSE SEGMENT ASSIGNMENT                                                   |      |

|     | 4.6.3 SETTING REGISTERS TO SELECT AN ARIBTRARY PULSE                                            |      |

|     | TABLE 11: TYPICAL ROM VALUES                                                                    |      |

|     | 4.7 DMO (DIGITAL MONITOR OUTPUT)                                                                |      |

|     | 4.8 LINE TERMINATION (TTIP/TRING)                                                               |      |

|     | FIGURE 19. TYPICAL CONNECTION DIAGRAM USING INTERNAL TERMINATION                                |      |

| 5.0 | T1/E1 APPLICATIONS                                                                              |      |

|     | 5.1 LOOPBACK DIAGNOSTICS                                                                        |      |

|     | 5.1.1 LOCAL ANALOG LOOPBACK                                                                     |      |

|     | FIGURE 20. SIMPLIFIED BLOCK DIAGRAM OF LOCAL ANALOG LOOPBACK                                    |      |

|     | 5.1.2 REMOTE LOOPBACK                                                                           |      |

|     | 5.1.3 DIGITAL LOOPBACK                                                                          |      |

|     | FIGURE 22. SIMPLIFIED BLOCK DIAGRAM OF DIGITAL LOOPBACK                                         |      |

|     | 5.1.4 DUAL LOOPBACK                                                                             | 32   |

|     | FIGURE 23. SIMPLIFIED BLOCK DIAGRAM OF DUAL LOOPBACK                                            |      |

|     | 5.2 84-CHANNEL T1/E1 MULTIPLEXER/MAPPER APPLICATIONS                                            |      |

|     | FIGURE 24. SIMPLIFIED BLOCK DIAGRAM OF AN 84-CHANNEL APPLICATION                                |      |

|     | TABLE 12: CHIP SELECT ASSIGNMENTS                                                               |      |

|     | 5.3 LINE CARD REDUNDANCY                                                                        |      |

|     | 5.3.1 1:1 AND 1+1 REDUNDANCY WITHOUT RELAYS5.3.2 TRANSMIT INTERFACE WITH 1:1 AND 1+1 REDUNDANCY |      |

|     | FIGURE 25. SIMPLIFIED BLOCK DIAGRAM OF THE TRANSMIT INTERFACE FOR 1:1 AND 1+1 REDUNDANCY        |      |

|     | 5.3.3 RECEIVE INTERFACE WITH 1:1 AND 1+1 REDUNDANCY                                             |      |

|     | FIGURE 26. SIMPLIFIED BLOCK DIAGRAM OF THE RECEIVE INTERFACE FOR 1:1 AND 1+1 REDUNDANCY         |      |

|     | 5.3.4 N+1 REDUNDANCY USING EXTERNAL RELAYS                                                      |      |

|     | 5.3.5 TRANSMIT INTERFACE WITH N+1 REDUNDANCY                                                    |      |

|     | FIGURE 27. SIMPLIFIED BLOCK DIAGRAM OF THE TRANSMIT INTERFACE FOR N+1 REDUNDANCY                |      |

|     | 5.3.6 RECEIVE INTERFACE WITH N+1 REDUNDANCY                                                     |      |

|     | 5.4 POWER FAILURE PROTECTION                                                                    |      |

|     | 5.5 OVERVOLTAGE AND OVERCURRENT PROTECTION                                                      |      |

|     | 5.6 NON-INTRUSIVE MONITORING                                                                    |      |

|     | FIGURE 29. SIMPLIFIED BLOCK DIAGRAM OF A NON-INTRUSIVE MONITORING APPLICATION                   |      |

|     | 5.7 ANALOG BOARD CONTINUITY CHECK                                                               | . 39 |

|     | FIGURE 30. ATP TESTING BLOCK DIAGRAM                                                            |      |

|     | FIGURE 31. TIMING DIAGRAM FOR ATP TESTING                                                       |      |

|     | 5.7.1 TRANSMITTER TTIP AND TRING TESTING                                                        |      |

| 6.0 | 5.7.2 RECEIVER RTIP AND RRING  MICROPROCESSOR INTERFACE BLOCK                                   |      |

| J.U | TABLE 13: SELECTING THE MICROPROCESSOR INTERFACE MODE                                           |      |

|     | FIGURE 32. SIMPLIFIED BLOCK DIAGRAM OF THE MICROPROCESSOR INTERFACE BLOCK                       |      |

|     | 6.1 THE MICROPROCESSOR INTERFACE BLOCK SIGNALS                                                  |      |

|     | TABLE 14: XRT84SH314S MICROPROCESSOR INTERFACE SIGNALS COMMON TO BOTH INTEL AND MOTOROLA MODES  |      |

|     | TABLE 15: INTEL MODE: MICROPROCESSOR INTERFACE SIGNALS                                          |      |

|     | TABLE 16: MOTOROLA MODE: MICROPROCESSOR INTERFACE SIGNALS                                       |      |

|     | 6.2 INTEL MODE PROGRAMMED I/O ACCESS (ASYNCHRONOUS)                                             |      |

|     | FIGURE 33. INTEL μP INTERFACE SIGNALS DURING PROGRAMMED I/O READ AND WRITE OPERATIONS           |      |

|     | TABLE 17: INTEL MICROPROCESSOR INTERFACE TIMING SPECIFICATIONS                                  |      |

|     | 6.3 MPC86X MODE PROGRAMMED I/O ACCESS (SYNCHRONOUS)                                             |      |

|     | TABLE 18: MOTOROLA MPC86X MICROPROCESSOR INTERFACE TIMING SPECIFICATIONS                        |      |

|     | FIGURE 35. MOTOROLA 68K μP INTERFACE SIGNALS DURING PROGRAMMED I/O READ AND WRITE OPERATIONS    |      |

|     | TABLE 19: MOTOROLA 68K MICROPROCESSOR INTERFACE TIMING SPECIFICATIONS                           |      |

| 7.0 | REGISTER DESCRIPTIONS                                                                           | 49   |

|     | Table 20: Microprocessor Register Address (ADDR[7:0])                                           | 49   |

|     | TABLE 21: MICROPROCESSOR REGISTER CHANNEL DESCRIPTION                                           |      |

|     | TABLE 22: MICROPROCESSOR REGISTER GLOBAL DESCRIPTION                                            | 50   |

# **XRT83VSH314**

### 14-C

| HANNEL T1/E1/J1 SHORT-HAUL LINE INTERFACE UNIT          | Experience Our Connectivity REV. 1.0.1 |

|---------------------------------------------------------|----------------------------------------|

| TABLE 23: MICROPROCESSOR REGISTER 0x00h BIT DESCRIPTION | 51                                     |

| TABLE 24: CABLE LENGTH SETTINGS                         | 52                                     |

| TABLE 25: MICROPROCESSOR REGISTER 0x01H BIT DESCRIPTION | 53                                     |

| TABLE 26: MICROPROCESSOR REGISTER 0x02H BIT DESCRIPTION | 54                                     |

| TABLE 27: MICROPROCESSOR REGISTER 0x03H BIT DESCRIPTION | 55                                     |

| TABLE 28: MICROPROCESSOR REGISTER 0x04H BIT DESCRIPTION | 56                                     |

| T 00 M B 0.05: B B                                      |                                        |

# 1.0 PIN DESCRIPTIONS

# **MICROPROCESSOR**

| NAME   | Pin | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                           |

|--------|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ĊS     | A22 | I    | Chip Select Input Active low signal. This signal enables the microprocessor interface by pulling chip select "Low". The microprocessor interface is disabled when the chip select signal returns "High". Note: Internally pulled "High" with a 50k $\Omega$ resistor.                                                                                                                                 |

| ALE_TS | C19 | I    | Address Latch Enable Input (Transfer Start) See the Microprocessor section of this datasheet for a description.  Note: Internally pulled "Low" with a 50k $\Omega$ resistor.                                                                                                                                                                                                                          |

| WR_R/W | A20 | I    | Write Strobe Input (Read/Write) See the Microprocessor section of this datasheet for a description.  Note: Internally pulled "Low" with a 50k $\Omega$ resistor.                                                                                                                                                                                                                                      |

| RD_WE  | D18 | I    | Read Strobe Input (Write Enable) See the Microprocessor section of this datasheet for a description.  Note: Internally pulled "Low" with a 50k $\Omega$ resistor.                                                                                                                                                                                                                                     |

| RDY_TA | AA3 | 0    | Ready Output (Transfer Acknowledge) See the Microprocessor section of this datasheet for a description.                                                                                                                                                                                                                                                                                               |

| ĪNT    | В3  | 0    | Interrupt Output  Active low signal. This signal is asserted "Low" when a change in alarm status occurs. Once the status registers have been read, the interrupt pin will return "High". GIE (Global Interrupt Enable) must be set "High" in the appropriate global register to enable interrupt generation.  Note: This pin is an open-drain output that requires an external 10KΩ pull-up resistor. |

| μPCLK  | AB2 | I    | Micro Processor Clock Input In a synchronous microprocessor interface, μPCLK is used as the internal timing reference for programming the LIU. Note: Internally pulled "Low" with a 50k $\Omega$ resistor.                                                                                                                                                                                            |

# **MICROPROCESSOR**

| NAME                                                               | Pin                                                                             | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------------------------------------------|---------------------------------------------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADDR10 ADDR9 ADDR8 ADDR7 ADDR6 ADDR5 ADDR4 ADDR3 ADDR2 ADDR1 ADDR0 | A23<br>E20<br>C22<br>Y18<br>AA19<br>AB20<br>AC21<br>AB21<br>AA20<br>Y19<br>AC22 |      | Address Bus Input  ADDR[10:8] is used as a chip select decoder. The LIU has 5 chip select output pins for enabling up to 5 additional devices for accessing internal registers. The LIU has the option to select itself (master device), up to 5 additional devices, or all 6 devices simultaneously by setting the ADDR[10:8] pins specified below. ADDR[7:0] is a direct address bus for permitting access to the internal registers.  ADDR[10:8]  000 = Master Device  001 = Chip Select Output 1 (Pin B21)  010 = Chip Select Output 2 (Pin D19)  011 = Chip Select Output 3 (Pin C20)  100 = Chip Select Output 4 (Pin A21)  101 = Chip Select Output 5 (Pin B20)  110 = Reserved  111 = All Chip Selects Active Including the Master Device  Note: Internally pulled "Low" with a 50k Ω resistor. |

| DATA7 DATA6 DATA5 DATA4 DATA3 DATA2 DATA1 DATA0                    | AA4<br>AB3<br>AC3<br>AA5<br>Y6<br>AB4<br>AC4<br>AB5                             | I/O  | <b>Bi-directional Data Bus</b> DATA[7:0] is a bi-directional data bus used for read and write operations. <b>Note:</b> Internally pulled "Low" with a 50k $\Omega$ resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| μPTS2<br>μPTS1<br>μPTS0                                            | AC23<br>AB22<br>AA21                                                            | I    | Microprocessor Type Select Input $\mu$ PTS[2:0] are used to select the microprocessor type interface. 000 = Intel 68HC11, 8051, 80C188 (Asynchronous) 001 = Motorola 68K (Asynchronous) 111 = Motorola MPC8260, MPC860 Power PC (Synchronous) Note: Internally pulled "Low" with a 50k $\Omega$ resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Reset                                                              | B22                                                                             | I    | Hardware Reset Input Active low signal. When this pin is pulled "Low" for more than $10\mu S$ , the internal registers are set to their default state. See the register description for the default values.  Note: Internally pulled "High" with a $50K\Omega$ resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CS5<br>CS4<br>CS3<br>CS2<br>CS1                                    | B20<br>A21<br>C20<br>D19<br>B21                                                 | 0    | Chip Select Output The XRT83VSH314 can be used to provide the necessary chip selects for up to 5 additional devices by using the 3 MSBs ADDR[10:8] from the 11-Bit address bus. The LIU allows up to 84-channel applications with only using one chip select. See the ADDR[10:0] definition in the pin description.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

# **RECEIVER SECTION**

| NAME                                                                                    | PIN                                                                                        | Түре |                                                                                        | Des                                                                                                     | CRIPTION                                                                                                                                                                                      |                                                       |

|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| RxON                                                                                    | AB19                                                                                       | I    | can be select<br>appropriate ch<br>ware pin is pu                                      | p, the receivers are powered through the microphannel register if the ha                                | wered off. Turning the rece processor interface by proardware pin is pulled "High are automatically turned of 50KΩ resistor.                                                                  | gramming the ". If the hard-                          |

| RxTSEL                                                                                  | Y15                                                                                        | I    | Upon power utermination caming the appropriate pin, Rx register. Once "High" to switch | n be selected through opriate channel registe FCNTL must be progr                                       |                                                                                                                                                                                               | te by program-<br>rol to the hard-<br>ropriate global |

|                                                                                         |                                                                                            |      |                                                                                        | RxTSEL (pin)                                                                                            | Rx Termination                                                                                                                                                                                |                                                       |

|                                                                                         |                                                                                            |      |                                                                                        | 0                                                                                                       | External                                                                                                                                                                                      |                                                       |

|                                                                                         |                                                                                            |      |                                                                                        | 1                                                                                                       | Internal                                                                                                                                                                                      |                                                       |

|                                                                                         |                                                                                            |      |                                                                                        | Note: RxTCNTL (bit)                                                                                     | must be set to "1"                                                                                                                                                                            |                                                       |

| RLOS                                                                                    | AB1                                                                                        | 0    | When a receive to ITU-T G.775 RLOS will rer Receive Loss Note: This pi                 | 5, the RLOS pin will go main "High" until the lof of Signal section of this in is for redundancy app    | for All 14-Channels) for any one of the 14-chan "High" for a minimum of on oss of signal condition cle s datasheet for more details colications to initiate an auto ual channel RLOS, see the | e RCLK cycle. ears. See the s. matic switch to        |

| RCLK13 RCLK12 RCLK11 RCLK10 RCLK9 RCLK8 RCLK7 RCLK6 RCLK5 RCLK4 RCLK3 RCLK2 RCLK1 RCLK1 | AB14<br>Y22<br>R22<br>P22<br>G22<br>F22<br>B14<br>B9<br>F2<br>G2<br>P2<br>R2<br>AA2<br>AA9 | 0    | signal is abse<br>an internal ma<br>RPOS/RNEG                                          | ecovered clock from the<br>nt or RxON is pulled "I<br>aster clock as its refer<br>data to be updated on | ne incoming data stream. I<br>Low", RCLK maintains its ti<br>rence. Software control (F<br>either edge of RCLK.<br>It applies to all 14 channels.                                             | iming by using RCLKE) allows                          |

# RECEIVER SECTION

| NAME                                                                                    | Pin                                                                                | Түре |                                                                        | Descr                                                     | RIPTION                |  |

|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|------|------------------------------------------------------------------------|-----------------------------------------------------------|------------------------|--|

| RCLKOUT                                                                                 | K1                                                                                 | 0    | Recovered Clo<br>One of the 14 F<br>0xEEh) bits and<br>See table below | ect [3:0] (register                                       |                        |  |

|                                                                                         |                                                                                    |      |                                                                        | Recovered Clock<br>Select[3:0]                            | Selected<br>RCLK[13:0] |  |

|                                                                                         |                                                                                    |      |                                                                        | 0000, 1111                                                | No RCLK Selected       |  |

|                                                                                         |                                                                                    |      |                                                                        | 0001                                                      | RCLK 0                 |  |

|                                                                                         |                                                                                    |      |                                                                        | 0010                                                      | RCLK 1                 |  |

|                                                                                         |                                                                                    |      |                                                                        | 0011                                                      | RCLK 2                 |  |

|                                                                                         |                                                                                    |      |                                                                        | 0100                                                      | RCLK 3                 |  |

|                                                                                         |                                                                                    |      |                                                                        | 0101                                                      | RCLK 4                 |  |

|                                                                                         |                                                                                    |      |                                                                        | 0110                                                      | RCLK 5                 |  |

|                                                                                         |                                                                                    |      |                                                                        | 0111                                                      | RCLK 6                 |  |

|                                                                                         |                                                                                    |      |                                                                        | 1000                                                      | RCLK 7                 |  |

|                                                                                         |                                                                                    |      |                                                                        | 1001                                                      | RCLK 8                 |  |

|                                                                                         |                                                                                    |      |                                                                        | 1010                                                      | RCLK 9                 |  |

|                                                                                         |                                                                                    |      |                                                                        | 1011                                                      | RCLK 10                |  |

|                                                                                         |                                                                                    |      |                                                                        | 1100                                                      | RCLK 11                |  |

|                                                                                         |                                                                                    |      |                                                                        | 1101                                                      | RCLK 12                |  |

|                                                                                         |                                                                                    |      |                                                                        | 1110                                                      | RCLK 13                |  |

| RPOS13 RPOS12 RPOS11 RPOS10 RPOS9 RPOS8 RPOS7 RPOS6 RPOS5 RPOS4 RPOS3 RPOS2 RPOS1 RPOS0 | Y14<br>W20<br>P20<br>N20<br>H20<br>G20<br>D14<br>D10<br>G4<br>H4<br>N4<br>P4<br>W4 | 0    |                                                                        | Output output pin. In dual rai single rail mode, this pir |                        |  |

# **RECEIVER SECTION**

| NAME    | Pin  | Түре | DESCRIPTION                                                                                                                                                 |

|---------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RNEG13  | AA14 | 0    | RNEG/LCV_OF Output                                                                                                                                          |

| RNEG12  | Y21  |      | In dual rail mode, this pin is the receive negative data output. In single rail                                                                             |

| RNEG11  | P21  |      | mode, this pin can either be a Line Code Violation or Overflow indicator. If LCV                                                                            |

| RNEG10  | N21  |      | is selected by software and if a line code violation, a bi-polar violation, or                                                                              |

| RNEG9   | H21  |      | excessive zeros occur, the LCV pin will pull "High" for a minimum of one RCLK cycle. LCV will remain "High" until there are no more violations. However, if |

| RNEG8   | G21  |      | OF is selected the LCV pin will pull "High" if the internal LCV counter is satu-                                                                            |

| RNEG7   | C14  |      | rated. The LCV pin will remain "High" until the LCV counter is reset.                                                                                       |

| RNEG6   | C10  |      | ,                                                                                                                                                           |

| RNEG5   | F3   |      |                                                                                                                                                             |

| RNEG4   | G3   |      |                                                                                                                                                             |

| RNEG3   | N3   |      |                                                                                                                                                             |

| RNEG2   | P3   |      |                                                                                                                                                             |

| RNEG1   | Y3   |      |                                                                                                                                                             |

| RNEG0   | AA10 |      |                                                                                                                                                             |

| RTIP13  | AC14 | 1    | Receive Differential Tip Input                                                                                                                              |

| RTIP12  | Y23  |      | RTIP is the positive differential input from the line interface. Along with the                                                                             |

| RTIP11  | T23  |      | RRING signal, these pins should be coupled to a 1:1 transformer for proper                                                                                  |

| RTIP10  | P23  |      | operation.                                                                                                                                                  |

| RTIP9   | G23  |      |                                                                                                                                                             |

| RTIP8   | E23  |      |                                                                                                                                                             |

| RTIP7   | A14  |      |                                                                                                                                                             |

| RTIP6   | A9   |      |                                                                                                                                                             |

| RTIP5   | E1   |      |                                                                                                                                                             |

| RTIP4   | G1   |      |                                                                                                                                                             |

| RTIP3   | P1   |      |                                                                                                                                                             |

| RTIP2   | T1   |      |                                                                                                                                                             |

| RTIP1   | Y1   |      |                                                                                                                                                             |

| RTIP0   | AC9  |      |                                                                                                                                                             |

| RRING13 | AC13 | 1    | Receive Differential Ring Input                                                                                                                             |

| RRING12 | W23  |      | RRING is the negative differential input from the line interface. Along with the                                                                            |

| RRING11 | U23  |      | RTIP signal, these pins should be coupled to a 1:1 transformer for proper operation                                                                         |

| RRING10 | N23  |      | ation.                                                                                                                                                      |

| RRING9  | H23  |      |                                                                                                                                                             |

| RRING8  | D23  |      |                                                                                                                                                             |

| RRING7  | A13  |      |                                                                                                                                                             |

| RRING6  | A10  |      |                                                                                                                                                             |

| RRING5  | D1   |      |                                                                                                                                                             |

| RRING4  | H1   |      |                                                                                                                                                             |

| RRING3  | N1   |      |                                                                                                                                                             |

| RRING2  | U1   |      |                                                                                                                                                             |

| RRING1  | W1   |      |                                                                                                                                                             |

| RRING0  | AC10 |      |                                                                                                                                                             |

# TRANSMITTER SECTION

| NAME                                                                                    | Pin                                                                                          | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TxON                                                                                    | AC20                                                                                         | I    | Transmit On/Off Input  Upon power up, the transmitters are powered off. Turning the transmitters On or Off is selected through the microprocessor interface by programming the appropriate channel register if this pin is pulled "High". If the TxON pin is pulled "Low", all 14 transmitters are powered off.  Notes:  1. TxON is ideal for redundancy applications. See the Redundancy Applications Section of this datasheet for more details.  2. Internally pulled "Low" with a 50KΩ resistor.      |

| DMO                                                                                     | Y4                                                                                           | 0    | Digital Monitor Output (Global Pin for All 14-Channels)  When no transmit output pulse is detected for more than 128 TCLK cycles on one of the 14-channels, the DMO pin will go "High" for a minimum of one TCLK cycle. DMO will remain "High" until the transmitter sends a valid pulse.  Note: This pin is for redundancy applications to initiate an automatic switch to the backup card. For individual channel DMO, see the register map.                                                            |

| TCLK13 TCLK12 TCLK11 TCLK10 TCLK9 TCLK8 TCLK7 TCLK6 TCLK5 TCLK4 TCLK4 TCLK3 TCLK2 TCLK1 | Y16<br>Y17<br>AC18<br>D16<br>C17<br>A19<br>B16<br>D7<br>A3<br>B5<br>B6<br>AC6<br>AC5         |      | Transmit Clock Input  TCLK is the input facility clock used to sample the incoming TPOS/TNEG data. If TCLK is absent, pulled "Low", or pulled "High", the transmitter outputs at TTIP/TRING can be selected to send an all ones or an all zero signal by programming TCLKCNL. In addition, software control (TCLKE) allows TPOS/TNEG data to be sampled on either edge of TCLK.  Notes:  1. TCLKE is a global setting that applies to all 14 channels.  2. Internally pulled "Low" with a 50k Ω resistor. |

| TPOS13 TPOS12 TPOS11 TPOS10 TPOS9 TPOS8 TPOS7 TPOS6 TPOS5 TPOS4 TPOS3 TPOS2 TPOS1 TPOS1 | AB17<br>AA18<br>AB18<br>A18<br>D17<br>B19<br>A17<br>B7<br>C4<br>B4<br>D6<br>AB6<br>AA6<br>Y8 | l    | TPOS/TDATA Input  Transmit digital input pin. In dual rail mode, this pin is the transmit positive data input. In single rail mode, this pin is the transmit non-return to zero (NRZ) data input.  Note: Internally pulled "Low" with a 50ΚΩ resistor.                                                                                                                                                                                                                                                    |

## REV. 1.0.1

# TRANSMITTER SECTION

| NAME    | Pin  | Түре | DESCRIPTION                                                                     |

|---------|------|------|---------------------------------------------------------------------------------|

| TNEG13  | AC17 |      | Transmit Negative Data Input                                                    |

| TNEG12  | AC19 |      | In dual rail mode, this pin is the transmit negative data input. In single rail |

| TNEG11  | AA17 |      | mode, this pin can be left unconnected.                                         |

| TNEG10  | B17  |      | <b>Note:</b> Internally pulled "Low" with a $50K\Omega$ resistor.               |

| TNEG9   | B18  |      |                                                                                 |

| TNEG8   | C18  |      |                                                                                 |

| TNEG7   | C16  |      |                                                                                 |

| TNEG6   | C7   |      |                                                                                 |

| TNEG5   | D5   |      |                                                                                 |

| TNEG4   | C5   |      |                                                                                 |

| TNEG3   | C6   |      |                                                                                 |

| TNEG2   | AA7  |      |                                                                                 |

| TNEG1   | Y7   |      |                                                                                 |

| TNEG0   | AB7  |      |                                                                                 |

| TTIP13  | AA13 | 0    | Transmit Differential Tip Output                                                |

| TTIP12  | W21  |      | TTIP is the positive differential output to the line interface. Along with the  |

| TTIP11  | R21  |      | TRING signal, these pins should be coupled to a 1:2 step up transformer for     |

| TTIP10  | M21  |      | proper operation.                                                               |

| TTIP9   | J21  |      |                                                                                 |

| TTIP8   | F21  |      |                                                                                 |

| TTIP7   | C13  |      |                                                                                 |

| TTIP6   | C11  |      |                                                                                 |

| TTIP5   | E3   |      |                                                                                 |

| TTIP4   | H3   |      |                                                                                 |

| TTIP3   | M3   |      |                                                                                 |

| TTIP2   | R3   |      |                                                                                 |

| TTIP1   | W3   |      |                                                                                 |

| TTIP0   | AA11 |      |                                                                                 |

| TRING13 | AB12 | 0    | Transmit Differential Ring Output                                               |

| TRING12 | V22  |      | TRING is the negative differential output to the line interface. Along with the |

| TRING11 | T20  |      | TTIP signal, these pins should be coupled to a 1:2 step up transformer for      |

| TRING10 | M22  |      | proper operation.                                                               |

| TRING9  | J22  |      |                                                                                 |

| TRING8  | D22  |      |                                                                                 |

| TRING7  | B12  |      |                                                                                 |

| TRING6  | B11  |      |                                                                                 |

| TRING5  | C2   |      |                                                                                 |

| TRING4  | H2   |      |                                                                                 |

| TRING3  | M2   |      |                                                                                 |

| TRING2  | U2   |      |                                                                                 |

| TRING1  | V3   |      |                                                                                 |

| TRING0  | AB11 |      |                                                                                 |

# **CONTROL FUNCTION**

| NAME   | Pin | Түре | DESCRIPTION                                                                                                                                                                         |

|--------|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TEST   | D4  | I    | Factory Test Mode For normal operation, the TEST pin should be tied to ground.  Note: Internally pulled "Low" with a $50k\Omega$ resistor.                                          |

| ĪCT    | A2  | I    | In Circuit Testing When this pin is tied "Low", all output pins are forced to "High" impedance for in circuit testing.  Note: Internally pulled "High" with a $50K\Omega$ resistor. |

| PhDIN  | L1  | I    | <b>Test Pin</b> For testing purposes only. For normal operation leave this pin unconnected. <b>Note:</b> Internally pulled "Low" with a $50k\Omega$ resistor.                       |

| CMPOUT | K2  | 0    | Test Pin For testing purposes only. For normal operation leave this pin unconnected.                                                                                                |

# **CLOCK SECTION**

| NAME       | Pin        | Түре | DESCRIPTION                                                                                                                                                                                                                                         |

|------------|------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MCLKin     | A6         | I    | Master Clock Input The master clock input can accept a wide range of inputs that can be used to generate T1 or E1 clock rates on a per channel basis. See the register map for details.  Note: Internally pulled "Low" with a $50k\Omega$ resistor. |

| 8kHzOUT    | D8         | 0    | 8kHz Output Clock                                                                                                                                                                                                                                   |

| MCLKE1out  | <b>A</b> 5 | 0    | 2.048MHz Output Clock                                                                                                                                                                                                                               |

| MCLKE1Nout | A4         | 0    | 2.048MHz, 4.096MHz, 8.192MHz, or 16.384MHz Output Clock See the register map for programming details.                                                                                                                                               |

| MCLKT1out  | <b>A</b> 7 | 0    | 1.544MHz Output Clock                                                                                                                                                                                                                               |

| MCLKT1Nout | B8         | 0    | 1.544MHz, 3.088MHz, 6.176MHz, or 12.352MHz Output Clock See the register map for programming details.                                                                                                                                               |

# JTAG SECTION

| NAME                | PIN        | Түре | DESCRIPTION                                                                                                                                                                                                                      |

|---------------------|------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ATP_TIP<br>ATP_RING | D21<br>K21 | I/O  | Analog Test Pin_TIP Analog Test Pin_RING These pins are used to check continuity of the Transmit and Receive TIP and RING connections on the assembled board.  Note: See "Section 5.7, Analog Board Continuity Check" on page 39 |

| TMS                 | E4         | I    | for more detailed description.  Test Mode Select  This pin is used as the input mode select for the boundary scan chain.  Note: Internally pulled "High" with a $50K\Omega$ resistor.                                            |

| TCK                 | B1         | I    | Test Clock Input This pin is used as the input clock source for the boundary scan chain.  Note: Internally pulled "High" with a $50K\Omega$ resistor.                                                                            |

| TDI                 | A1         | I    | Test Data In This pin is used as the input data pin for the boundary scan chain.  Note: Internally pulled "High" with a $50K\Omega$ resistor.                                                                                    |

| TDO                 | D3         | 0    | Test Data Out This pin is used as the output data pin for the boundary scan chain.                                                                                                                                               |

# **POWER AND GROUND**

| NAME                                                                                                 | Pin                                                                                 | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TVDD13 TVDD12 TVDD11 TVDD10 TVDD9 TVDD8 TVDD7 TVDD6 TVDD5 TVDD4 TVDD3 TVDD2 TVDD1                    | AB13<br>V21<br>T21<br>N22<br>H22<br>E21<br>B13<br>B10<br>D2<br>J3<br>N2<br>T3<br>U4 | PWR  | Transmit Analog Power Supply (3.3V ±5%)  TVDD can be shared with DVDD. However, it is recommended that TVDD be isolated from the analog power supply RVDD. For best results, use an internal power plane for isolation. If an internal power plane is not available, a ferrite bead can be used. Each power supply pin should be bypassed to ground through an external 0.1μF capacitor.                                               |

| TVDD0  RVDD13 RVDD12 RVDD11 RVDD10 RVDD9 RVDD8 RVDD7 RVDD6 RVDD5 RVDD4 RVDD3 RVDD2 RVDD1 RVDD1 RVDD1 | AB10 AC15 AA23 T22 R23 F23 E22 A15 A8 E2 F1 R1 T2 Y2 AB9                            | PWR  | Receive Analog Power Supply (3.3V ±5%) RVDD should not be shared with other power supplies. It is recommended that RVDD be isolated from the digital power supply DVDD and the analog power supply TVDD. For best results, use an internal power plane for isolation. If an internal power plane is not available, a ferrite bead can be used. Each power supply pin should be bypassed to ground through an external 0.1μF capacitor. |

| DVDD_DRV DVDD_DRV DVDD_DRV DVDD_DRV DVDD_DRV DVDD_DRV                                                | AC2<br>K3<br>U22<br>C21<br>AA16                                                     | PWR  | Digital Power Supply (3.3V ±5%)  DVDD should be isolated from the analog power supplies. For best results, use an internal power plane for isolation. If an internal power plane is not available, a ferrite bead can be used. Every two DVDD power supply pins should be bypassed to ground through at least one 0.1μF capacitor.  Digital Power Supply (1.8V ±5%)                                                                    |

| DVDD_PRE DVDD_PRE DVDD_PRE DVDD DVDD DVDD DVDD DVDD DVDD DVDD DV                                     | C3<br>D20<br>Y20<br>J2<br>V2<br>D12<br>AA12<br>U21<br>K23<br>AA15                   |      | DVDD should be isolated from the analog power supplies. For best results, use an internal power plane for isolation. If an internal power plane is not available, a ferrite bead can be used. Every two DVDD power supply pins should be bypassed to ground through at least one $0.1\mu F$ capacitor.                                                                                                                                 |

# 14-CHANNEL T1/E1/J1 SHORT-HAUL LINE INTERFACE UNIT

# **POWER AND GROUND**

| NAME       | PIN  | Түре | DESCRIPTION                                                                         |

|------------|------|------|-------------------------------------------------------------------------------------|

| AVDD_BIAS  | K4   | PWR  | Analog Power Supply (1.8V ±5%)                                                      |

| AVDD_PLL22 | C15  |      | AVDD should be isolated from the digital power supplies. For best results, use      |

| AVDD_PLL21 | B15  |      | an internal power plane for isolation. If an internal power plane is not available, |

| AVDD_PLL12 | AB16 |      | a ferrite bead can be used. Each power supply pin should be bypassed to             |

| AVDD_PLL11 | AC16 |      | ground through at least one 0.1μF capacitor.                                        |

| TGND13     | Y13  | GND  | Transmit Analog Ground                                                              |

| TGND12     | V20  |      | It's recommended that all ground pins of this device be tied together.              |

| TGND11     | R20  |      |                                                                                     |

| TGND10     | M20  |      |                                                                                     |

| TGND9      | J20  |      |                                                                                     |

| TGND8      | F20  |      |                                                                                     |

| TGND7      | D13  |      |                                                                                     |

| TGND6      | D11  |      |                                                                                     |

| TGND5      | F4   |      |                                                                                     |

| TGND4      | J4   |      |                                                                                     |

| TGND3      | M4   |      |                                                                                     |

| TGND2      | R4   |      |                                                                                     |

| TGND1      | V4   |      |                                                                                     |

| TGND0      | Y11  |      |                                                                                     |

| RGND13     | AC12 | GND  | Receive Analog Ground                                                               |