Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

JANUARY 2007

#### **GENERAL DESCRIPTION**

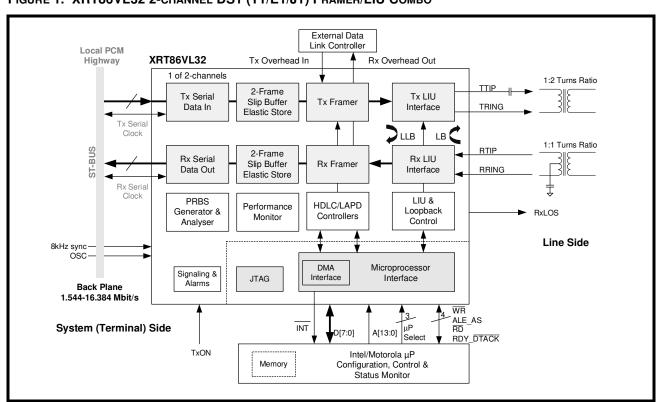

The XRT86VL32 is a two-channel 1.544 Mbit/s or 2.048 Mbit/s DS1/E1/J1 framer and LIU integrated solution featuring R³ technology (Relayless, Reconfigurable, Redundancy). The physical interface is optimized with internal impedance, and with the patented pad structure, the XRT86VL32 provides protection from power failures and hot swapping.

The XRT86VL32 contains an integrated DS1/E1/J1 framer and LIU which provide DS1/E1/J1 framing and error accumulation in accordance with ANSI/ITU\_T specifications. Each framer has its own framing synchronizer and transmit-receive slip buffers. The slip buffers can be independently enabled or disabled as required and can be configured to frame to the common DS1/E1/J1 signal formats.

Each Framer block contains its own Transmit and Receive T1/E1/J1 Framing function. There are 3 Transmit HDLC controllers per channel which encapsulate contents of the Transmit HDLC buffers into LAPD Message frames. There are 3 Receive HDLC controllers per channel which extract the

payload content of Receive LAPD Message frames from the incoming T1/E1/J1 data stream and write the contents into the Receive HDLC buffers. Each framer also contains a Transmit and Overhead Data Input port, which permits Data Link Terminal Equipment direct access to the outbound T1/E1/J1 frames. Likewise, a Receive Overhead output data port permits Data Link Terminal Equipment direct access to the Data Link bits of the inbound T1/E1/J1 frames.

REV. V1.2.0

The XRT86VL32 fully meets all of the latest T1/E1/J1 specifications: ANSI T1/E1.107-1988, ANSI T1/E1.403-1995, ANSI T1/E1.231-1993, ANSI T1/E1.408-1990, AT&T TR 62411 (12-90) TR54016, and ITU G-703, G.704, G706 and G.733, AT&T Pub. 43801, and ETS 300 011, 300 233, JT G.703, JT G.704, JT G706, I.431. Extensive test and diagnostic functions include Loop-backs, Boundary scan, Pseudo Random bit sequence (PRBS) test pattern generation, Performance Monitor, Bit Error Rate (BER) meter, forced error insertion, and LAPD unchannelized data payload processing according to ITU-T standard Q.921.

#### APPLICATIONS AND FEATURES (NEXT PAGE)

FIGURE 1. XRT86VL32 2-CHANNEL DS1 (T1/E1/J1) FRAMER/LIU COMBO

#### XRT86VL32

# Experience Our Connectivity. REV. V1.2.0

#### DUAL T1/E1/J1 FRAMER/LIU COMBO - T1 REGISTER DESCRIPTION

#### **APPLICATIONS**

- High-Density T1/E1/J1 interfaces for Multiplexers, Switches, LAN Routers and Digital Modems

- SONET/SDH terminal or Add/Drop multiplexers (ADMs)

- T1/E1/J1 add/drop multiplexers (MUX)

- Channel Service Units (CSUs): T1/E1/J1 and Fractional T1/E1/J1

- Digital Access Cross-connect System (DACs)

- Digital Cross-connect Systems (DCS)

- Frame Relay Switches and Access Devices (FRADS)

- ISDN Primary Rate Interfaces (PRA)

- PBXs and PCM channel bank

- T3 channelized access concentrators and M13 MUX

- Wireless base stations

- ATM equipment with integrated DS1 interfaces

- Multichannel DS1 Test Equipment

- T1/E1/J1 Performance Monitoring

- Voice over packet gateways

- Routers

#### **FEATURES**

- Two independent, full duplex DS1 Tx and Rx Framer/LIUs

- Two 512-bit (two-frame) elastic store, PCM frame slip buffers (FIFO) on TX and Rx provide up to 8.192 MHz asynchronous back plane connections with jitter and wander attenuation

- Supports input PCM and signaling data at 1.544, 2.048, 4.096 and 8.192 Mbits. Also supports 2-channel multiplexed 12.352/16.384 (HMVIP/H.100) Mbit/s on the back plane bus

- Programmable output clocks for Fractional T1/E1/J1

- Supports Channel Associated Signaling (CAS)

- Supports Common Channel Signalling (CCS)

- Supports ISDN Primary Rate Interface (ISDN PRI) signaling

- Extracts and inserts robbed bit signaling (RBS)

- 3 Integrated HDLC controllers per channel for transmit and receive, each controller having two 96-byte buffers (buffer 0 / buffer 1)

- HDLC Controllers Support SS7

- Timeslot assignable HDLC

- V5.1 or V5.2 Interface

- Automatic Performance Report Generation (PMON Status) can be inserted into the transmit LAPD interface every 1 second or for a single transmission

- Alarm Indication Signal with Customer Installation signature (AIS-CI)

- Remote Alarm Indication with Customer Installation (RAI-CI)

- Gapped Clock interface mode for Transmit and Receive.

- Intel/Motorola and Power PC interfaces for configuration, control and status monitoring

- Parallel search algorithm for fast frame synchronization

- Wide choice of T1 framing structures: SF/D4, ESF, SLC®96, T1DM and N-Frame (non-signaling)

- Direct access to D and E channels for fast transmission of data link information

- PRBS, QRSS, and Network Loop Code generation and detection

- Programmable Interrupt output pin

- Supports programmed I/O and DMA modes of Read-Write access

- Each framer block encodes and decodes the T1/E1/J1 Frame serial data

- Detects and forces Red (SAI), Yellow (RAI) and Blue (AIS) Alarms

- Detects OOF, LOF, LOS errors and COFA conditions

- Loopbacks: Local (LLB) and Line remote (LB)

- Facilitates Inverse Multiplexing for ATM

- Performance monitor with one second polling

- Boundary scan (IEEE 1149.1) JTAG test port

- Accepts external 8kHz Sync reference

- 1.8V Inner Core

- 3.3V CMOS operation with 5V tolerant inputs

- 225-pin PBGA package with -40°C to +85°C operation

#### ORDERING INFORMATION

| PART NUMBER | PACKAGE                     | OPERATING TEMPERATURE RANGE |

|-------------|-----------------------------|-----------------------------|

| XRT86VL32IB | 225 Plastic Ball Grid Array | -40°C to +85°C              |

#### XRT86VL32

## DUAL T1/E1/J1 FRAMER/LIU COMBO - T1 REGISTER DESCRIPTION

## LIST OF PARAGRAPHS

| 1.0 REGISTER DESCRIPTIONS - T1 MODE             | 9   |

|-------------------------------------------------|-----|

| 2.0 LINE INTERFACE UNIT (LIU SECTION) REGISTERS | 124 |

## **LIST OF FIGURES**

| Figure 1.: XRT86VL32 2-channel DS1 (T1/E1/J1) Framer/LIU Combo |

|----------------------------------------------------------------|

|----------------------------------------------------------------|

## LIST OF TABLES

| Table 1:: Register Summary                                            |                               | 4  |

|-----------------------------------------------------------------------|-------------------------------|----|

| Table 2:: Clock Select Register(CSR)                                  | Hex Address: 0xn100           |    |

| Table 3:: Line Interface Control Register (LICR)                      | Hex Address: 0xn101           | 11 |

| Table 4:: Framing Select Register (FSR)                               | Hex Address: 0xn107           | 13 |

| Table 5:: Alarm Generation Register (AGR)                             | Hex Address: 0xn108           | 15 |

| Table 6:: yellow alarm duration and format when one second rule is no | ot enforced                   | 16 |

| Table 7:: yellow alarm format when one second rule is enforced        |                               | 17 |

| Table 8:: Synchronization MUX Register (SMR)                          | Hex Address: 0xn109           | 19 |

| Table 9:: Transmit Signaling and Data Link Select Register (TSDLSR)   |                               |    |

| Table 10:: Framing Control Register (FCR)                             | Hex Address: 0xn10B           |    |

| Table 11:: Receive Signaling & Data Link Select Register (RSDLSR)     | Hex Address: 0xn10C           |    |

| Table 12:: Receive Signaling Change Register 0 (RSCR 0)               | Hex Address: 0xn10D           | 27 |

| Table 13:: Receive Signaling Change Register 1(RSCR 1)                | Hex Address: 0xn10E           |    |

| Table 14:: Receive Signaling Change Register 2 (RSCR 2)               | Hex Address: 0xn10F           |    |

| Table 15:: Receive In Frame Register (RIFR)                           | Hex Address: 0xn112           |    |

| Table 16:: Data Link Control Register (DLCR1)                         | Hex Address: 0xn113           |    |

| Table 17:: Transmit Data Link Byte Count Register (TDLBCR1)           | Hex Address: 0xn114           |    |

| Table 18:: Receive Data Link Byte Count Register (RDLBCR1)            | Hex Address: 0xn115           |    |

| Table 19:: Slip Buffer Control Register (SBCR)                        | Hex Address: 0xn116           |    |

| Table 20:: FIFO Latency Register (FFOLR)                              | Hex Address: 0xn117           |    |

| Table 21:: DMA 0 (Write) Configuration Register (D0WCR)               | Hex Address: 0xn118           |    |

| Table 22:: DMA 1 (Read) Configuration Register (D1RCR)                | Hex Address: 0xn119           |    |

| Table 23:: Interrupt Control Register (ICR)                           | Hex Address: 0xn11A           |    |

| Table 24:: LAPD Select Register (LAPDSR)                              | Hex Address: 0xn11B           |    |

| Table 25:: Customer Installation Alarm Generation Register (CIAGR)    | Hex Address: 0xn11C           |    |

| Table 26:: Performance Report Control Register (PRCR)                 | Hex Address: 0xn11D           |    |

| Table 27:: Gapped Clock Control Register (GCCR)                       | Hex Address: 0xn11E           |    |

| Table 28:: Transmit Interface Control Register (TICR)                 | Hex Address:0xn120            |    |

| Table 29:: Transmit Interface Speed When Multiplexed Mode is Disab    |                               |    |

| Table 30:: Transmit Interface Speed when Multiplexed Mode is Enable   |                               |    |

| Table 31:: PRBS Control & Status Register (PRBSCSR0)                  | Hex Address: 0xn121           |    |

| Table 32:: Receive Interface Control Register (RICR)                  | Hex Address: 0xn122           |    |

| Table 33:: Receive Interface Speed When Multiplexed Mode is Disable   |                               |    |

| Table 34:: Receive Interface Speed when Multiplexed Mode is Enable    |                               |    |

| Table 35:: PRBS Control & Status Register (PRBSCSR1)                  | Hex Address: 0xn123           |    |

| Table 36:: Loopback Code Control Register (LCCR)                      | Hex Address: 0xn124           |    |

| Table 37:: Transmit Loopback Coder Register (TLCR)                    | Hex Address: 0xn125           |    |

| Table 38:: Receive Loopback Activation Code Register (RLACR)          | Hex Address: 0xn126           |    |

| Table 39:: Receive Loopback Deactivation Code Register (RLDCR)        | Hex Address: 0xn127           |    |

| Table 40:: Defect Detection Enable Register (DDER)                    | Hex Address: 0xn129           |    |

| Table 41:: Transmit SPRM Control Register (TSPRMCR)                   | Hex Address: 0xn142           |    |

| Table 42:: Data Link Control Register (DLCR2)                         | Hex Address: 0xn143           |    |

| Table 43:: Transmit Data Link Byte Count Register (TDLBCR2)           | Hex Address: 0xn144           |    |

| Table 44:: Receive Data Link Byte Count Register (RDLBCR2)            | Hex Address: 0xn145           |    |

| Table 45:: Data Link Control Register (DLCR3)                         | Hex Address: 0xn153           |    |

| Table 46:: Transmit Data Link Byte Count Register (TDLBCR3)           | Hex Address: 0xn154           |    |

| Table 47:: Receive Data Link Byte Count Register (RDLBCR3)            | Hex Address: 0xn155           |    |

| Table 48:: Device ID Register (DEVID)                                 | Hex Address: 0xn1FE           |    |

| Table 49:: Revision ID Register (REVID)                               | Hex Address: 0xn1FF           |    |

| Table 50:: Transmit Channel Control Register 0-23 (TCCR 0-23)         | Hex Address: 0xn300 to 0xn317 |    |

| Table 51:: Transmit User Code Register 0-23 (TUCR 0-23)               | Hex Address: 0xn320 to 0xn337 |    |

|                                                                       | Hex Address: 0xn340 to 0xn357 |    |

| Table 53:: Receive Channel Control Register 0-23 (RCCR 0-23)          | Hex Address: 0xn360 to 0xn377 |    |

| Table 54:: Receive User Code Register 0-23 (RUCR 0-23)                | Hex Address: 0xn380 to 0xn397 |    |

| Table 55:: Receive Signaling Control Register 0-23 (RSCR 0-23)        | Hex Address: 0xn3A0 to 0xn3B7 |    |

| Table 56:: Receive Substitution Signaling Register 0-23 (RSSR 0-23)   |                               |    |

| Table 57:: Receive Signaling Array Register 0 to 23 (RSAR 0-23)       | Hex Address: 0Xn500 to 0xn517 |    |

| Table 58:: LAPD Buffer () Control Register (LAPDBCRO)                 | Hex Address: 0xn600           |    |

REV. V1.2.0

## DUAL T1/E1/J1 FRAMER/LIU COMBO - T1 REGISTER DESCRIPTION

| Table 59:: LAPD Buffer 1 Control Register (LAPDBCR1) Hex Addi                                              | ress: 0xn700          | 78  |

|------------------------------------------------------------------------------------------------------------|-----------------------|-----|

| Table 60:: PMON Receive Line Code Violation Counter MSB (RLCVCU)                                           | Hex Address: 0xn900   | 79  |

| Table 61:: PMON Receive Line Code Violation Counter LSB (RLCVCL)                                           | Hex Address: 0xn901   | 79  |

| Table 62:: PMON Receive Framing Alignment Bit Error Counter MSB (RFAECU)                                   | ) Hex Address: 0xn902 | 80  |

| Table 63:: PMON Receive Framing Alignment Bit Error Counter LSB (RFAECL)                                   |                       |     |

| Table 64:: PMON Receive Severely Errored Frame Counter (RSEFC)                                             | Hex Address: 0xn904   |     |

| Table 65:: PMON Receive CRC-6 BIT Error Counter - MSB (RSBBECU)                                            | Hex Address: 0xn905   |     |

| Table 66:: PMON Receive CRC-6 Bit Error Counter - LSB (RSBBECL)                                            | Hex Address: 0xn906   |     |

| Table 67:: PMON Receive Slip Counter (RSC)                                                                 | Hex Address: 0xn909   |     |

| Table 68:: PMON Receive Loss of Frame Counter (RLFC)                                                       | Hex Address: 0xn90A   |     |

| Table 69:: PMON Receive Change of Frame Alignment Counter (RCFAC)                                          | Hex Address: 0xn90B   |     |

| Table 70:: PMON LAPD1 Frame Check Sequence Error Counter 1 (LFCSEC1)                                       | Hex Address: 0xn90C   |     |

| Table 71:: PRBS Bit Error Counter MSB (PBECU)                                                              | Hex Address: 0xn90D   |     |

| Table 71:: PRBS Bit Error Counter MSB (PBECL)                                                              | Hex Address: 0xn90E   |     |

|                                                                                                            |                       |     |

| Table 73:: Transmit Slip Counter (TSC)                                                                     | Hex Address: 0xn90F   |     |

| Table 74:: Excessive Zero Violation Counter MSB (EZVCU)                                                    | Hex Address: 0xn910   |     |

| Table 75:: Excessive Zero Violation Counter LSB (EZVCL)                                                    | Hex Address: 0xn911   |     |

| Table 76:: PMON LAPD2 Frame Check Sequence Error Counter 2 (LFCSEC2)                                       | Hex Address: 0xn91C   |     |

| Table 77:: PMON LAPD2 Frame Check Sequence Error Counter 3 (LFCSEC3)                                       | Hex Address: 0xn92C   |     |

| Table 78:: Block Interrupt Status Register (BISR)                                                          | Hex Address: 0xnB00   |     |

| Table 79:: Block Interrupt Enable Register (BIER)                                                          | Hex Address: 0xnB01   |     |

| Table 80:: Alarm & Error Interrupt Status Register (AEISR)                                                 | Hex Address: 0xnB02   |     |

| Table 81:: Alarm & Error Interrupt Enable Register (AEIER)                                                 | Hex Address: 0xnB03   |     |

| Table 82:: Framer Interrupt Status Register (FISR)                                                         | Hex Address: 0xnB04   |     |

| Table 83:: Framer Interrupt Enable Register (FIER)                                                         | Hex Address: 0xnB05   |     |

| Table 84:: Data Link Status Register 1 (DLSR1)                                                             | Hex Address: 0xnB06   | 98  |

| Table 85:: Data Link Interrupt Enable Register 1 (DLIER1)                                                  | Hex Address: 0xnB07   | 100 |

| Table 86:: Slip Buffer Interrupt Status Register (SBISR)                                                   | Hex Address: 0xnB08   | 102 |

| Table 87:: Slip Buffer Interrupt Enable Register (SBIER)                                                   | Hex Address: 0xnB09   | 105 |

| Table 88:: Receive Loopback Code Interrupt and Status Register (RLCISR)                                    | Hex Address: 0xnB0A   | 107 |

| Table 89:: Receive Loopback Code Interrupt Enable Register (RLCIER)                                        | Hex Address: 0xnB0B   |     |

| Table 90:: Excessive Zero Status Register (EXZSR)                                                          | Hex Address: 0xnB0E   |     |

| Table 91:: Excessive Zero Enable Register (EXZER)                                                          | Hex Address: 0xnB0F   |     |

| Table 92:: SS7 Status Register for LAPD1 (SS7SR1)                                                          | Hex Address: 0xnB10   |     |

| Table 93:: SS7 Enable Register for LAPD1 (SS7ER1)                                                          | Hex Address: 0xnB11   |     |

| Table 94:: RxLOS/CRC Interrupt Status Register (RLCISR)                                                    | Hex Address: 0xnB12   |     |

| Table 95:: RxLOS/CRC Interrupt Enable Register (RLCIER)                                                    | Hex Address: 0xnB13   |     |

| Table 96:: Data Link Status Register 2 (DLSR2)                                                             | Hex Address: 0xnB16   |     |

| Table 97:: Data Link Olatas Hogister 2 (DLIER2)                                                            | Hex Address: 0xnB17   |     |

| Table 98:: SS7 Status Register for LAPD2 (SS7SR2)                                                          | Hex Address: 0xnB18   |     |

| Table 99:: SS7 Enable Register for LAPD2 (SS7ER2)                                                          | Hex Address: 0xnB19   |     |

| Table 100:: Data Link Status Register 3 (DLSR3)                                                            | Hex Address: 0xnB26   |     |

| Table 100:. Data Link Status Register 3 (DL3R3) Table 101:: Data Link Interrupt Enable Register 3 (DLIER3) |                       |     |

|                                                                                                            | Hex Address: 0xnB27   |     |

| Table 102:: SS7 Status Register for LAPD3 (SS7SR3)                                                         | Hex Address: 0xnB28   |     |

| Table 103:: SS7 Enable Register for LAPD3 (SS7ER3)                                                         | Hex Address: 0xnB29   |     |

| Table 104:: Customer Installation Alarm Status Register (CIASR)                                            | Hex Address: 0xnB40   |     |

| Table 105:: Customer Installation Alarm Status Register (CIAIER)                                           | Hex Address: 0xnB41   |     |

| Table 106:: LIU Channel Control Register 0 (LIUCCR0)                                                       | Hex Address: 0x0Fn0   |     |

| Table 107:: Equalizer Control and Transmit Line Build Out                                                  |                       |     |

| Table 108:: LIU Channel Control Register 1 (LIUCCR1)                                                       | Hex Address: 0x0Fn1   |     |

| Table 109:: LIU Channel Control Register 2 (LIUCCR2)                                                       | Hex Address: 0x0Fn2   | 129 |

| Table 110:: LIU Channel Control Register 3 (LIUCCR3)                                                       | Hex Address: 0x0Fn3   | 131 |

| Table 111:: LIU Channel Control Interrupt Enable Register (LIUCCIER)                                       | Hex Address: 0x0Fn4   |     |

| Table 112:: LIU Channel Control Status Register (LIUCCSR)                                                  | Hex Address: 0x0Fn5   | 135 |

| Table 113:: LIU Channel Control Interrupt Status Register (LIUCCISR)                                       | Hex Address: 0x0Fn6   | 138 |

| Table 114:: LIU Channel Control Cable Loss Register (LIUCCCCR)                                             | Hex Address: 0x0Fn7   | 139 |

| Table 115:: LIU Channel Control Arbitrary Register 1 (LIUCCAR1)                                            | Hex Address: 0x0Fn8   |     |

|                                                                                                            | Hex Address: 0x0Fn9   |     |

| , , ,                                                                                                      | Hex Address: 0x0FnA   |     |

| , , ,                                                                                                      | Hex Address: 0x0FnD   |     |

| ( <del> </del>                                                                                             |                       |     |

#### XRT86VL32

## DUAL T1/E1/J1 FRAMER/LIU COMBO - T1 REGISTER DESCRIPTION REV. V1.2.0

| Table 118:: LIU Channel Control Arbitrary Register 4 (LIUCCAR4) Table 119:: LIU Channel Control Arbitrary Register 5 (LIUCCAR5) Table 121:: LIU Channel Control Arbitrary Register 7 (LIUCCAR7) Table 122:: LIU Channel Control Arbitrary Register 8 (LIUCCAR8) Table 123:: LIU Global Control Register 0 (LIUGCR0) Table 124:: LIU Global Control Register 1 (LIUGCR1) Table 125:: LIU Global Control Register 2 (LIUGCR2) | Hex Address: 0x0FnB       141         Hex Address: 0x0FnC       141         Hex Address: 0x0FnE       142         Hex Address: 0x0FnF       143         Hex Address: 0x0FE1       144         Hex Address: 0x0FE2       145 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 125:: LIU Global Control Register 2 (LIUGCR2)                                                                                                                                                                                                                                                                                                                                                                         | Hex Address: 0x0FE2145                                                                                                                                                                                                      |

| Table 126:: LIU Global Control Register 3 (LIUGCR3) Table 127:: LIU Global Control Register 4 (LIUGCR4)                                                                                                                                                                                                                                                                                                                     | Hex Address: 0x0FE4146<br>Hex Address: 0x0FE9147                                                                                                                                                                            |

| Table 128:: LIU Global Control Register 5 (LIUGCR5)                                                                                                                                                                                                                                                                                                                                                                         | Hex Address: 0x0FEA148                                                                                                                                                                                                      |

### **DESCRIPTION OF THE CONTROL REGISTERS - T1 MODE**

All address on this register description is shown in HEX format, where n indicates channels 0 and 2 in the 2-channel device.

TABLE 1: REGISTER SUMMARY

| Function                                         | SYMBOL   | HEX                |  |  |

|--------------------------------------------------|----------|--------------------|--|--|

| Control Registers (0xn100 - 0xn1FF)              |          |                    |  |  |

| Clock and Select Register                        | CSR      | 0xn100             |  |  |

| Line Interface Control Register                  | LICR     | 0xn101             |  |  |

| Reserved                                         | -        | 0xn102 - 0xn106    |  |  |

| Framing Select Register                          | FSR      | 0xn107             |  |  |

| Alarm Generation Register                        | AGR      | 0xn108             |  |  |

| Synchronization MUX Register                     | SMR      | 0xn109             |  |  |

| Transmit Signaling and Data Link Select Register | TSDLSR   | 0xn10A             |  |  |

| Framing Control Register                         | FCR      | 0xn10B             |  |  |

| Receive Signaling & Data Link Select Register    | RSDLSR   | 0xn10C             |  |  |

| Receive Signaling Change Register 0              | RSCR0    | 0xn10D             |  |  |

| Receive Signaling Change Register 1              | RSCR1    | 0xn10E             |  |  |

| Receive Signaling Change Register 2              | RSCR2    | 0xn10F             |  |  |

| Reserved - E1 mode only                          | -        | 0xn110 -<br>0xn111 |  |  |

| Receive In-Frame Register                        | RIFR     | 0xn112             |  |  |

| Data Link Control Register 1                     | DLCR1    | 0xn113             |  |  |

| Transmit Data Link Byte Count Register 1         | TDLBCR1  | 0xn114             |  |  |

| Receive Data Link Byte Count Register 1          | RDLBCR1  | 0xn115             |  |  |

| Slip Buffer Control Register                     | SBCR     | 0xn116             |  |  |

| FIFO Latency Register                            | FIFOLR   | 0xn117             |  |  |

| DMA 0 (Write) Configuration Register             | D0WCR    | 0xn118             |  |  |

| DMA 1 (Read) Configuration Register              | D1RCR    | 0xn119             |  |  |

| Interrupt Control Register                       | ICR      | 0xn11A             |  |  |

| LAPD Select Register                             | LAPDSR   | 0xn11B             |  |  |

| Customer Installation Alarm Generation Register  | CIAGR    | 0xn11C             |  |  |

| Performance Report Control Register              | PRCR     | 0xn11D             |  |  |

| Gapped Clock Control Register                    | GCCR     | 0xn11E             |  |  |

| Transmit Interface Control Register              | TICR     | 0xn120             |  |  |

| PRBS Control & Status - Register 0               | PRBSCSR0 | 0xn121             |  |  |

#### TABLE 1: REGISTER SUMMARY

| Function                                      | SYMBOL    | HEX                |  |  |

|-----------------------------------------------|-----------|--------------------|--|--|

| Receive Interface Control Register            | RICR      | 0xn122             |  |  |

| PRBS Control & Status - Register 1            | PRBSCSR1  | 0xn123             |  |  |

| Loopback Code Control Register                | LCCR      | 0xn124             |  |  |

| Transmit Loopback Code Register               | TLCR      | 0xn125             |  |  |

| Receive Loopback Activation Code Register     | RLACR     | 0xn126             |  |  |

| Receive Loopback Deactivation Code Register   | RLDCR     | 0xn127             |  |  |

| Defect Detection Enable Register              | DDER      | 0xn129             |  |  |

| Reserved - E1 mode only                       | -         | 0xn130 - 0xn13F    |  |  |

| Transmit SPRM Control Register                | TSPRMCR   | 0xn142             |  |  |

| Data Link Control Register 2                  | DLCR2     | 0xn143             |  |  |

| Transmit Data Link Byte Count Register 2      | TDLBCR2   | 0xn144             |  |  |

| Receive Data Link Byte Count Register 2       | RDLBCR2   | 0xn145             |  |  |

| Data Link Control Register 3                  | DLCR3     | 0xn153             |  |  |

| Transmit Data Link Byte Count Register 3      | TDLBCR3   | 0xn154             |  |  |

| Receive Data Link Byte Count Register 3       | RDLBCR3   | 0xn155             |  |  |

| Device ID Register                            | DEVID     | 0xn1FE             |  |  |

| Revision Number Register                      | REVID     | 0xn1FF             |  |  |

| Time Slot (payload) Control (0xn300 - 0xn3FF) |           |                    |  |  |

| Transmit Channel Control Register 0-23        | TCCR 0-23 | 0xn300 - 0xn317    |  |  |

| Transmit User Code Register 0-23              | TUCR 0-23 | 0xn320 - 0xn337    |  |  |

| Transmit Signaling Control Register 0-23      | TSCR 0-23 | 0xn340 - 0xn357    |  |  |

| Receive Channel Control Register 0-23         | RCCR 0-23 | 0xn360 - 0xn377    |  |  |

| Receive User Code Register 0-23               | RUCR 0-23 | 0xn380 - 0xn397    |  |  |

| Receive Signaling Control Register 0-23       | RSCR 0-23 | 0xn3A0 - 0xn3B7    |  |  |

| Receive Substitution Signaling Register 0-23  | RSSR 0-23 | 0xn3C0 - 0xn3D7    |  |  |

| Receive Signaling Array (0xn500 - 0xn51F)     |           |                    |  |  |

| Receive Signaling Array Register 0            | RSAR0-23  | 0xn500 -<br>0xn517 |  |  |

| LAPDn Buffer 0                                |           |                    |  |  |

| LAPD Buffer 0 Control Register                | LAPDBCR0  | 0xn600 -<br>0xn660 |  |  |

| LAPDn Buffer 1                                | 1         | •                  |  |  |

| LAPD Buffer 1 Control Register                | LAPDBCR1  | 0xn700 -<br>0xn760 |  |  |

TABLE 1: REGISTER SUMMARY

| Function                                                           | SYMBOL  | HEX             |  |  |

|--------------------------------------------------------------------|---------|-----------------|--|--|

| Performance Monitor                                                |         |                 |  |  |

| Receive Line Code Violation Counter: MSB                           | RLCVCU  | 0xn900          |  |  |

| Receive Line Code Violation Counter: LSB                           | RLCVCL  | 0xn901          |  |  |

| Receive Frame Alignment Error Counter: MSB                         | RFAECU  | 0xn902          |  |  |

| Receive Frame Alignment Error Counter: LSB                         | RFAECL  | 0xn903          |  |  |

| Receive Severely Errored Frame Counter                             | RSEFC   | 0xn904          |  |  |

| Receive Synchronization Bit (CRC-6) Error Counter: MSB             | RSBBECU | 0xn905          |  |  |

| Receive Synchronization Bit (CRC-6) Error Counter: LSB             | RSBBECL | 0xn906          |  |  |

| Reserved - E1 Mode Only                                            |         | 0xn907 - 0xn908 |  |  |

| Receive Slip Counter                                               | RSC     | 0xn909          |  |  |

| Receive Loss of Frame Counter                                      | RLFC    | 0xn90A          |  |  |

| Receive Change of Frame Alignment Counter                          | RCOAC   | 0xn90B          |  |  |

| LAPD Frame Check Sequence Error counter 1                          | LFCSEC1 | 0xn90C          |  |  |

| PRBS bit Error Counter: MSB                                        | PBECU   | 0xn90D          |  |  |

| PRBS bit Error Counter: LSB                                        | PBECL   | 0xn90E          |  |  |

| Transmit Slip Counter                                              | TSC     | 0xn90F          |  |  |

| Excessive Zero Violation Counter: MSB                              | EZVCU   | 0xn910          |  |  |

| Excessive Zero Violation Counter: LSB                              | EZVCL   | 0xn911          |  |  |

| LAPD Frame Check Sequence Error counter 2                          | LFCSEC2 | 0xn91C          |  |  |

| LAPD Frame Check Sequence Error counter 3                          | LFCSEC3 | 0xn92C          |  |  |

| Interrupt Generation/Enable Register Address Map (0xnB00 - 0xnB41) |         |                 |  |  |

| Block Interrupt Status Register                                    | BISR    | 0xnB00          |  |  |

| Block Interrupt Enable Register                                    | BIER    | 0xnB01          |  |  |

| Alarm & Error Interrupt Status Register                            | AEISR   | 0xnB02          |  |  |

| Alarm & Error Interrupt Enable Register                            | AEIER   | 0xnB03          |  |  |

| Framer Interrupt Status Register                                   | FISR    | 0xnB04          |  |  |

| Framer Interrupt Enable Register                                   | FIER    | 0xnB05          |  |  |

| Data Link Status Register 1                                        | DLSR1   | 0xnB06          |  |  |

| Data Link Interrupt Enable Register 1                              | DLIER1  | 0xnB07          |  |  |

| Slip Buffer Interrupt Status Register                              | SBISR   | 0xnB08          |  |  |

| Slip Buffer Interrupt Enable Register                              | SBIER   | 0xnB09          |  |  |

| Receive Loopback code Interrupt and Status Register                | RLCISR  | 0xnB0A          |  |  |

| Receive Loopback code Interrupt Enable Register                    | RLCIER  | 0xnB0B          |  |  |

#### TABLE 1: REGISTER SUMMARY

| Function                                              | SYMBOL   | HEX             |

|-------------------------------------------------------|----------|-----------------|

| Reserved - E1 Mode Only                               | -        | 0xnB0C - 0xnB0D |

| Excessive Zero Status Register                        | EXZSR    | 0xnB0E          |

| Excessive Zero Enable Register                        | EXZER    | 0xnB0F          |

| SS7 Status Register for LAPD 1                        | SS7SR1   | 0xnB10          |

| SS7 Enable Register for LAPD 1                        | SS7ER1   | 0xnB11          |

| RxLOS/CRC Interrupt Status Register                   | RLCISR   | 0xnB12          |

| RxLOS/CRC Interrupt Enable Register                   | RLCIER   | 0xnB13          |

| Data Link Status Register 2                           | DLSR2    | 0xnB16          |

| Data Link Interrupt Enable Register 2                 | DLIER2   | 0xnB17          |

| SS7 Status Register for LAPD 2                        | SS7SR2   | 0xnB18          |

| SS7 Enable Register for LAPD 2                        | SS7ER2   | 0xnB19          |

| Data Link Status Register 3                           | DLSR3    | 0xnB26          |

| Data Link Interrupt Enable Register 3                 | DLIER3   | 0xnB27          |

| SS7 Status Register for LAPD 3                        | SS7SR3   | 0xnB28          |

| SS7 Enable Register for LAPD 3                        | SS7ER3   | 0xnB29          |

| Customer Installation Alarm Status Register           | CIASR    | 0xnB40          |

| Customer Installation Alarm Interrupt Enable Register | CIAIER   | 0xnB41          |

| LIU Register Summary - Channel Control Registers      |          |                 |

| LIU Channel Control Register 0                        | LIUCCR0  | 0x0Fn0          |

| LIU Channel Control Register 1                        | LIUCCR1  | 0x0Fn1          |

| LIU Channel Control Register 2                        | LIUCCR2  | 0x0Fn2          |

| LIU Channel Control Register 3                        | LIUCCR3  | 0x0Fn3          |

| LIU Channel Control Interrupt Enable Register         | LIUCCIER | 0x0Fn4          |

| LIU Channel Control Status Register                   | LIUCCSR  | 0x0Fn5          |

| LIU Channel Control Interrupt Status Register         | LIUCCISR | 0x0Fn6          |

| LIU Channel Control Cable Loss Register               | LIUCCCCR | 0x0Fn7          |

| LIU Channel Control Arbitrary Register 1              | LIUCCAR1 | 0x0Fn8          |

| LIU Channel Control Arbitrary Register 2              | LIUCCAR2 | 0x0Fn9          |

| LIU Channel Control Arbitrary Register 3              | LIUCCAR3 | 0x0FnA          |

| LIU Channel Control Arbitrary Register 4              | LIUCCAR4 | 0x0FnB          |

| LIU Channel Control Arbitrary Register 5              | LIUCCAR5 | 0x0FnC          |

| LIU Channel Control Arbitrary Register 6              | LIUCCAR6 | 0x0FnD          |

| LIU Channel Control Arbitrary Register 7              | LIUCCAR7 | 0x0FnE          |

#### TABLE 1: REGISTER SUMMARY

| Function                                        | SYMBOL   | HEX                |  |

|-------------------------------------------------|----------|--------------------|--|

| LIU Channel Control Arbitrary Register 8        | LIUCCAR8 | 0x0FnF             |  |

| Reserved                                        | -        | 0x0F80 -<br>0x0FDF |  |

| LIU Register Summary - Global Control Registers |          |                    |  |

| LIU Global Control Register 0                   | LIUGCR0  | 0x0FE0             |  |

| LIU Global Control Register 1                   | LIUGCR1  | 0x0FE1             |  |

| LIU Global Control Register 2                   | LIUGCR2  | 0x0FE2             |  |

| LIU Global Control Register 3                   | LIUGCR3  | 0x0FE4             |  |

| LIU Global Control Register 4                   | LIUGCR4  | 0x0FE9             |  |

| LIU Global Control Register 5                   | LIUGCR5  | 0x0FEA             |  |

| Reserved                                        | -        | 0x0FEB -<br>0x0FFF |  |

#### 1.0 REGISTER DESCRIPTIONS - T1 MODE

All address on this register description is shown in HEX format, where n indicates channels 0 and 2 in the 2-channel device

TABLE 2: CLOCK SELECT REGISTER(CSR)

| Віт | FUNCTION                      | Түре | DEFAULT | DESCRIPTION-OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|-------------------------------|------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | LCV Insert                    | R/W  | 0       | Line Code Violation Insertion This bit is used to force a Line Code Violation (LCV) on the transmit output of TTIP/TRING. A "0" to "1" transition on this bit will cause a single LCV to be inserted on the transmit output of TTIP/TRING.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6   | Set T1 Mode                   | R/W  | 0       | T1 Mode select This bit is used to program the individual channel to operate in either T1 or E1 mode.  0 = Configures the selected channel to operate in E1 mode.  1 = Configures the selected channel to operate in T1 mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5   | Sync All Transmitters to 8kHz | R/W  | 0       | Sync All Transmit Framers to 8kHz  This bit permits the user to configure each of the two (2) Transmit T1 Framer blocks to synchronize their "transmit output" frame alignment with the 8kHz signal that is derived from the MCLK PLL, as described below.  0 - Disables the "Sync all Transmit Framers to 8kHz" feature for all 2 channels.  1 - Enables the "Sync all Transmit Framers to 8kHz" feature for all 2 channels.  Note: Writing to this bit in register 0x0100 will enable this feature for all 2 channels.  Note: This bit is only active if the MCLK PLL is used as the "Timing Source" for the Transmit T1 Framer" blocks. CSS[1:0] of this register allows users to select the transmit source of the framer. |

| 4   | Clock Loss Detect             | R/W  | 1       | Clock Loss Detect Enable/Disable Select  This bit enables a clock loss protection feature for the Framer whenever the recovered line clock is used as the timing source for the transmit section. If the LIU loses clock recovery, the Clock Distribution Block will detect this occurrence and automatically begin to use the internal clock derived from MCLK PLL as the Transmit source, until the LIU is able to regain clock recovery.  0 = Disables the clock loss protection feature.  1 = Enables the clock loss protection feature.  Note: This bit needs to be enabled in order to detect the clock closs detection interrupt status (address: 0xnB00, bit 5)                                                        |

| 3:2 | Reserved                      | R/W  | 00      | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

## TABLE 2: CLOCK SELECT REGISTER(CSR)

HEX ADDRESS: 0xn100

| Віт | FUNCTION | Түре | DEFAULT |                         | DESCRIPTION-OPERATION                                                                                                                                |                                                                |

|-----|----------|------|---------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| 1:0 | CSS[1:0] | R/W  | 01      | These bits c and TxMSYI | ce Select elect the timing source for the Transr an also determine the direction of Tx NC in base rate operation mode (1.54 e (1.544MHz Clock Mode): | SERCLK, TxSYNC,                                                |

|     |          |      |         | CSS[1:0]                | TRANSMIT SOURCE FOR THE TRANSMIT T1 FRAMER BLOCK                                                                                                     | DIRECTION OF TXSERCLK                                          |

|     |          |      |         | 00/11                   | Loop Timing Mode The recovered line clock is chosen as the timing source.                                                                            | Output                                                         |

|     |          |      |         | 01                      | External Timing Mode The Transmit Serial Input Clock from the TxSERCLK_n input pin is chosen as the timing source.                                   | Input                                                          |

|     |          |      |         | 10                      | Internal Timing Mode The MCLK PLL is chosen as the timing source.                                                                                    | Output                                                         |

|     |          |      |         | depe<br>0xn1<br>Synd    | YNC/TxMSYNC can be programme<br>ending on the setting of SYNC INV bi<br>109, bit 4. Please see Register<br>chronization Mux Register (SMR - 0x       | t in Register Address<br>Description for the<br>n109) Table 8. |

|     |          |      |         |                         | igh-Speed or multiplexed modes, TxS<br>NC are all configured as INPUTS only                                                                          |                                                                |

HEX ADDRESS: 0XN101

## TABLE 3: LINE INTERFACE CONTROL REGISTER (LICR)

| Віт | Function  | Түре | DEFAULT | DESCRIPTION-OPERATION                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                     |  |  |

|-----|-----------|------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7   | FORCE_LOS | R/W  | 0       | This bit perm<br>(within the chequipment, a<br>0 - Configure                                                                                                                      | mit LOS (To the Line Side) its the user to configure the transmit direction circuitry nannel) to transmit the LOS pattern to the remote terminal is described below. Is the transmit direction circuitry to transmit "normal" traffic. Is the transmit direction circuitry to transmit the LOS                      |  |  |

| 6   | Reserved  | R/W  | 0       | Single Rail Mode This bit can only be set if the LIU Block is also set to single rail mode. See Register 0x0FE0, bit 7. 0 - Dual Rail 1 - Single Rail                             |                                                                                                                                                                                                                                                                                                                     |  |  |

| 5:4 | LB[1:0]   | R/W  | 00      | Framer Loopback Selection These bits are used to select any of the following loop-back modes for the framer section. For LIU loopback modes, see the LIU configuration registers. |                                                                                                                                                                                                                                                                                                                     |  |  |

|     |           |      |         | LB[1:0]                                                                                                                                                                           | TYPES OF LOOPBACK SELECTED                                                                                                                                                                                                                                                                                          |  |  |

|     |           |      |         | 00                                                                                                                                                                                | Normal Mode (No LoopBack)                                                                                                                                                                                                                                                                                           |  |  |

|     |           |      |         | 01                                                                                                                                                                                | Framer Local LoopBack: When framer local loopback is enabled, the transmit PCM input data is looped back to the receive PCM output data. The receive input data at RTIP/RRING is ignored while an All Ones Signal is transmitted out to the line interface.                                                         |  |  |

|     |           |      |         | 10                                                                                                                                                                                | Framer Far-End (Remote) Line LoopBack: When framer remote loopback is enabled, the digital data enters the framer interface, however does not enter the framing blocks. The receive digital data from the LIU is allowed to pass through the LIU Decoder/ Encoder circuitry before returning to the line interface. |  |  |

|     |           |      |         | 11                                                                                                                                                                                | Framer Payload LoopBack: When framer payload loopback is enabled, the raw data within the receive time slots are looped back to the transmit framer block where the data is re-framed according to the transmit timing.                                                                                             |  |  |

| 3:2 | Reserved  | R/W  | 0       | Reserved                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                     |  |  |

### TABLE 3: LINE INTERFACE CONTROL REGISTER (LICR)

HEX ADDRESS: 0XN101

| Віт | FUNCTION        | Түре | DEFAULT | Description-Operation                                                    |

|-----|-----------------|------|---------|--------------------------------------------------------------------------|

| 1   | Encode B8ZS     | R/W  | 0       | Encode AMI or B8ZS/HDB3 Line Code Select                                 |

|     |                 |      |         | This bit enables or disables the B8ZS/HDB3 encoder on the transmit path. |

|     |                 |      |         | 0 = Enables the B8ZS encoder.                                            |

|     |                 |      |         | 1 = Disables the B8ZS encoder.                                           |

|     |                 |      |         | Note: When B8ZS encoder is disabled, AMI line code is used.              |

| 0   | Decode AMI/B8ZS | R/W  | 0       | Decode AMI or B8ZS/HDB3 Line Code Select                                 |

|     |                 |      |         | This bit enables or disables the B8ZS/HDB3 decoder on the receive path.  |

|     |                 |      |         | 0 = Enables the B8ZS decoder.                                            |

|     |                 |      |         | 1 = Disables the B8ZS decoder.                                           |

|     |                 |      |         | NOTE: When B8ZS decoder is disabled, AMI line code is received.          |

## TABLE 4: FRAMING SELECT REGISTER (FSR)

| Віт | FUNCTION                                     | Түре | DEFAULT | DESCRIPTION-OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|----------------------------------------------|------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Signaling update on<br>Superframe Boundaries | R/W  | 0       | Enable Robbed-Bit Signaling Update on Superframe Boundary on Both Transmit and Receive Direction  This bit enables or disables robbed-bit signaling update on the superframe boundary for both the transmit and receive side of the framer.  On the Receive Side:  If signaling update is enabled, signaling data on the receive side (RxSIG pin and Signaling Array Register - RSAR) will be updated on the superframe boundary, otherwise, signaling data will be updated as soon as it is received.  On the Transmit Side:  If signaling update is enabled, any signaling data changes on the transmit side will be transmitted on the superframe boundary, otherwise, signaling data will be transmitted as soon as it is changed.  0 - Disables the signaling update feature for both transmit and receive.  1 - Enables the signaling update feature for both transmit and receive. |

| 6   | Force CRC Errors                             | R/W  | 0       | Force CRC Errors (To the Line Side) This bit permits the user to force the Transmit T1 Framer block to transmit CRC errors within the outbound T1 data-stream, as depicted below.  0 - Disables CRC error transmission on the outbound T1 stream.  1 - Enables CRC error transmission on the outbound T1 stream.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5   | J1_MODE                                      | R/W  | 0       | <ul> <li>J1 Mode This bit is used to configure the device in J1 mode. Once the device is configured in J1 mode, the following two changes will happen: <ol> <li>CRC calculation is done in J1 format. The J1 CRC6 calculation is based on the actual values of all 4632 bits in a T1 multiframe including Fe bits instead of assuming all Fe bits to be a one in T1 format.</li> <li>Receive and Transmit Yellow Alarm signal format is interpreted per the J1 standard. (J1-SF or J1-ESF)</li> <li>Configures the device in T1 mode. (Default)</li> <li>Configures the device in J1 mode.</li> </ol> </li> <li>Note: Users can select between J1-SF or J1-ESF by setting this bit and the T1 Framing Mode Select Bits[2:0] (Bits 2-0 within this register).</li> </ul>                                                                                                                   |

| 4   | ONEONLY                                      | R/W  | 0       | Allow Only One Sync Candidate This bit is used to specify one of the synchronization criteria that the Receive T1 Framer block employs.  0 - Allows the Receive T1 Framer to select any one of the winners in the matching process when there are two or more valid synchronization patterns appear in the required time frame.  1 - Allows the Receive T1 Framer to declare success of match when there is only one candidate left in the required time frame.                                                                                                                                                                                                                                                                                                                                                                                                                           |

TABLE 4: FRAMING SELECT REGISTER (FSR)

| HEV | ADDRESS: | 0vn107     |

|-----|----------|------------|

| ПЕХ | AUUKESS: | UXII I U / |

| Віт | FUNCTION | Түре | DEFAULT                                                                                                                                                                                                                                                                                                                                                                       |                | DESC     | RIPTION-C | PERATIO                                               | N                                            |     |

|-----|----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------|-----------|-------------------------------------------------------|----------------------------------------------|-----|

| 3   | FASTSYNC | R/W  | This bit is used to specify one of the synchronization criteria to Receive T1 Framer block employs. If this "Faster Sync Algorienabled, the Receive T1 Framer Block will declare synchroniearlier. The table below specifies the number of consecutive with correct F-bits that the T1 Receive framer must receive in to declare "SYNC" when FASTSYNC is enabled or disabled. |                |          |           | Algorithm" is chronization utive frames eive in order |                                              |     |

|     |          |      |                                                                                                                                                                                                                                                                                                                                                                               |                | Framing  |           | stSync<br>= 0                                         | FastS                                        | .   |

|     |          |      |                                                                                                                                                                                                                                                                                                                                                                               |                | ESF      |           | 96                                                    | 48                                           | 3   |

|     |          |      |                                                                                                                                                                                                                                                                                                                                                                               |                | SF       |           | 48                                                    | 24                                           | ļ.  |

|     |          |      |                                                                                                                                                                                                                                                                                                                                                                               |                | N        |           | 48                                                    | 24                                           | 1   |

|     |          |      |                                                                                                                                                                                                                                                                                                                                                                               |                | SLC ® 96 |           | 48                                                    | 24                                           | l . |

|     |          |      |                                                                                                                                                                                                                                                                                                                                                                               | 0 - Disables F |          |           |                                                       |                                              |     |

| 2-0 | FSI[2:0] | R/W  |                                                                                                                                                                                                                                                                                                                                                                               |                |          |           | able show configuri                                   | s the five dif-<br>ng these<br>e the Receive |     |

|     |          |      |                                                                                                                                                                                                                                                                                                                                                                               |                | Framing  | FS[2]     | FS[1]                                                 | FS[0]                                        |     |

|     |          |      |                                                                                                                                                                                                                                                                                                                                                                               |                | ESF      | 0         | Х                                                     | Х                                            |     |

|     |          |      |                                                                                                                                                                                                                                                                                                                                                                               |                | SF       | 1         | 0                                                     | 1                                            |     |

|     |          |      |                                                                                                                                                                                                                                                                                                                                                                               |                | N        | 1         | 1                                                     | 0                                            |     |

|     |          |      |                                                                                                                                                                                                                                                                                                                                                                               |                | T1DM     | 1         | 1                                                     | 1                                            |     |

|     |          |      |                                                                                                                                                                                                                                                                                                                                                                               |                | SLC®96   | 1         | 0                                                     | 0                                            |     |

## TABLE 5: ALARM GENERATION REGISTER (AGR)

| Віт | Function                             | Түре | DEFAULT | DESCRIPTION-OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|--------------------------------------|------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Yellow Alarm -<br>One Second<br>Rule | R/W  | O O     | <ul> <li>One-Second Yellow Alarm Rule Enforcement This bit is used to enforce the one-second yellow alarm rule according to the yellow alarm (RAI) transmission duration per the ANSI standards. </li> <li>If the one second alarm rule is enforced, the following will happen: <ol> <li>RAI will be transmitted for at least one second for both ESF and SF.</li> <li>There must be a minimum of one second delay between termination of the first RAI and the initiation of a subsequent RAI.</li> <li>ALARM_ENB bit (see description of bit 6 of this register) controls the duration of RAI.</li> <li>YEL[0] &amp; YEL[1] (see description of bits 5-4 of this register) controls the format of RAI.</li> </ol> </li> <li>If the one second alarm rule is NOT enforced, the following will happen: <ol> <li>RAI will be transmitted for at least one second for ESF and SF.</li> <li>Minimum one second delay between termination of the first RAI and the initiation of the subsequent RAI is NOT enforced.</li> <li>YEL[0] and YEL[1] bits (see description of bits 5-4 of this register) are used to control the duration AND the format of RAI transmission.</li> <li>The one-second yellow alarm rule is NOT enforced.</li> </ol> </li> </ul> |

|     |                                      |      |         | <ol> <li>The one-second yellow alarm rule is enforced.</li> <li>NOTE: When setting this bit to '0', yellow alarm transmission will be backward compatible with the XRT86L38 device. XRT86L38 does not support the one-second yellow alarm rule.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 6   | ALARM_ENB                            | R/W  | 0       | Yellow Alarm Transmission Enable This bit is used to control the duration of yellow alarm (RAI) when the one-second yellow alarm rule is enforced (bit 7 of this register set to'1'). When the one-second yellow alarm rule is not enforced (bit 7 of this register set to'0'), the duration of the RAI is controlled by the YEL[0] and YEL[1] bits (bits 5-4 of this register).  If the one-second alarm rule is enforced:  0 - Stop the transmission of yellow alarm (see description of bits 5-4).  1 - Start the transmission of yellow alarm (see description of bits 5-4).  NOTE: This bit has no function if the one second alarm rule is not enforced.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| TABL | E 5: ALARM G | ENERA | TION REG | ISTER (AGR                                    | HEX ADDRESS: 0xn108                                                                                                                                                                                                                                                  |  |  |

|------|--------------|-------|----------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|