Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# XUF216-512-FB236 Datasheet

2017/02/02 XMOS © 2017, All Rights Reserved

Document Number: X007545,

# **Table of Contents**

| 1    | xCORE Multicore Microcontrollers      | 2  |

|------|---------------------------------------|----|

| 2    | XUF216-512-FB236 Features             | 4  |

| 3    | Pin Configuration                     | 5  |

| 4    | Signal Description                    |    |

| 5    | Example Application Diagram           |    |

| 6    | Product Overview                      |    |

| 7    | PLL                                   |    |

| 8    | Boot Procedure                        |    |

| 9    | Memory                                | 17 |

| 10   | USB PHY                               |    |

| 11   | JTAG                                  | 20 |

| 12   | Board Integration                     | 21 |

| 13   | DC and Switching Characteristics      |    |

| 14   | Package Information                   |    |

| 15   | Ordering Information                  |    |

| Appe | endices                               |    |

| Α    | Configuration of the XUF216-512-FB236 |    |

| В    | Processor Status Configuration        | 35 |

| C    | Tile Configuration                    |    |

| D    | Node Configuration                    | 54 |

| E    | USB Node Configuration                |    |

| F    | USB PHY Configuration                 |    |

| G    | JTAG, xSCOPE and Debugging            | 71 |

| H    | Schematics Design Check List          | 73 |

| I    | PCB Layout Design Check List          | 75 |

| J    | Associated Design Documentation       |    |

| K    | Related Documentation                 | 76 |

| L    | Revision History                      | 77 |

#### TO OUR VALUED CUSTOMERS

It is our intention to provide you with accurate and comprehensive documentation for the hardware and software components used in this product. To subscribe to receive updates, visit <a href="http://www.xmos.com/">http://www.xmos.com/</a>.

XMOS Ltd. is the owner or licensee of the information in this document and is providing it to you "AS IS" with no warranty of any kind, express or implied and shall have no liability in relation to its use. XMOS Ltd. makes no representation that the information, or any particular implementation thereof, is or will be free from any claims of infringement and again, shall have no liability in relation to any such claims.

XMOS and the XMOS logo are registered trademarks of XMOS Ltd in the United Kingdom and other countries, and may not be used without written permission. Company and product names mentioned in this document are the trademarks or registered trademarks of their respective owners.

# 1 xCORE Multicore Microcontrollers

The xCORE200 Series is a comprehensive range of 32-bit multicore microcontrollers that brings the low latency and timing determinism of the xCORE architecture to mainstream embedded applications. Unlike conventional microcontrollers, xCORE multicore microcontrollers execute multiple real-time tasks simultaneously and communicate between tasks using a high speed network. Because xCORE multicore microcontrollers are completely deterministic, you can write software to implement functions that traditionally require dedicated hardware.

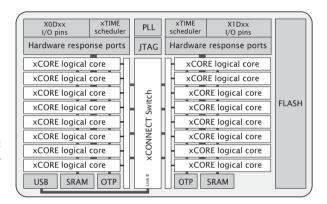

Figure 1: XUF216-512-FB236 block diagram

Key features of the XUF216-512-FB236 include:

- ► **Tiles**: Devices consist of one or more xCORE tiles. Each tile contains between five and eight 32-bit xCOREs with highly integrated I/O and on-chip memory.

- ▶ Logical cores Each logical core can execute tasks such as computational code, DSP code, control software (including logic decisions and executing a state machine) or software that handles I/O. Section 6.1

- ▶ xTIME scheduler The xTIME scheduler performs functions similar to an RTOS, in hardware. It services and synchronizes events in a core, so there is no requirement for interrupt handler routines. The xTIME scheduler triggers cores on events generated by hardware resources such as the I/O pins, communication channels and timers. Once triggered, a core runs independently and concurrently to other cores, until it pauses to wait for more events. Section 6.2

- ▶ Channels and channel ends Tasks running on logical cores communicate using channels formed between two channel ends. Data can be passed synchronously or asynchronously between the channel ends assigned to the communicating tasks. Section 6.5

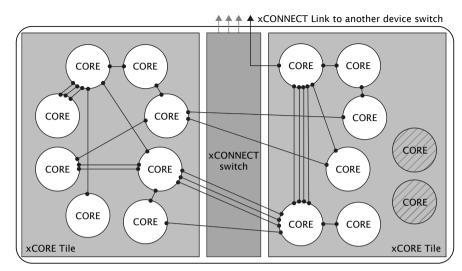

- ➤ xCONNECT Switch and Links Between tiles, channel communications are implemented over a high performance network of xCONNECT Links and routed through a hardware xCONNECT Switch. Section 6.6

- ▶ **Ports** The I/O pins are connected to the processing cores by Hardware Response ports. The port logic can drive its pins high and low, or it can sample the value on its pins optionally waiting for a particular condition. Section 6.3

- ► Clock blocks xCORE devices include a set of programmable clock blocks that can be used to govern the rate at which ports execute. Section 6.4

- ▶ Memory Each xCORE Tile integrates a bank of SRAM for instructions and data, and a block of one-time programmable (OTP) memory that can be configured for system wide security features. Section 9

- ▶ PLL The PLL is used to create a high-speed processor clock given a low speed external oscillator. Section 7

- ▶ **USB** The USB PHY provides High-Speed and Full-Speed, device, host, and on-thego functionality. Data is communicated through ports on the digital node. A library is provided to implement USB device functionality. Section 10

- ▶ Flash The device has a built-in 2MBflash. Section 8

- ▶ JTAG The JTAG module can be used for loading programs, boundary scan testing, in-circuit source-level debugging and programming the OTP memory. Section 11

#### 1.1 Software

Devices are programmed using C, C++ or xC (C with multicore extensions). XMOS provides tested and proven software libraries, which allow you to quickly add interface and processor functionality such as USB, Ethernet, PWM, graphics driver, and audio EO to your applications.

#### 1.2 xTIMEcomposer Studio

The xTIMEcomposer Studio development environment provides all the tools you need to write and debug your programs, profile your application, and write images into flash memory or OTP memory on the device. Because xCORE devices operate deterministically, they can be simulated like hardware within xTIMEcomposer: uniquely in the embedded world, xTIMEcomposer Studio therefore includes a static timing analyzer, cycle-accurate simulator, and high-speed in-circuit instrumentation.

xTIMEcomposer can be driven from either a graphical development environment, or the command line. The tools are supported on Windows, Linux and MacOS X and available at no cost from xmos.com/downloads. Information on using the tools is provided in the xTIMEcomposer User Guide, X3766.

#### 2 XUF216-512-FB236 Features

#### ► Multicore Microcontroller with Advanced Multi-Core RISC Architecture

- 16 real-time logical cores on 2 xCORE tiles

- Cores share up to 1000 MIPS

- Up to 2000 MIPS in dual issue mode

- Each logical core has:

- Guaranteed throughput of between 1/5 and 1/8 of tile MIPS

- 16x32bit dedicated registers

- 167 high-density 16/32-bit instructions

- All have single clock-cycle execution (except for divide)

- 32x32→64-bit MAC instructions for DSP, arithmetic and user-definable cryptographic functions

#### ▶ USB PHY, fully compliant with USB 2.0 specification

#### ▶ Programmable I/O

- 128 general-purpose I/O pins, configurable as input or output

- Up to 32 x 1bit port, 12 x 4bit port, 8 x 8bit port, 4 x 16bit port, 2 x 32bit port

- 8 xCONNECT links

- Port sampling rates of up to 60 MHz with respect to an external clock

- 64 channel endss (32 per tile) for communication with other cores, on or off-chip

#### ▶ Memory

- 512KB internal single-cycle SRAM (max 256KB per tile) for code and data storage

- 16KB internal OTP (max 8KB per tile) for application boot code

- 2MB internal flash for application code and overlays

#### ▶ Hardware resources

- 12 clock blocks (6 per tile)

- 20 timers (10 per tile)

- 8 locks (4 per tile)

#### ▶ JTAG Module for On-Chip Debug

#### ▶ Security Features

- Programming lock disables debug and prevents read-back of memory contents

- AES bootloader ensures secrecy of IP held on external flash memory

#### ► Ambient Temperature Range

- Commercial qualification: 0°C to 70°C

- Industrial qualification: -40 °C to 85 °C

#### ▶ Speed Grade

20: 1000 MIPS

# ▶ Power Consumption

570 mA (typical)

# ▶ 236-pin FBGA package 0.5 mm pitch

# 3 Pin Configuration

|   | 1                                                    | 2                                                    | 3                                                    | 4     | 5           | 6          | 7     | 8             | 9             | 10          | 11            | 12          | 13           | 14           | 15      | 16    | 17                                                   | 18                                                   | 19                                                   |

|---|------------------------------------------------------|------------------------------------------------------|------------------------------------------------------|-------|-------------|------------|-------|---------------|---------------|-------------|---------------|-------------|--------------|--------------|---------|-------|------------------------------------------------------|------------------------------------------------------|------------------------------------------------------|

| А | GND                                                  | VDDIOL                                               | VDDIOL                                               |       | TCK         | CLK        |       | X1D31         | X1D29         |             | X1D41         | OTP_<br>VCC |              | NC           | MODE[0] |       | X0D29                                                | VDDIOR                                               | GND                                                  |

| В | X0D36                                                | VDDIOL                                               | VDDIOL                                               | TDO   | TMS         | TRST_<br>N | X1D33 | X1D32         | X1D28         | X1D26       | X1D42         | OTP_<br>VCC | NC           | NC           | MODE[1] | X0D33 | X0D32                                                | VDDIOR                                               | VDDIOR                                               |

| С | X0D37<br>X <sub>0</sub> L <sub>0</sub> <sup>M</sup>  | X0D38<br>X <sub>0</sub> L <sub>0</sub> <sup>0</sup>  | VDDIOL                                               | TDI   | DEBUG_<br>N | RST_N      | X1D10 | X1D11         | X1D30         | X1D27       | X1D43         | X1D40       | NC           | NC           | X0D31   | X0D30 | X0D28                                                | X0D26<br>X <sub>0</sub> L <sup>c3</sup> <sub>7</sub> | X0D27<br>X <sub>0</sub> L <sub>7</sub> <sup>o4</sup> |

| D |                                                      | X0D39<br>X <sub>0</sub> L <sub>0</sub> <sup>2</sup>  | X0D40<br>X <sub>0</sub> L <sub>0</sub> <sup>11</sup> |       |             |            |       |               |               |             |               |             |              |              |         |       | X0D34<br>X <sub>0</sub> L <sub>7</sub> <sup>o1</sup> | X0D35<br>X <sub>0</sub> L <sub>7</sub> <sup>2</sup>  |                                                      |

| Е | X0D43<br>X <sub>0</sub> L <sub>0</sub> 1             | X0D42<br>X₀L₀⁰                                       | X0D41<br>X <sub>0</sub> L <sub>0</sub> <sup>10</sup> |       |             |            |       |               |               |             |               |             |              |              |         |       | X0D25<br>X <sub>3</sub> L <sub>7</sub> <sup>00</sup> | X0D24<br>X <sub>0</sub> L <sub>7</sub> <sup>0</sup>  | X1D01<br>X <sub>0</sub> L <sub>7</sub> <sup>1</sup>  |

| F | X1D34<br>X <sub>0</sub> L <sub>0</sub> <sup>22</sup> | X1D35<br>X <sub>0</sub> L <sub>0</sub> <sup>03</sup> | X1D36<br>X <sub>0</sub> L <sub>0</sub> <sup>st</sup> |       |             |            | NC    | VDD           | VDD           | VDDIOT      | VDD           | VDD         | PLL_<br>AVDD | PLL_<br>AGND |         |       | X1D08<br>X <sub>3</sub> L <sub>7</sub> <sup>4</sup>  | X1D09<br>X <sub>0</sub> L <sub>7</sub> <sup>0</sup>  | X1D00<br>X <sub>0</sub> L <sub>7</sub> <sup>2</sup>  |

| G |                                                      | X1D49<br>X <sub>0</sub> L <sub>1</sub> <sup>18</sup> | X1D50<br>X <sub>0</sub> L <sub>1</sub>               |       |             | VDD        |       | GND           |               | GND         |               | GND         |              | VDD          |         |       | X0D69<br>X <sub>3</sub> L <sub>6</sub> <sup>03</sup> | X0D70<br>X <sub>0</sub> L <sup>pl</sup> <sub>6</sub> |                                                      |

| н | X1D53<br>X <sub>2</sub> L <sub>1</sub> <sup>0</sup>  | X1D52<br>X <sub>3</sub> L <sub>1</sub>               | X1D51<br>X <sub>3</sub> L <sub>1</sub> <sup>22</sup> |       |             | VDD        | GND   | GND           | GND           | GND         | GND           | GND         | GND          | VDD          |         |       | X0D68<br>X <sub>0</sub> L <sub>0</sub> <sup>02</sup> | X0D67<br>X <sub>0</sub> L <sup>ol</sup> <sub>6</sub> | X0D66<br>X <sub>0</sub> L <sub>6</sub> <sup>00</sup> |

| J | X1D54<br>X <sub>3</sub> L <sub>1</sub> <sup>0</sup>  | X1D55<br>X <sub>0</sub> L <sup>ol</sup>              | X1D56<br>X <sub>3</sub> L <sub>1</sub> <sup>22</sup> |       |             | VDD        |       | GND           |               | GND         |               | GND         |              | VDD          |         |       | X0D63<br>X <sub>0</sub> L <sub>0</sub> <sup>2</sup>  | X0D64<br>X <sub>0</sub> L <sup>1</sup> <sub>6</sub>  | X0D65<br>X <sub>0</sub> L <sub>6</sub> <sup>0</sup>  |

| К |                                                      | X1D58<br>X <sub>0</sub> L <sub>1</sub> <sup>ol</sup> | X1D57<br>X <sub>3</sub> L <sub>1</sub> <sup>23</sup> |       |             | VDD        | GND   | GND           | GND           | GND         | GND           | GND         | GND          | VDD          |         |       | X0D62<br>X <sub>0</sub> L <sub>0</sub> <sup>3</sup>  | X0D61<br>X <sub>0</sub> L <sup>M</sup> <sub>6</sub>  |                                                      |

| L | X1D63<br>X <sub>0</sub> L <sup>2</sup> <sub>2</sub>  | X1D62<br>X <sub>0</sub> L <sub>2</sub> <sup>0</sup>  | X1D61<br>X <sub>3</sub> L <sup>14</sup> <sub>2</sub> |       |             | VDD        |       | GND           |               | GND         |               | GND         |              | VDD          |         |       | X0D58<br>X <sub>0</sub> L <sup>od</sup> <sub>5</sub> | X0D57<br>X <sub>0</sub> L <sup>3</sup>               | X0D56<br>X <sub>0</sub> L <sub>5</sub> <sup>02</sup> |

| М | X1D64<br>X <sub>0</sub> L <sup>1</sup> <sub>2</sub>  | X1D65<br>X <sub>0</sub> L <sub>2</sub> <sup>0</sup>  | X1D66<br>X <sub>0</sub> L <sub>2</sub> <sup>0</sup>  |       |             | VDD        | GND   | GND           | GND           | GND         | GND           | GND         | GND          | VDD          |         |       | X0D53<br>X <sub>3</sub> L <sup>0</sup> <sub>3</sub>  | X0D54<br>X <sub>0</sub> L <sub>3</sub> <sup>0</sup>  | X0D55<br>X <sub>0</sub> L <sub>3</sub> <sup>o1</sup> |

| N |                                                      | X1D67<br>X <sub>0</sub> L <sub>2</sub> <sup>o1</sup> | X1D68<br>X <sub>3</sub> L <sub>2</sub> <sup>22</sup> |       |             | VDD        |       | GND           |               | GND         |               | GND         |              | VDD          |         |       | X0D51<br>X <sub>3</sub> L <sub>3</sub> <sup>2</sup>  | X0D52<br>X <sub>0</sub> L <sup>1</sup> <sub>3</sub>  |                                                      |

| Р | X1D70<br>X <sub>0</sub> L <sub>2</sub> <sup>st</sup> | X1D69<br>X <sub>0</sub> L <sub>2</sub> <sup>0</sup>  | X1D37<br>X <sub>0</sub> L <sub>3</sub> <sup>H</sup>  |       |             | VDD        | VDD   | VDD           | USB_<br>VDD   | USB_<br>VDD | VDD           | VDD         | VDD          | NC           |         |       | X1D07<br>X <sub>3</sub> L <sub>4</sub> <sup>o4</sup> | X0D50<br>X <sub>0</sub> L <sub>3</sub> <sup>3</sup>  | X0D49<br>X <sub>0</sub> L <sup>H</sup> <sub>5</sub>  |

| R | X1D38<br>X <sub>0</sub> L <sub>3</sub> <sup>0</sup>  | X1D39<br>X <sub>0</sub> L <sub>3</sub> <sup>2</sup>  | X1D17<br>X <sub>0</sub> L <sub>3</sub> <sup>0</sup>  |       |             |            |       |               |               |             |               |             |              |              |         |       | X1D03<br>X <sub>3</sub> L <sub>4</sub> <sup>00</sup> | X1D05<br>X <sub>0</sub> L <sup>cd</sup> <sub>4</sub> | X1D06<br>X <sub>0</sub> L <sub>4</sub> <sup>c3</sup> |

| Т |                                                      | X1D16<br>X <sub>0</sub> L <sub>3</sub> <sup>1</sup>  | X1D18<br>X <sub>3</sub> L <sub>3</sub> <sup>0</sup>  |       |             |            |       |               |               |             |               |             |              |              |         |       | X1D02<br>X <sub>3</sub> L <sub>4</sub> <sup>0</sup>  | X1D04<br>X <sub>0</sub> L <sub>4</sub> <sup>o1</sup> |                                                      |

| U | X0D10<br>X <sub>0</sub> L <sub>3</sub> <sup>c0</sup> | X0D01<br>X <sub>0</sub> L <sub>3</sub> <sup>22</sup> | X1D19<br>X <sub>0</sub> L <sup>e1</sup> <sub>3</sub> | X0D00 | X0D11       | X0D07      | X1D12 | USB_<br>VDD33 | USB_<br>VBUS  | USB_<br>ID  | USB_<br>VSSAC | NC          | X1D24        | X0D22        | X0D13   | X0D23 | X0D19<br>X <sub>3</sub> L <sup>0</sup> <sub>4</sub>  | X0D18<br>X <sub>0</sub> L <sup>2</sup> <sub>4</sub>  | X0D17<br>X <sub>0</sub> L <sub>4</sub> <sup>0</sup>  |

| V | X1D22<br>X <sub>0</sub> L <sub>3</sub> <sup>04</sup> | VDDIOL                                               | VDDIOL                                               | X0D04 | X0D06       | X0D03      | X0D08 | X0D09         | USB_<br>DM    | USB_<br>DP  | X1D21         | X1D14       | X1D25        | X0D21        | X0D14   | X0D12 | VDDIOR                                               | VDDIOR                                               | X0D16<br>X <sub>0</sub> L <sup>H</sup> <sub>4</sub>  |

| w | GND                                                  | VDDIOL                                               | X1D23                                                |       | X0D05       | X0D02      |       | X1D13         | USB_<br>RTUNE |             | X1D20         | X1D15       |              | X0D20        | X0D15   |       | VDDIOR                                               | VDDIOR                                               | GND                                                  |

# 4 Signal Description

This section lists the signals and I/O pins available on the XUF216-512-FB236. The device provides a combination of 1 bit, 4bit, 8bit and 16bit ports, as well as wider ports that are fully or partially (gray) bonded out. All pins of a port provide either output or input, but signals in different directions cannot be mapped onto the same port.

Pins may have one or more of the following properties:

- ▶ PD/PU: The IO pin has a weak pull-down or pull-up resistor. The resistor is enabled during and after reset. Enabling a link or port that uses the pin disables the resistor. Thereafter, the resistor can be enabled or disabled under software control. The resistor is designed to ensure defined logic input state for unconnected pins. It should not be used to pull external circuitry. Note that the resistors are highly non-linear and only a maximum pull current is specified in Section 13.2.

- ▶ ST: The IO pin has a Schmitt Trigger on its input.

- IOL/IOT/IOR: The IO pin is powered from VDDIOL, VDDIOT, and VDDIOR respectively

|           | Power pins (11)           |      |            |

|-----------|---------------------------|------|------------|

| Signal    | Function                  | Type | Properties |

| GND       | Digital ground            | GND  |            |

| OTP_VCC   | OTP power supply          | PWR  |            |

| PLL_AGND  | Analog ground for PLL     | PWR  |            |

| PLL_AVDD  | Analog PLL power          | PWR  |            |

| USB_VDD   | Digital tile power        | PWR  |            |

| USB_VDD33 | USB Analog power          | PWR  |            |

| USB_VSSAC | USB analog ground         | GND  |            |

| VDD       | Digital tile power        | PWR  |            |

| VDDIOL    | Digital I/O power (left)  | PWR  |            |

| VDDIOR    | Digital I/O power (right) | PWR  |            |

| VDDIOT    | Digital I/O power (top)   | PWR  |            |

|        | JTAG pins (6)      |        |             |  |  |  |  |  |  |  |

|--------|--------------------|--------|-------------|--|--|--|--|--|--|--|

| Signal | Function           | Type   | Properties  |  |  |  |  |  |  |  |

| RST_N  | Global reset input | Input  | IOL, PU, ST |  |  |  |  |  |  |  |

| TCK    | Test clock         | Input  | IOL, PD, ST |  |  |  |  |  |  |  |

| TDI    | Test data input    | Input  | IOL, PU     |  |  |  |  |  |  |  |

| TDO    | Test data output   | Output | IOL, PD     |  |  |  |  |  |  |  |

| TMS    | Test mode select   | Input  | IOL, PU     |  |  |  |  |  |  |  |

| TRST_N | Test reset input   | Input  | IOL, PU, ST |  |  |  |  |  |  |  |

| I/O pins (128) |                                               |                  |                 |                 |                   |                   |      |            |  |  |  |

|----------------|-----------------------------------------------|------------------|-----------------|-----------------|-------------------|-------------------|------|------------|--|--|--|

| Signal         | Function                                      |                  |                 |                 |                   |                   | Type | Properties |  |  |  |

| X0D00          |                                               | 1A <sup>0</sup>  |                 |                 |                   |                   | I/O  | IOL, PD    |  |  |  |

| X0D01          | X <sub>0</sub> L3 <sup>2</sup> <sub>out</sub> | 1 B <sup>0</sup> |                 |                 |                   |                   | 1/0— | IOL, PD    |  |  |  |

| X0D02          |                                               |                  | 4A <sup>0</sup> | 8A <sup>0</sup> | 16A <sup>0</sup>  | 32A <sup>20</sup> | I/O  | IOL, PD    |  |  |  |

| X0D03          |                                               |                  | 4A <sup>1</sup> | 8A <sup>1</sup> | 16A <sup>1</sup>  | 32A <sup>21</sup> | I/O  | IOL, PD    |  |  |  |

| X0D04          |                                               |                  | 4B <sup>0</sup> | 8A <sup>2</sup> | 16A <sup>2</sup>  | 32A <sup>22</sup> | 1/0— | IOL, PD    |  |  |  |

| X0D05          |                                               |                  | 4B <sup>1</sup> | 8A <sup>3</sup> | 16A <sup>3</sup>  | 32A <sup>23</sup> | 1/0— | IOL, PD    |  |  |  |

| X0D06          |                                               |                  | 4B <sup>2</sup> | 8A <sup>4</sup> | 16A <sup>4</sup>  | 32A <sup>24</sup> | 1/0- | IOL, PD    |  |  |  |

| X0D07          |                                               |                  | 4B <sup>3</sup> | 8A <sup>5</sup> | 16A <sup>5</sup>  | 32A <sup>25</sup> | 1/0- | IOL, PD    |  |  |  |

| X0D08          |                                               |                  | 4A <sup>2</sup> | 8A <sup>6</sup> | 16A <sup>6</sup>  | 32A <sup>26</sup> | I/O  | IOL, PD    |  |  |  |

| X0D09          |                                               |                  | 4A <sup>3</sup> | 8A <sup>7</sup> | 16A <sup>7</sup>  | 32A <sup>27</sup> | 1/0  | IOL, PD    |  |  |  |

| X0D10          | X <sub>0</sub> L3 <sup>3</sup> <sub>out</sub> | 1C <sup>0</sup>  |                 |                 |                   |                   | 1/0— | IOL, PD    |  |  |  |

| X0D11          |                                               | 1D <sup>0</sup>  |                 |                 |                   |                   | 1/0  | IOL, PD    |  |  |  |

| X0D12          |                                               | 1 E <sup>0</sup> |                 |                 |                   |                   | 1/0  | IOR, PD    |  |  |  |

| X0D13          |                                               | 1F <sup>0</sup>  |                 |                 |                   |                   | 1/0  | IOR, PD    |  |  |  |

| X0D14          |                                               |                  | 4C <sup>0</sup> | 8B <sup>0</sup> | 16A <sup>8</sup>  | 32A <sup>28</sup> | 1/0  | IOR, PD    |  |  |  |

| X0D15          |                                               |                  | 4C <sup>1</sup> | 8B <sup>1</sup> | 16A <sup>9</sup>  | 32A <sup>29</sup> | I/O  | IOR, PD    |  |  |  |

| X0D16          | X <sub>0</sub> L4 <sup>4</sup> <sub>in</sub>  |                  | 4D <sup>0</sup> | 8B <sup>2</sup> | 16A <sup>10</sup> |                   | 1/0  | IOR, PD    |  |  |  |

| X0D17          | X <sub>0</sub> L4 <sup>3</sup> <sub>in</sub>  |                  | 4D <sup>1</sup> | 8B <sup>3</sup> | 16A <sup>11</sup> |                   | 1/0  | IOR, PD    |  |  |  |

| X0D18          | X <sub>0</sub> L4 <sup>2</sup> <sub>in</sub>  |                  | 4D <sup>2</sup> | 8B <sup>4</sup> | 16A <sup>12</sup> |                   | I/O  | IOR, PD    |  |  |  |

| X0D19          | X <sub>0</sub> L4 <sup>1</sup> <sub>in</sub>  |                  | 4D <sup>3</sup> | 8B <sup>5</sup> | 16A <sup>13</sup> |                   | 1/0  | IOR, PD    |  |  |  |

| X0D20          |                                               |                  | 4C <sup>2</sup> | 8B <sup>6</sup> | 16A <sup>14</sup> | 32A <sup>30</sup> | I/O  | IOR, PD    |  |  |  |

| X0D21          |                                               |                  | 4C <sup>3</sup> | 8B <sup>7</sup> | 16A <sup>15</sup> |                   | I/O  | IOR, PD    |  |  |  |

| X0D22          |                                               | 1G <sup>0</sup>  |                 |                 |                   |                   | 1/0  | IOR, PD    |  |  |  |

| X0D23          |                                               | 1H <sup>0</sup>  |                 |                 |                   |                   | 1/0  | IOR, PD    |  |  |  |

| X0D24          | X <sub>0</sub> L7 <sup>0</sup> <sub>in</sub>  | 110              |                 |                 |                   |                   | 1/0  | IOR, PD    |  |  |  |

| X0D25          | X <sub>0</sub> L7 <sup>0</sup> <sub>out</sub> | 1J <sup>0</sup>  |                 |                 |                   |                   | 1/0  | IOR, PD    |  |  |  |

| X0D26          | X <sub>0</sub> L7 <sup>3</sup> <sub>out</sub> |                  | 4E <sup>0</sup> | 8C <sup>0</sup> | 16B <sup>0</sup>  |                   | 1/0  | IOR, PD    |  |  |  |

| X0D27          | X <sub>0</sub> L7 <sup>4</sup> <sub>out</sub> |                  | 4E <sup>1</sup> | 8C <sup>1</sup> | 16B <sup>1</sup>  |                   | 1/0  | IOR, PD    |  |  |  |

| X0D28          |                                               |                  | 4F <sup>0</sup> | 8C <sup>2</sup> | 16B <sup>2</sup>  |                   | 1/0  | IOR, PD    |  |  |  |

| X0D29          |                                               |                  | 4F <sup>1</sup> | 8C <sup>3</sup> | 16B <sup>3</sup>  |                   | 1/0  | IOR, PD    |  |  |  |

| X0D30          |                                               |                  | 4F <sup>2</sup> | 8C <sup>4</sup> | 16B <sup>4</sup>  |                   | 1/0  | IOR, PD    |  |  |  |

| X0D31          |                                               |                  | 4F <sup>3</sup> | 8C <sup>5</sup> | 16B <sup>5</sup>  |                   | 1/0  | IOR, PD    |  |  |  |

| X0D32          |                                               |                  | 4E <sup>2</sup> | 8C <sup>6</sup> | 16B <sup>6</sup>  |                   | 1/0  | IOR, PD    |  |  |  |

| X0D33          |                                               |                  | 4E <sup>3</sup> | 8C <sup>7</sup> | 16B <sup>7</sup>  |                   | 1/0  | IOR, PD    |  |  |  |

| X0D34          | X <sub>0</sub> L7 <sup>1</sup> <sub>out</sub> | 1K <sup>0</sup>  |                 |                 |                   |                   | 1/0  | IOR, PD    |  |  |  |

| X0D35          | X <sub>0</sub> L7 <sup>2</sup> <sub>out</sub> | 1L <sup>0</sup>  |                 |                 |                   |                   | 1/0  | IOR, PD    |  |  |  |

| X0D36          |                                               | 1M <sup>0</sup>  |                 | 8D <sup>0</sup> | 16B <sup>8</sup>  |                   | 1/0  | IOL, PD    |  |  |  |

| X0D37          | X <sub>0</sub> L0 <sup>4</sup> <sub>in</sub>  | 1N <sup>0</sup>  |                 | 8D1             | 16B <sup>9</sup>  |                   | 1/0  | IOL, PD    |  |  |  |

| X0D38          | X <sub>0</sub> L0 <sup>3</sup> <sub>in</sub>  | 10 <sup>0</sup>  |                 | 8D <sup>2</sup> | 16B <sup>10</sup> |                   | 1/0  | IOL, PD    |  |  |  |

| X0D39          | X <sub>0</sub> L0 <sup>2</sup> <sub>in</sub>  | 1P <sup>0</sup>  |                 | 8D <sup>3</sup> | 16B <sup>11</sup> |                   | 1/0  | IOL, PD    |  |  |  |

| X0D40          | X <sub>0</sub> L0 <sup>1</sup> <sub>in</sub>  |                  |                 | 8D <sup>4</sup> | 16B <sup>12</sup> |                   | 1/0  | IOL, PD    |  |  |  |

(continued)

| Signal | Function                                      |                 |                 |                   |                   | Type | Properties |

|--------|-----------------------------------------------|-----------------|-----------------|-------------------|-------------------|------|------------|

| X0D41  | X <sub>0</sub> L0 <sup>0</sup> <sub>in</sub>  |                 | 8D <sup>5</sup> | 16B <sup>13</sup> |                   | 1/0  | IOL, PD    |

| X0D42  | X <sub>0</sub> L0 <sup>0</sup> <sub>out</sub> |                 | 8D <sup>6</sup> | 16B <sup>14</sup> |                   | 1/0  | IOL, PD    |

| X0D43  | X <sub>0</sub> L0 <sup>1</sup> <sub>out</sub> |                 | 8D <sup>7</sup> | 16B <sup>15</sup> |                   | 1/0  | IOL, PD    |

| X0D49  | X <sub>0</sub> L5 <sup>4</sup> <sub>in</sub>  |                 |                 |                   | 32A <sup>0</sup>  | 1/0  | IOR, PD    |

| X0D50  | X <sub>0</sub> L5 <sup>3</sup> <sub>in</sub>  |                 |                 |                   | 32A <sup>1</sup>  | 1/0  | IOR, PD    |

| X0D51  | X <sub>0</sub> L5 <sup>2</sup> <sub>in</sub>  |                 |                 |                   | 32A <sup>2</sup>  | 1/0  | IOR, PD    |

| X0D52  | X <sub>0</sub> L5 <sup>1</sup> <sub>in</sub>  |                 |                 |                   | 32A <sup>3</sup>  | 1/0  | IOR, PD    |

| X0D53  | X <sub>0</sub> L5 <sup>0</sup> <sub>in</sub>  |                 |                 |                   | 32A <sup>4</sup>  | I/O  | IOR, PD    |

| X0D54  | X <sub>0</sub> L5 <sup>0</sup> <sub>out</sub> |                 |                 |                   | 32A <sup>5</sup>  | I/O  | IOR, PD    |

| X0D55  | X <sub>0</sub> L5 <sup>1</sup> <sub>out</sub> |                 |                 |                   | 32A <sup>6</sup>  | I/O  | IOR, PD    |

| X0D56  | X <sub>0</sub> L5 <sup>2</sup> <sub>out</sub> |                 |                 |                   | 32A <sup>7</sup>  | I/O  | IOR, PD    |

| X0D57  | X <sub>0</sub> L5 <sup>3</sup> <sub>out</sub> |                 |                 |                   | 32A <sup>8</sup>  | I/O  | IOR, PD    |

| X0D58  | X <sub>0</sub> L5 <sup>4</sup> <sub>out</sub> |                 |                 |                   | 32A <sup>9</sup>  | I/O  | IOR, PD    |

| X0D61  | X <sub>0</sub> L6 <sup>4</sup> <sub>in</sub>  |                 |                 |                   | 32A <sup>10</sup> | I/O  | IOR, PD    |

| X0D62  | X <sub>0</sub> L6 <sup>3</sup> <sub>in</sub>  |                 |                 |                   | 32A <sup>11</sup> | I/O  | IOR, PD    |

| X0D63  | X <sub>0</sub> L6 <sup>2</sup> <sub>in</sub>  |                 |                 |                   | 32A <sup>12</sup> | I/O  | IOR, PD    |

| X0D64  | X <sub>0</sub> L6 <sup>1</sup> <sub>in</sub>  |                 |                 |                   | 32A <sup>13</sup> | I/O  | IOR, PD    |

| X0D65  | X <sub>0</sub> L6 <sup>0</sup> <sub>in</sub>  |                 |                 |                   | 32A <sup>14</sup> | I/O  | IOR, PD    |

| X0D66  | X <sub>0</sub> L6 <sup>0</sup> <sub>out</sub> |                 |                 |                   | 32A <sup>15</sup> | I/O  | IOR, PD    |

| X0D67  | X <sub>0</sub> L6 <sup>1</sup> <sub>out</sub> |                 |                 |                   | 32A <sup>16</sup> | I/O  | IOR, PD    |

| X0D68  | X <sub>0</sub> L6 <sup>2</sup> <sub>out</sub> |                 |                 |                   | 32A <sup>17</sup> | I/O  | IOR, PD    |

| X0D69  | X <sub>0</sub> L6 <sup>3</sup> <sub>out</sub> |                 |                 |                   | 32A <sup>18</sup> | I/O  | IOR, PD    |

| X0D70  | X <sub>0</sub> L6 <sup>4</sup> <sub>out</sub> |                 |                 |                   | 32A <sup>19</sup> | I/O  | IOR, PD    |

| X1D00  | $X_0L7_{in}^2$ $1A^0$                         |                 |                 |                   |                   | I/O  | IOR, PD    |

| X1D01  | $X_0L7_{in}^1$ 1B <sup>0</sup>                |                 |                 |                   |                   | I/O  | IOR, PD    |

| X1D02  | X <sub>0</sub> L4 <sup>0</sup> <sub>in</sub>  | 4A <sup>0</sup> | 8A <sup>0</sup> | 16A <sup>0</sup>  | 32A <sup>20</sup> | I/O  | IOR, PD    |

| X1D03  | X <sub>0</sub> L4 <sup>0</sup> <sub>out</sub> | 4A <sup>1</sup> | 8A <sup>1</sup> | 16A <sup>1</sup>  | 32A <sup>21</sup> | I/O  | IOR, PD    |

| X1D04  | X <sub>0</sub> L4 <sup>1</sup> <sub>out</sub> | 4B <sup>0</sup> | 8A <sup>2</sup> | 16A <sup>2</sup>  | 32A <sup>22</sup> | I/O  | IOR, PD    |

| X1D05  | X <sub>0</sub> L4 <sup>2</sup> <sub>out</sub> | 4B <sup>1</sup> | 8A <sup>3</sup> | 16A <sup>3</sup>  | 32A <sup>23</sup> | I/O  | IOR, PD    |

| X1D06  | X <sub>0</sub> L4 <sup>3</sup> <sub>out</sub> | 4B <sup>2</sup> | 8A <sup>4</sup> | 16A <sup>4</sup>  | 32A <sup>24</sup> | I/O  | IOR, PD    |

| X1D07  | X <sub>0</sub> L4 <sup>4</sup> <sub>out</sub> | 4B <sup>3</sup> | 8A <sup>5</sup> | 16A <sup>5</sup>  | 32A <sup>25</sup> | I/O  | IOR, PD    |

| X1D08  | X <sub>0</sub> L7 <sup>4</sup> <sub>in</sub>  | 4A <sup>2</sup> | 8A <sup>6</sup> | 16A <sup>6</sup>  | 32A <sup>26</sup> | I/O  | IOR, PD    |

| X1D09  | X <sub>0</sub> L7 <sup>3</sup> <sub>in</sub>  | 4A <sup>3</sup> | 8A <sup>7</sup> | 16A <sup>7</sup>  | 32A <sup>27</sup> | I/O  | IOR, PD    |

| X1D10  | 1C <sup>0</sup>                               |                 |                 |                   |                   | I/O  | IOT, PD    |

| XIDII  | 1D <sup>0</sup>                               |                 |                 |                   |                   | I/O  | IOT, PD    |

| X1D12  | 1E <sup>0</sup>                               |                 |                 |                   |                   | I/O  | IOL, PD    |

| X1D13  | 1F <sup>0</sup>                               |                 |                 |                   |                   | I/O  | IOL, PD    |

| X1D14  |                                               | 4C <sup>0</sup> | 8B <sup>0</sup> | 16A <sup>8</sup>  | 32A <sup>28</sup> | I/O  | IOR, PD    |

| X1D15  |                                               | 4C <sup>1</sup> | 8B <sup>1</sup> | 16A <sup>9</sup>  | 32A <sup>29</sup> | I/O  | IOR, PD    |

| X1D16  | X <sub>0</sub> L3 <sup>1</sup> <sub>in</sub>  | 4D <sup>0</sup> | 8B <sup>2</sup> | 16A <sup>10</sup> |                   | I/O  | IOL, PD    |

| XID17  | X <sub>0</sub> L3 <sup>0</sup> <sub>in</sub>  | 4D <sup>1</sup> | 8B <sup>3</sup> | 16A <sup>11</sup> |                   | I/O  | IOL, PD    |

| X1D18  | X <sub>0</sub> L3 <sup>0</sup> <sub>out</sub> | 4D <sup>2</sup> | 8B <sup>4</sup> | 16A <sup>12</sup> |                   | I/O  | IOL, PD    |

| X1D19  | X <sub>0</sub> L3 <sup>1</sup> <sub>out</sub> | 4D <sup>3</sup> | 8B <sup>5</sup> | 16A <sup>13</sup> |                   | I/O  | IOL, PD    |

(continued)

| Signal | Function                                      |                  |                 |                 |                   |                   | Type | Properties |

|--------|-----------------------------------------------|------------------|-----------------|-----------------|-------------------|-------------------|------|------------|

| X1D20  | Tunction                                      |                  | 4C <sup>2</sup> | 8B <sup>6</sup> | 16A <sup>14</sup> | 32A <sup>30</sup> | 1/0  | IOR, PD    |

| X1D21  |                                               |                  | 4C <sup>3</sup> | 8B <sup>7</sup> | 16A <sup>15</sup> | 32A <sup>31</sup> | 1/0  | IOR, PD    |

| X1D22  | X <sub>0</sub> L3 <sup>4</sup> <sub>out</sub> | 1G <sup>0</sup>  |                 |                 |                   |                   | 1/0  | IOL, PD    |

| X1D23  | 0 - out                                       | 1H <sup>0</sup>  |                 |                 |                   |                   | 1/0  | IOL, PD    |

| X1D24  |                                               | 110              |                 |                 |                   |                   | 1/0  | IOR, PD    |

| X1D25  |                                               | 1J <sup>0</sup>  |                 |                 |                   |                   | 1/0  | IOR, PD    |

| X1D26  |                                               |                  | 4E <sup>0</sup> | 8C <sup>0</sup> | 16B <sup>0</sup>  |                   | 1/0  | IOT, PD    |

| X1D27  |                                               |                  | 4E <sup>1</sup> | 8C <sup>1</sup> | 16B <sup>1</sup>  |                   | I/O  | IOT, PD    |

| X1D28  |                                               |                  | 4F <sup>0</sup> | 8C <sup>2</sup> | 16B <sup>2</sup>  |                   | I/O  | IOT, PD    |

| X1D29  |                                               |                  | 4F <sup>1</sup> | 8C <sup>3</sup> | 16B <sup>3</sup>  |                   | I/O  | IOT, PD    |

| X1D30  |                                               |                  | 4F <sup>2</sup> | 8C <sup>4</sup> | 16B <sup>4</sup>  |                   | I/O  | IOT, PD    |

| X1D31  |                                               |                  | 4F <sup>3</sup> | 8C <sup>5</sup> | 16B <sup>5</sup>  |                   | I/O  | IOT, PD    |

| X1D32  |                                               |                  | 4E <sup>2</sup> | 8C <sup>6</sup> | 16B <sup>6</sup>  |                   | I/O  | IOT, PD    |

| X1D33  |                                               |                  | 4E <sup>3</sup> | 8C <sup>7</sup> | 16B <sup>7</sup>  |                   | I/O  | IOT, PD    |

| X1D34  | X <sub>0</sub> L0 <sup>2</sup> <sub>out</sub> | 1K <sup>0</sup>  |                 |                 |                   |                   | I/O  | IOL, PD    |

| X1D35  | X <sub>0</sub> L0 <sup>3</sup> <sub>out</sub> | 1 L <sup>0</sup> |                 |                 |                   |                   | I/O  | IOL, PD    |

| X1D36  | X <sub>0</sub> L0 <sup>4</sup> <sub>out</sub> | 1 M <sup>0</sup> |                 | 8D <sup>0</sup> | 16B <sup>8</sup>  |                   | I/O  | IOL, PD    |

| X1D37  | X <sub>0</sub> L3 <sup>4</sup> <sub>in</sub>  | 1 N <sup>0</sup> |                 | 8D <sup>1</sup> | 16B <sup>9</sup>  |                   | I/O  | IOL, PD    |

| X1D38  | X <sub>0</sub> L3 <sup>3</sup> <sub>in</sub>  | 10 <sup>0</sup>  |                 | 8D <sup>2</sup> | 16B <sup>10</sup> |                   | I/O  | IOL, PD    |

| X1D39  | X <sub>0</sub> L3 <sup>2</sup> <sub>in</sub>  | 1 P <sup>0</sup> |                 | 8D <sup>3</sup> | 16B <sup>11</sup> |                   | I/O  | IOL, PD    |

| X1D40  |                                               |                  |                 | 8D <sup>4</sup> | 16B <sup>12</sup> |                   | I/O  | IOT, PD    |

| X1D41  |                                               |                  |                 | 8D <sup>5</sup> | 16B <sup>13</sup> |                   | I/O  | IOT, PD    |

| X1D42  |                                               |                  |                 | 8D <sup>6</sup> | 16B <sup>14</sup> |                   | I/O  | IOT, PD    |

| X1D43  |                                               |                  |                 | 8D <sup>7</sup> | 16B <sup>15</sup> |                   | I/O  | IOT, PD    |

| X1D49  | X <sub>0</sub> L1 <sup>4</sup> <sub>in</sub>  |                  |                 |                 |                   | 32A <sup>0</sup>  | I/O  | IOL, PD    |

| X1D50  | X <sub>0</sub> L1 <sup>3</sup> <sub>in</sub>  |                  |                 |                 |                   | 32A <sup>1</sup>  | I/O  | IOL, PD    |

| X1D51  | X <sub>0</sub> L1 <sup>2</sup> <sub>in</sub>  |                  |                 |                 |                   | 32A <sup>2</sup>  | I/O  | IOL, PD    |

| X1D52  | X <sub>0</sub> L1 <sup>1</sup> <sub>in</sub>  |                  |                 |                 |                   | 32A <sup>3</sup>  | I/O  | IOL, PD    |

| X1D53  | X <sub>0</sub> L1 <sup>0</sup> <sub>in</sub>  |                  |                 |                 |                   | 32A <sup>4</sup>  | I/O  | IOL, PD    |

| X1D54  | X <sub>0</sub> L1 <sup>0</sup> <sub>out</sub> |                  |                 |                 |                   | 32A <sup>5</sup>  | I/O  | IOL, PD    |

| X1D55  | X <sub>0</sub> L1 <sup>1</sup> <sub>out</sub> |                  |                 |                 |                   | 32A <sup>6</sup>  | I/O  | IOL, PD    |

| X1D56  | X <sub>0</sub> L1 <sup>2</sup> <sub>out</sub> |                  |                 |                 |                   | 32A <sup>7</sup>  | I/O  | IOL, PD    |

| X1D57  | X <sub>0</sub> L1 <sup>3</sup> <sub>out</sub> |                  |                 |                 |                   | 32A <sup>8</sup>  | I/O  | IOL, PD    |

| X1D58  | X <sub>0</sub> L1 <sup>4</sup> <sub>out</sub> |                  |                 |                 |                   | 32A <sup>9</sup>  | I/O  | IOL, PD    |

| X1D61  | X <sub>0</sub> L2 <sup>4</sup> <sub>in</sub>  |                  |                 |                 |                   | 32A <sup>10</sup> | I/O  | IOL, PD    |

| X1D62  | X <sub>0</sub> L2 <sup>3</sup> <sub>in</sub>  |                  |                 |                 |                   | 32A <sup>11</sup> | I/O  | IOL, PD    |

| X1D63  | X <sub>0</sub> L2 <sup>2</sup> <sub>in</sub>  |                  |                 |                 |                   | 32A <sup>12</sup> | I/O  | IOL, PD    |

| X1D64  | X <sub>0</sub> L2 <sup>1</sup> <sub>in</sub>  |                  |                 |                 |                   | 32A <sup>13</sup> | I/O  | IOL, PD    |

| X1D65  | X <sub>0</sub> L2 <sup>0</sup> <sub>in</sub>  |                  |                 |                 |                   | 32A <sup>14</sup> | I/O  | IOL, PD    |

| X1D66  | X <sub>0</sub> L2 <sup>0</sup> <sub>out</sub> |                  |                 |                 |                   | 32A <sup>15</sup> | I/O  | IOL, PD    |

| X1D67  | X <sub>0</sub> L2 <sup>1</sup> <sub>out</sub> |                  |                 |                 |                   | 32A <sup>16</sup> | I/O  | IOL, PD    |

| X1D68  | X <sub>0</sub> L2 <sup>2</sup> <sub>out</sub> |                  |                 |                 |                   | 32A <sup>17</sup> | I/O  | IOL, PD    |

| X1D69  | X <sub>0</sub> L2 <sup>3</sup> <sub>out</sub> |                  |                 |                 |                   | 32A <sup>18</sup> | I/O  | IOL, PD    |

(continued)

| Signal | Function        |                   | Type | Properties |

|--------|-----------------|-------------------|------|------------|

| X1D70  | $X_0L2_{out}^4$ | 32A <sup>19</sup> | I/O  | IOL, PD    |

| System pins (3) |                     |       |             |  |  |  |  |  |  |

|-----------------|---------------------|-------|-------------|--|--|--|--|--|--|

| Signal          | Function            | Type  | Properties  |  |  |  |  |  |  |

| CLK             | PLL reference clock | Input | IOL, PD, ST |  |  |  |  |  |  |

| DEBUG_N         | Multi-chip debug    | I/O   | IOL, PU     |  |  |  |  |  |  |

| MODE[1:0]       | Boot mode select    | Input | PU          |  |  |  |  |  |  |

|           | usb pins (5)                   |      |            |  |  |  |  |  |  |  |  |  |

|-----------|--------------------------------|------|------------|--|--|--|--|--|--|--|--|--|

| Signal    | Function                       | Type | Properties |  |  |  |  |  |  |  |  |  |

| USB_DM    | USB Serial Data Inverted       | I/O  |            |  |  |  |  |  |  |  |  |  |

| USB_DP    | USB Serial Data                | I/O  |            |  |  |  |  |  |  |  |  |  |

| USB_ID    | USB Device ID (OTG) - Reserved | I/O  |            |  |  |  |  |  |  |  |  |  |

| USB_RTUNE | USB resistor                   | I/O  |            |  |  |  |  |  |  |  |  |  |

| USB_VBUS  | USB Power Detect Pin           | I/O  |            |  |  |  |  |  |  |  |  |  |

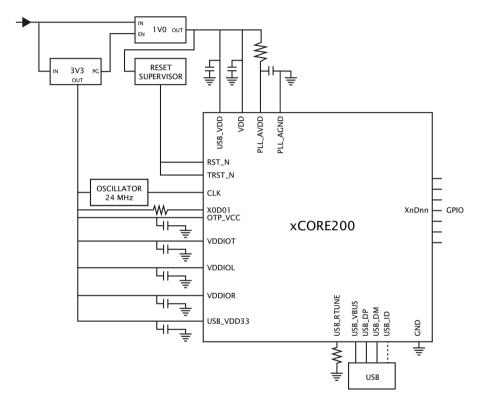

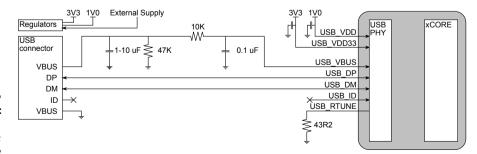

# 5 Example Application Diagram

Figure 2: Simplified Reference Schematic

- ▶ see Section 10 for details on the USB PHY

- ▶ see Section 12 for details on the power supplies and PCB design

# 6 Product Overview

The XUF216-512-FB236 is a powerful device that consists of two xCORE Tiles, each comprising a flexible logical processing cores with tightly integrated I/O and on-chip memory.

# 6.1 Logical cores

Each tile has 8 active logical cores, which issue instructions down a shared five-stage pipeline. Instructions from the active cores are issued round-robin. If up to five logical cores are active, each core is allocated a fifth of the processing cycles. If more than five logical cores are active, each core is allocated at least 1/n cycles (for n cores). Figure 3 shows the guaranteed core performance depending on the number of cores used.

Figure 3: Logical core performance

| Speed | MIPS      | Frequency | Minimum MIPS per core (for <i>n</i> cores) |     |     |     |     |    |    |    |

|-------|-----------|-----------|--------------------------------------------|-----|-----|-----|-----|----|----|----|

| grade |           |           | 1                                          | 2   | 3   | 4   | 5   | 6  | 7  | 8  |

| 10    | 1000 MIPS | 500 MHz   | 100                                        | 100 | 100 | 100 | 100 | 83 | 71 | 63 |

There is no way that the performance of a logical core can be reduced below these predicted levels (unless *priority threads* are used: in this case the guaranteed minimum performance is computed based on the number of priority threads as defined in the architecture manual). Because cores may be delayed on I/O, however, their unused processing cycles can be taken by other cores. This means that for more than five logical cores, the performance of each core is often higher than the predicted minimum but cannot be guaranteed.

The logical cores are triggered by events instead of interrupts and run to completion. A logical core can be paused to wait for an event.

#### 6.2 xTIME scheduler

The xTIME scheduler handles the events generated by xCORE Tile resources, such as channel ends, timers and I/O pins. It ensures that all events are serviced and synchronized, without the need for an RTOS. Events that occur at the I/O pins are handled by the Hardware-Response ports and fed directly to the appropriate xCORE Tile. An xCORE Tile can also choose to wait for a specified time to elapse, or for data to become available on a channel.

Tasks do not need to be prioritised as each of them runs on their own logical xCORE. It is possible to share a set of low priority tasks on a single core using cooperative multitasking.

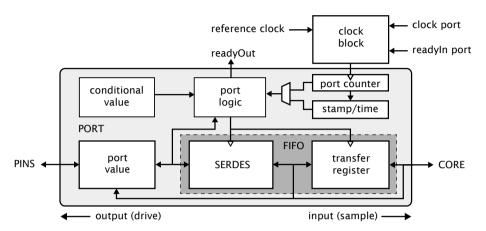

#### 6.3 Hardware Response Ports

Hardware Response ports connect an xCORE tile to one or more physical pins and as such define the interface between hardware attached to the XUF216-512-FB236, and the software running on it. A combination of 1 bit, 4 bit, 8 bit, 16 bit and 32 bit

ports are available. All pins of a port provide either output or input. Signals in different directions cannot be mapped onto the same port.

Figure 4: Port block diagram

The port logic can drive its pins high or low, or it can sample the value on its pins, optionally waiting for a particular condition. Ports are accessed using dedicated instructions that are executed in a single processor cycle. xCORE-200 IO pins can be used as *open collector* outputs, where signals are driven low if a zero is output, but left high impedance if a one is output. This option is set on a per-port basis.

Data is transferred between the pins and core using a FIFO that comprises a SERDES and transfer register, providing options for serialization and buffered data.

Each port has a 16-bit counter that can be used to control the time at which data is transferred between the port value and transfer register. The counter values can be obtained at any time to find out when data was obtained, or used to delay I/O until some time in the future. The port counter value is automatically saved as a timestamp, that can be used to provide precise control of response times.

The ports and xCONNECT links are multiplexed onto the physical pins. If an xConnect Link is enabled, the pins of the underlying ports are disabled. If a port is enabled, it overrules ports with higher widths that share the same pins. The pins on the wider port that are not shared remain available for use when the narrower port is enabled. Ports always operate at their specified width, even if they share pins with another port.

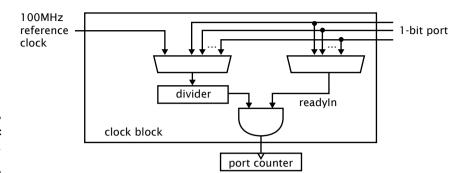

#### 6.4 Clock blocks

xCORE devices include a set of programmable clocks called clock blocks that can be used to govern the rate at which ports execute. Each xCORE tile has six clock blocks: the first clock block provides the tile reference clock and runs at a default frequency of 100MHz; the remaining clock blocks can be set to run at different frequencies.

Figure 5: Clock block diagram

A clock block can use a 1-bit port as its clock source allowing external application clocks to be used to drive the input and output interfaces. xCORE-200 clock blocks optionally divide the clock input from a 1-bit port.

In many cases I/O signals are accompanied by strobing signals. The xCORE ports can input and interpret strobe (known as readyln and readyOut) signals generated by external sources, and ports can generate strobe signals to accompany output data.

On reset, each port is connected to clock block 0, which runs from the xCORE Tile reference clock.

# 6.5 Channels and Channel Ends

Logical cores communicate using point-to-point connections, formed between two channel ends. A channel-end is a resource on an xCORE tile, that is allocated by the program. Each channel-end has a unique system-wide identifier that comprises a unique number and their tile identifier. Data is transmitted to a channel-end by an output-instruction; and the other side executes an input-instruction. Data can be passed synchronously or asynchronously between the channel ends.

#### 6.6 xCONNECT Switch and Links

XMOS devices provide a scalable architecture, where multiple xCORE devices can be connected together to form one system. Each xCORE device has an xCONNECT interconnect that provides a communication infrastructure for all tasks that run on the various xCORE tiles on the system.

The interconnect relies on a collection of switches and XMOS links. Each  $\times$ CORE device has an on-chip switch that can set up circuits or route data. The switches are connected by  $\times$ Connect Links. An XMOS link provides a physical connection between two switches. The switch has a routing algorithm that supports many different topologies, including lines, meshes, trees, and hypercubes.

The links operate in either 2 wires per direction or 5 wires per direction mode, depending on the amount of bandwidth required. Circuit switched, streaming

Figure 6: Switch, links and channel ends

and packet switched data can both be supported efficiently. Streams provide the fastest possible data rates between xCORE Tiles (up to 250 MBit/s), but each stream requires a single link to be reserved between switches on two tiles. All packet communications can be multiplexed onto a single link.

Information on the supported routing topologies that can be used to connect multiple devices together can be found in the XS1-UF Link Performance and Design Guide, X2999.

# 7 PLL

The PLL creates a high-speed clock that is used for the switch, tile, and reference clock. The PLL multiplication value is selected through the two MODE pins, and can be changed by software to speed up the tile or use less power. The MODE pins are set as shown in Figure 7:

Figure 7: PLL multiplier values and MODE pins

| Oscillator  | MC | MODE Tile Boot |             | PLL Ratio | PLL | settings |   |  |

|-------------|----|----------------|-------------|-----------|-----|----------|---|--|

| Frequency   | 1  | 0              | Frequency   |           | OD  | F        | R |  |

| 3.25-10 MHz | 0  | 0              | 130-400 MHz | 40        | 1   | 159      | 0 |  |

| 9-25 MHz    | 1  | 1              | 144-400 MHz | 16        | 1   | 63       | 0 |  |

| 25-50 MHz   | 1  | 0              | 167-400 MHz | 8         | 1   | 31       | 0 |  |

| 50-100 MHz  | 0  | 1              | 196-400 MHz | 4         | 1   | 15       | 0 |  |

Figure 7 also lists the values of *OD*, *F* and *R*, which are the registers that define the ratio of the tile frequency to the oscillator frequency:

$$F_{core} = F_{osc} \times \frac{F+1}{2} \times \frac{1}{R+1} \times \frac{1}{OD+1}$$

OD, F and R must be chosen so that  $0 \le R \le 63$ ,  $0 \le F \le 4095$ ,  $0 \le OD \le 7$ , and  $260MHz \le F_{osc} \times \frac{F+1}{2} \times \frac{1}{R+1} \le 1.3GHz$ . The OD, F, and R values can be modified by writing to the digital node PLL configuration register.

The MODE pins must be held at a static value during and after deassertion of the system reset. If the USB PHY is used, then either a 24 MHz or 12 MHz oscillator must be used.

If a different tile frequency is required (eg, 500 MHz), then the PLL must be reprogrammed after boot to provide the required tile frequency. The XMOS tools perform this operation by default. Further details on configuring the clock can be found in the xCORE-200 Clock Frequency Control document.

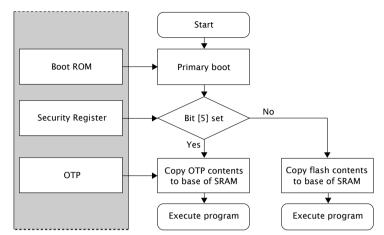

# 8 Boot Procedure

The device is kept in reset by driving RST\_N low. When in reset, all GPIO pins have a pull-down enabled. The processor must be held in reset until VDDIOL is in spec for at least 1 ms. When the device is taken out of reset by releasing RST\_N the processor starts its internal reset process. After 15-150  $\mu$ s (depending on the input clock) the processor boots.

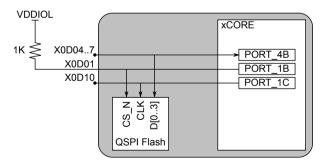

The device boots from a QSPI flash (IS25LQ016B) that is embedded in the device. The QSPI flash is connected to the ports on Tile 0 as shown in Figure 8. An external 1K resistor must connect X0D01 to VDDIOL. X0D10 should ideally not be connected. If X0D10 is connected, then a 150 ohm series resistor close to the device is recommended. X0D04. X0D07 should be not connected.

Figure 8: QSPI port connectivity

The xCORE Tile boot procedure is illustrated in Figure 9. If bit 5 of the security register (see §9.1) is set, the device boots from OTP. Otherwise, the device boots from the internal flash.

The boot image has the following format:

Figure 9: Boot procedure

- ▶ A 32-bit program size *s* in words.

- ▶ Program consisting of  $s \times 4$  bytes.

- ➤ A 32-bit CRC, or the value 0x0D15AB1E to indicate that no CRC check should be performed.

The program size and CRC are stored least significant byte first. The program is loaded into the lowest memory address of RAM, and the program is started from that address. The CRC is calculated over the byte stream represented by the program size and the program itself. The polynomial used is 0xEDB88320 (IEEE 802.3); the CRC register is initialized with 0xFFFFFFFF and the residue is inverted to produce the CRC.

# 8.1 Security register

The security register enables security features on the xCORE tile. The features shown in Figure 10 provide a strong level of protection and are sufficient for providing strong IP security.

# 9 Memory

#### 9.1 OTP

Each xCORE Tile integrates 8 KB one-time programmable (OTP) memory along with a security register that configures system wide security features. The OTP holds data in four sectors each containing 512 rows of 32 bits which can be used to implement secure bootloaders and store encryption keys. Data for the security register is loaded from the OTP on power up. All additional data in OTP is copied from the OTP to SRAM and executed first on the processor.

| Feature              | Bit  | Description                                                                                                                                                                                                                    |

|----------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Disable JTAG         | 0    | The JTAG interface is disabled, making it impossible for the tile state or memory content to be accessed via the JTAG interface.                                                                                               |

| Disable Link access  | 1    | Other tiles are forbidden access to the processor state via the system switch. Disabling both JTAG and Link access transforms an xCORE Tile into a "secure island" with other tiles free for non-secure user application code. |

| Secure Boot          | 5    | The xCORE Tile is forced to boot from address 0 of the OTP, allowing the xCORE Tile boot ROM to be bypassed (see §8).                                                                                                          |

| Redundant rows       | 7    | Enables redundant rows in OTP.                                                                                                                                                                                                 |

| Sector Lock 0        | 8    | Disable programming of OTP sector 0.                                                                                                                                                                                           |

| Sector Lock 1        | 9    | Disable programming of OTP sector 1.                                                                                                                                                                                           |

| Sector Lock 2        | 10   | Disable programming of OTP sector 2.                                                                                                                                                                                           |

| Sector Lock 3        | 11   | Disable programming of OTP sector 3.                                                                                                                                                                                           |

| OTP Master Lock      | 12   | Disable OTP programming completely: disables updates to all sectors and security register.                                                                                                                                     |

| Disable JTAG-OTP     | 13   | Disable all (read & write) access from the JTAG interface to this OTP.                                                                                                                                                         |

| Disable Global Debug | 14   | Disables access to the DEBUG_N pin.                                                                                                                                                                                            |

|                      | 2115 | General purpose software accessable security register available to end-users.                                                                                                                                                  |

|                      | 3122 | General purpose user programmable JTAG UserID code extension.                                                                                                                                                                  |

Figure 10: Security register features

The OTP memory is programmed using three special I/O ports: the OTP address port is a 16-bit port with resource ID 0x100200, the OTP data is written via a 32-bit port with resource ID 0x200100, and the OTP control is on a 16-bit port with ID 0x100300. Programming is performed through libotp and xburn.

#### **9.2 SRAM**

Each xCORE Tile integrates a single 256KBSRAM bank for both instructions and data. All internal memory is 32 bits wide, and instructions are either 16-bit or 32-bit. Byte (8-bit), half-word (16-bit) or word (32-bit) accesses are supported and are executed within one tile clock cycle. There is no dedicated external memory interface, although data memory can be expanded through appropriate use of the ports.

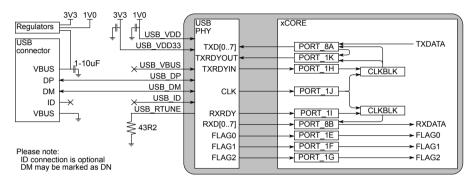

#### 10 USB PHY

The USB PHY provides High-Speed and Full-Speed, device, host, and on-the-go functionality. The PHY is configured through a set of peripheral registers (Appendix F),

and data is communicated through ports on the digital node. A library, XUD, is provided to implement *USB-device* functionality.

The USB PHY is connected to the ports on Tile 0 and Tile 1 as shown in Figure 11. When the USB PHY is enabled on Tile 0, the ports shown can on Tile 0 only be used with the USB PHY. When the USB PHY is enabled on Tile 1, then the ports shown can on Tile 1 only be used with the USB PHY. All other IO pins and ports are unaffected. The USB PHY should not be enabled on both tiles. Two clock blocks can be used to clock the USB ports. One clock block for the TXDATA path, and one clock block for the RXDATA path. Details on how to connect those ports are documented in an application note on USB for xCORE-200.

Figure 11: Bus powered USB-device

An external resistor of 43.2 ohm (1% tolerance) should connect USB\_RTUNE to ground, as close as possible to the device.

#### 10.1 USB VBUS

USB\_VBUS need not be connected if the device is wholly powered by USB, and the device is used to implement a *USB-device*.

If you use the USB PHY to design a self-powered *USB-device*, then the device must be able detect the presence of VBus on the USB connector (so the device can disconnect its pull-up resistors from D+/D- to ensure the device does not have any voltage on the D+/D- pins when VBus is not present, "USB Back Voltage Test"). This requires USB\_VBUS to be connected to the VBUS pin of the USB connector as is shown in Figure 12.

Figure 12: Self powered USB-device

When connecting a USB cable to the device it is possible an overvoltage transient will be present on VBus due to the inductance of the USB cable combined with the required input capacitor on VBus. The circuit in Figure 12 ensures that the transient does not damage the device. The 10k series resistor and 0.1uF capacitor ensure than any input transient is filtered and does not reach the device. The 47k resistor to ground is a bleeder resistor to discharge the input capacitor when VBus is not present. The 1-10uF input capacitor is required as part of the USB specification. A typical value would be 2.2uF to ensure the 1uF minimum requirement is met even under voltage bias conditions.

In any case, extra components (such as a ferrite bead and diodes) may be required for EMC compliance and ESD protection. Different wiring is required for USB-host and USB-OTG.

# 10.2 Logical Core Requirements

The XMOS XUD software component runs in a single logical core with endpoint and application cores communicating with it via a combination of channel communication and shared memory variables.

Each IN (host requests data from device) or OUT (data transferred from host to device) endpoint requires one logical core.

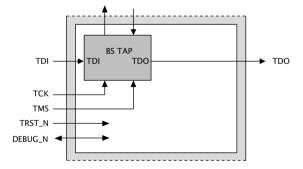

# 11 JTAG

The JTAG module can be used for loading programs, boundary scan testing, incircuit source-level debugging and programming the OTP memory.

Figure 13: JTAG chain structure

The JTAG chain structure is illustrated in Figure 13. It comprises a single 1149.1 compliant TAP that can be used for boundary scan of the I/O pins. It has a 4-bit IR and 32-bit DR. It also provides access to a chip TAP that in turn can access the xCORE Tile for loading code and debugging.

The TRST\_N pin must be asserted low during and after power up for 100 ns. If JTAG is not required, the TRST\_N pin can be tied to ground to hold the JTAG module in reset.

The DEBUG\_N pin is used to synchronize the debugging of multiple xCORE Tiles. This pin can operate in both output and input mode. In output mode and when configured to do so, DEBUG\_N is driven low by the device when the processor hits a debug break point. Prior to this point the pin will be tri-stated. In input mode and when configured to do so, driving this pin low will put the xCORE Tile into debug mode. Software can set the behavior of the xCORE Tile based on this pin. This pin should have an external pull up of  $4K7-47K\Omega$  or left not connected in single core applications.

The JTAG device identification register can be read by using the IDCODE instruction. Its contents are specified in Figure 14.

Figure 14: IDCODE return value

| Bi | t31 |        |   |             | Device Identification Register |   |   |   |   |   |   |   |   |   |   |   |                       |   |   | В | it0 |   |   |   |   |   |   |   |   |   |   |

|----|-----|--------|---|-------------|--------------------------------|---|---|---|---|---|---|---|---|---|---|---|-----------------------|---|---|---|-----|---|---|---|---|---|---|---|---|---|---|

|    | Ve  | ersion |   | Part Number |                                |   |   |   |   |   |   |   |   |   |   |   | Manufacturer Identity |   |   |   |     |   |   |   |   |   | 1 |   |   |   |   |

| 0  | 0   | 0      | 0 | 0           | 0                              | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1                     | 1 | 0 | 0 | 1   | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| 0  |     |        |   | 0           |                                |   |   | 0 |   |   | 0 |   |   |   | 6 |   |                       |   | 6 |   |     |   | 3 |   |   |   | 3 |   |   |   |   |

The JTAG usercode register can be read by using the USERCODE instruction. Its contents are specified in Figure 15. The OTP User ID field is read from bits [22:31] of the security register on xCORE Tile 0, see §9.1 (all zero on unprogrammed devices).

Figure 15: USERCODE return value

| Bit                | Bit31 Usercode Register B |   |   |     |   |   |   |   |   |   |   |                  |   |   |   | it0 |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|--------------------|---------------------------|---|---|-----|---|---|---|---|---|---|---|------------------|---|---|---|-----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| OTP User ID Unused |                           |   |   |     |   |   |   |   |   |   |   | Silicon Revision |   |   |   |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| 0                  | 0                         | 0 | 0 | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0                | 0 | 1 | 0 | 1   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0                  |                           |   |   | 0 ( |   |   |   |   | 0 |   |   | 2                | 2 |   | 8 |     |   |   | ( | ) |   |   | ( | ) |   | 0 |   |   |   |   |   |

# 12 Board Integration

The device has the following power supply pins:

- ▶ VDD pins for the xCORE Tile, including a USB\_VDD pin that powers the USB PHY

- ▶ VDDIO pins for the I/O lines. Separate I/O supplies are provided for the left, top, and right side of the package; different I/O voltages may be supplied on those. The signal description (Section 4) specifies which I/O is powered from which power-supply

- PLL\_AVDD pins for the PLL

- ▶ OTP\_VCC pins for the OTP

- ▶ A USB\_VDD33 pin for the analogue supply to the USB-PHY

Several pins of each type are provided to minimize the effect of inductance within the package, all of which must be connected. The power supplies must be brought up monotonically and input voltages must not exceed specification at any time.

The VDD supply must ramp from 0 V to its final value within 10 ms to ensure correct startup.

The VDDIO and OTP\_VCC supply must ramp to its final value before VDD reaches 0.4 V.

The PLL\_AVDD supply should be separated from the other noisier supplies on the board. The PLL requires a very clean power supply, and a low pass filter (for example, a  $4.7\,\Omega$  resistor and  $100\,\text{nF}$  multi-layer ceramic capacitor) is recommended on this pin.

The following ground pins are provided:

- ▶ PLL AGND for PLL AVDD

- ► GND for all other supplies

All ground pins must be connected directly to the board ground.

The VDD and VDDIO supplies should be decoupled close to the chip by several 100 nF low inductance multi-layer ceramic capacitors between the supplies and GND (for example, 100nF 0402 for every other supply pin). The ground side of the decoupling capacitors should have as short a path back to the GND pins as possible. A bulk decoupling capacitor of at least 10 uF should be placed on each of these supplies.

RST\_N is an active-low asynchronous-assertion global reset signal. Following a reset, the PLL re-establishes lock after which the device boots up according to the boot mode (*see* §8). RST\_N and must be asserted low during and after power up for 100 ns.

#### 12.1 USB connections

USB\_VBUS should be connected to the VBUS pin of the USB connector. A 2.2 uF capacitor to ground is required on the VBUS pin. A ferrite bead may be used to reduce HF noise.

For self-powered systems, a bleeder resistor may be required to stop VBUS from floating when no USB cable is attached.

USB\_DP and USB\_DN should be connected to the USB connector. USB\_ID does not need to be connected.

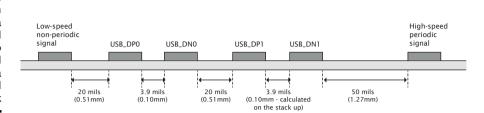

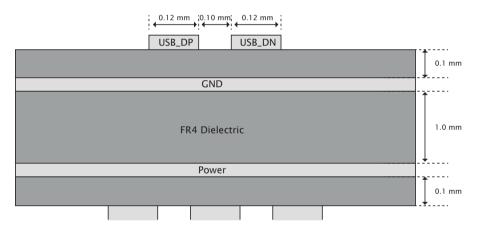

# 12.2 USB signal routing and placement

The USB\_DP and USB\_DN lines are the positive and negative data polarities of a high speed USB signal respectively. Their high-speed differential nature implies that they must be coupled and properly isolated. The board design must ensure that the board traces for USB\_DP and USB\_DN are tightly matched. In addition, according to the USB 2.0 specification, the USB\_DP and USB\_DN differential impedance must be  $90\ \Omega.$

Figure 16:

USB trace

separation

showing a

low speed

signal, two

differential

pairs and a

high-speed

clock

# 12.2.1 General routing and placement guidelines

The following guidelines will help to avoid signal quality and EMI problems on high speed USB designs. They relate to a four-layer (Signal, GND, Power, Signal) PCB.

Figure 17: Example USB board stack

For best results, most of the routing should be done on the top layer (assuming the USB connector and XS2-UF16A-512-FB236 are on the top layer) closest to GND. Reference planes should be below the transmission lines in order to maintain control of the trace impedance.

We recommend that the high-speed clock and high-speed USB differential pairs are routed first before any other routing. When routing high speed USB signals, the following guidelines should be followed:

- ▶ High speed differential pairs should be routed together.

- ▶ High-speed USB signal pair traces should be trace-length matched. Maximum trace-length mismatch should be no greater than 4mm.

- ► Ensure that high speed signals (clocks, USB differential pairs) are routed as far away from off-board connectors as possible.

- ► High-speed clock and periodic signal traces that run parallel should be at least 1.27mm away from USB\_DP/USB\_DN (see Figure 16).

- ► Low-speed and non-periodic signal traces that run parallel should be at least 0.5mm away from USB\_DP/USB\_DN (see Figure 16).

- ▶ Route high speed USB signals on the top of the PCB wherever possible.

- ▶ Route high speed USB traces over continuous power planes, with no breaks. If a trade-off must be made, changing signal layers is preferable to crossing plane splits.

- ▶ Follow the  $20 \times h$  rule; keep traces  $20 \times h$  (the height above the power plane) away from the edge of the power plane.

- ▶ Use a minimum of vias in high speed USB traces.

- ► Avoid corners in the trace. Where necessary, rather than turning through a 90 degree angle, use two 45 degree turns or an arc.

- ▶ DO NOT route USB traces near clock sources, clocked circuits or magnetic devices

- Avoid stubs on high speed USB signals.

# 12.3 Land patterns and solder stencils

The package is a 236 ball Fine Ball Grid Array (FBGA) on a 0.5 mm pitch. We recommend you use HDI or better PCB technology. The missing balls in the outer rows can be used to route the first inner row out over the top layer. The missing balls in the center can be used for ground vias. The missing rows four and five can be used for VDD vias if required.

The land patterns and solder stencils will depend on the PCB manufacturing process. We recommend you design them with using the IPC specifications "Generic Requirements for Surface Mount Design and Land Pattern Standards" IPC-7351B. This standard aims to achieve desired targets of heel, toe and side fillets for solder-joints. The mechanical drawings in Section 14 specify the dimensions and tolerances.

#### 12.4 Ground and Thermal Vias

Vias from the ground balls into the ground plane of the PCB are recommended for a low inductance ground connection and good thermal performance. Typical designs could use 16 vias in a  $4 \times 4$  grid, equally spaced amongst the ground balls.

# 12.5 Moisture Sensitivity

XMOS devices are, like all semiconductor devices, susceptible to moisture absorption. When removed from the sealed packaging, the devices slowly absorb moisture from the surrounding environment. If the level of moisture present in the device