## imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

### Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# zilog

Z16C30

### **CMOS USC Universal** Serial Controller

### **Product Specification**

DS007902-0708

PRELIMINARY

Copyright ©2008 by Zilog<sup>®</sup>, Inc. All rights reserved. www.zilog.com

## **z**ilog<sup>°</sup>

### Warning: DO NOT USE IN LIFE SUPPORT

### LIFE SUPPORT POLICY

ZILOG'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF ZILOG CORPORATION.

### As used herein

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

### **Document Disclaimer**

©2008 by Zilog, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZILOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. The information contained within this document has been verified according to the general principles of electrical and mechanical engineering.

Z8, Z8 Encore!, Z8 Encore! XP, Z8 Encore! MC, Crimzon, eZ80, and ZNEO are trademarks or registered trademarks of Zilog, Inc. All other product or service names are the property of their respective owners.

ISO 9001:2000 FS 507510 Zilog products are designed and manufactured under an ISO registered 9001:2000 Quality Management System. For more details, please visit www.zilog.com/quality.

### **Revision History**

Each instance in Revision History reflects a change to this document from its previous revision. For more details, refer to the corresponding pages and appropriate links in the table below.

| Date      | <b>Revision Level</b> | Description                                     | Page No |

|-----------|-----------------------|-------------------------------------------------|---------|

| July 2008 | 02                    | Updated as per latest template and style guide. | All     |

| Jan 2000  | 01                    | Original issue                                  |         |

## zilog<sup>°</sup> <sub>iv</sub>

### **Table of Contents**

| Architectural Overview              |

|-------------------------------------|

| Features 1                          |

| General Description                 |

| Pin Description                     |

| Pin Functions                       |

| Electrical Characteristics 10       |

| Standard Test Conditions 10         |

| Capacitance                         |

| Miscellaneous                       |

| Temperature Ratings                 |

| DC Characteristics                  |

| AC Characteristics                  |

| USC Timing                          |

| AC Characteristics                  |

| Architecture                        |

| Data Path                           |

| Functional Description 41           |

| Data Communications Capabilities 41 |

| Data Encoding                       |

| Character Counters 44               |

| Baud Rate Generators                |

| Digital Phase-Locked Loop           |

| Counters                            |

| Clock Multiplexer                   |

|                                     |

| I/O Interface Capabilities          |

| Interrupt                           |

| Block Transfer Mode                 |

| Programming                         |

| Control Registers                   |

| Packaging                           |

| Ordering Information                |

| Codes                               |

| Customer Support                    |

|                                     |

## zilog

### **Architectural Overview**

### Features

The key features of Zilog's Z16C30 device include:

- Two Independent 0-to-10 Mbps Full-Duplex Channels, each with Two Baud Rate Generators and One digital phase-locked loop (DPLL) for Clock Recovery

- 32-byte Data FIFO's for each Receiver and Transmitter

- 110 ns Bus Cycle Time, 16-bit Data Bus Bandwidth

- Multi-Protocol Operation under Program Control with Independent Mode Selection for Receiver and Transmitter

- Async Mode with 1 to 8 Bits/Character, 1/16 to 2 Stop Bits/Character in 1/16-bit Increments, Programmable Clock Factor, Break Detect and Generation, Odd, Even, Mark, Space or no Parity and Framing Error Detection, Supports One Address/Data Bit and MIL STD 1553B Protocols

- Byte Oriented Synchronous Mode with One to Eight Bits/Character, Programmable Idle Line Condition, Optional Receive Sync Stripping; Optional Preamble Transmission, 16or 32-bit CRC, and Transmit-to-Receive Slaving (for X.21)

- Bisync Mode with 2- to 16-bit Programmable Sync Character, Programmable Idle Line Condition, Optional Receive Sync Stripping, Optional Preamble Transmission, 16- or 32-bit CRC

- Transparent Bisync Mode with EBCDIC or ASCII Character Code, Automatic CRC Handling, Programmable Idle Line Condition, Optional Preamble Transmission, Automatic Recognition of DLE, SYN, SOH, ITX, ETX, ETB, EOT, ENQ, and ITB

- External Character Sync Mode for Receive

- HDLC/SDLC Mode with Eight-Bit Address Compare, Extended Address Field Option, 16- or 32-bit CRC, Programmable Idle Line Condition, Optional Preamble Transmission and Loop Mode

- DMA Interface with Separate Request and Acknowledge for Each Receiver and Transmitter

- Channel Load Command for DMA Controlled Initialization

- Flexible Bus Interface for Direct Connection to Most Microprocessors, User Programmable for 8 or 16 Bits Wide, Directly Supports 680X0 Family or 8X86 Family Bus Interfaces

- Low Power CMOS

- 68-Pin PLCC/100-Pin VQFP Packages

## **z**ilog<sup>®</sup>

### **General Description**

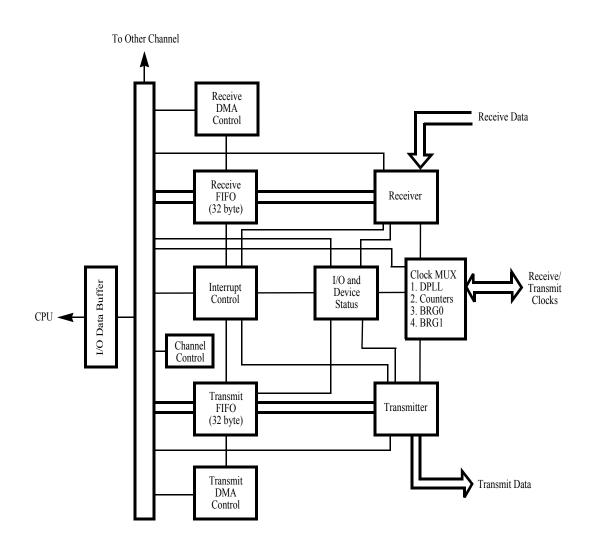

Zilog's Z16C30 USC Universal Serial Controller is a dual-channel multi-protocol data communications peripheral designed for use with any conventional multiplexed or nonmultiplexed bus. The USC functions as a serial-to-parallel, parallel-to-serial converter/ controller and may be software configured to satisfy a wide variety of serial communications applications. The device contains a variety of new, sophisticated internal functions including two baud rate generators per channel, one digital phase-locked loop (DPLL) per channel, character counters for both receive and transmit in each channel and 32-byte data FIFO's for each receiver and transmitter (Figure 1 on page 3).

Zilog now offers a high speed version of the USC with improved bus bandwidth. CPU bus accesses have been shortened from 160 ns per access to 110 ns per access. The USC has a transmit and receive clock range of up to 10 MHz (20 MHz when using the DPLL, BRG, or CTR) and data transfer rates as high as 10 Mbits/sec full duplex.

The USC handles asynchronous formats, synchronous byte-oriented formats such as BISYNC, and synchronous bit-oriented formats such as HDLC. This device supports virtually any serial data transfer application.

The device can generate and check CRC in any synchronous mode and can be programmed to check data integrity in various modes. The USC also has facilities for modem controls in both channels. In applications where these controls are not needed, the modem controls may be used for general-purpose I/O (GPIO). The same is true for most of the other pins in each channel.

Interrupts are supported with a daisy-chain hierarchy, with the two channels having completely separate interrupt structures.

High-speed data transfers through DMA are supported by a Request/Acknowledge signal pair for each receiver and transmitter. The device supports automatic status transfer through DMA and also allows device initialization under DMA control.

When written to, all reserved bits must be programmed to 0.

To aid in efficiently programming the USC, support tools are available. The Technical Manual describes in detail all features presented in this Product Specification and gives programming sequence hints. The Programmer's Assistant is a MS-DOS disk-based programming initialization tool to be used in conjunction with the Technical Manual. There are also available assorted application notes and development boards to assist in the hard-ware/software development.

All Signals with an overline, are active Low. For example:  $\overline{B/W}$ , in which WORD is active Low, and  $\overline{B}/W$ , in which BYTE is active Low.

Power connections follow these conventional descriptions:

Note:

## Zilog <sub>3</sub>

| Table 1. | <b>Power connection conventions</b> |  |

|----------|-------------------------------------|--|

|----------|-------------------------------------|--|

| Connection | Circuit         | Device          |

|------------|-----------------|-----------------|

| Power      | V <sub>CC</sub> | V <sub>DD</sub> |

| Ground     | GND             | V <sub>SS</sub> |

zilog 4

### **Pin Description**

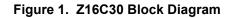

Figure 2. Z16C30 Pin Functions

zilog

5

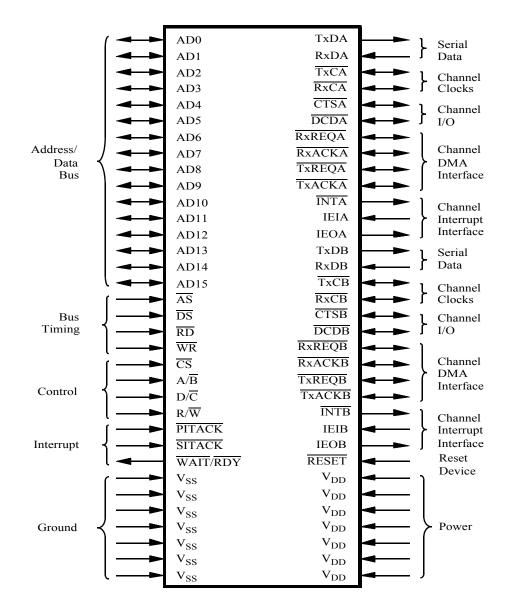

Figure 3. Z16C30 68-Pin PLCC Pin Assignments

**z**ilog<sup>°</sup>

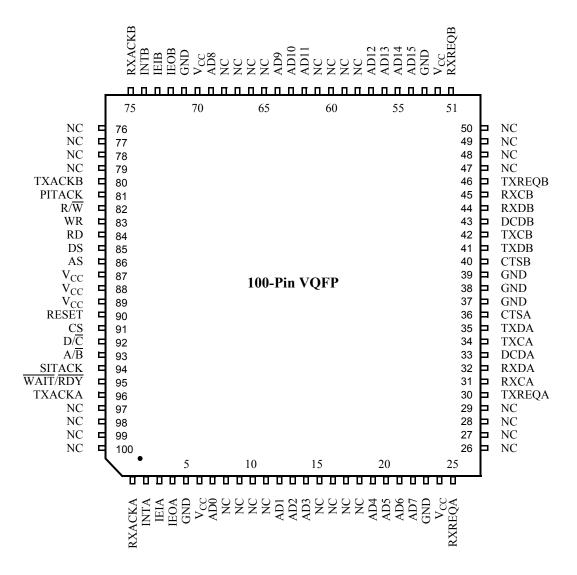

Figure 4. 100-Pin VQFP Pin Assignments

The Z16C30 contains 13 pins per channel for channel I/O, 16 pins for address and data, 12 pins for CPU handshake, and 14 pins for power and ground.

Three separate bus interface types are available for the device. The Bus Configuration Register (BCR) and external connections to the AD bus control selection of the bus type. A 16-bit bus is selected by setting BCR bit 2 to a 1. The 8-bit bus is selected by setting BCR bit 2 to 0 and tying AD15–AD8 to  $V_{SS}$ .

zilog

The 8-bit bus with separate address is selected by setting BCR bit 2 to 0 and, during the BCR write, forcing AD15 to a 1 and forcing AD14–AD8 to 0.

The multiplexed bus is selected for the USC if there is an Address Strobe prior to or during the transaction which writes the BCR. If no Address Strobe is present prior to or during the transaction which writes the BCR, a nonmultiplexed bus is selected (see Figure 29 on page 49).

### **Pin Functions**

**RESET Reset (input, active Low)**—This signal resets the device to a known state. The first write to the USC after a reset accesses the BCR to select additional bus options for the device.

AS Address Strobe (input, active Low)—This signal is used in the multiplexed bus modes to latch the address on the AD lines. The  $\overline{AS}$  signal is not used in the nonmultiplexed bus modes and should be tied to  $V_{DD}$ .

**DS Data Strobe (input, active Low)**—This signal strobes data out of the device during a read and may strobe an interrupt vector out of the device during an interrupt acknowledge cycle.  $\overline{\text{DS}}$  also strobes data into the device on the state of  $R/\overline{W}$ .

**RD Read Strobe (input, active Low)**—This signal strobes data out of the device during a read and may strobe an interrupt vector out of the device during an interrupt acknowledge cycle.

**WR Write Strobe (input, active Low)**—This signal strobes data into the device during a write.

**R/W Read/Write (input)**—This signal determines the direction of data transfer for a read or write cycle in conjunction with  $\overline{\text{DS}}$ .

**CS Chip Select (input, active Low)**—This signal selects the device for access and must be asserted for read and write cycles, but is ignored during interrupt acknowledge and flyby DMA transfers. In the case of a multiplexed bus interface,  $\overline{CS}$  is latched by the rising edge of  $\overline{AS}$ .

**A/B Channel A/Channel B Select (input)**—This signal selects between the two channels in the device. High selects channel A and Low selects channel B. This signal is sampled and the result is latched during the BCR (Bus Configuration Register) write. It programs the sense of the WAIT/RDY signal appropriate for different bus interfaces.

**D/C Data/Control Select (input)**—This signal, when High, provides for direct access to the RDR and TDR. In the case of a multiplexed bus interface,  $D/\overline{C}$  High overrides the address provided to the device.

**SITACK Status Interrupt Acknowledge (input, active Low)**—This signal is a status signal that indicates that an interrupt acknowledge cycle is in progress. The device is capable of returning an interrupt vector that may be encoded with the type of interrupt pending during this acknowledge cycle. This signal is compatible with 680X0 family microprocessors.

<mark>z</mark>ilog<sup>°</sup>

**PITACK Pulsed Interrupt Acknowledge (input, active Low)**—This signal is a strobe signal that indicates that an interrupt acknowledge cycle is in progress. The device is capable of returning an interrupt vector that may be encoded with the type of interrupt pending during this acknowledge cycle. PITACK may be programmed to accept a single pulse or double pulse acknowledge type. This programming is done in the BCR. With the double pulse type selected, the first PITACK is recognized but no action takes place. The interrupt vector is returned on the second pulse if the no vector option is not selected. The double pulse type is compatible with 8X86 family microprocessors.

**WAIT/RDY Wait/Data Ready (output, active Low)**—This signal serves to indicate when the data is available during a read cycle, when the device is ready to receive data during a write cycle, and when a valid vector is available during an interrupt acknowledge cycle. It may be programmed to function either as a Wait signal or a Ready signal using the state of the A/B pin during the BCR write. When A/B is High during the BCR write, this signal functions as a wait output and thus supports the READY function of 8X86 family microprocessors. When A/B is Low during the BCR write, this signal functions as a ready output and thus supports the DTACK function of 680X0 family microprocessors.

**AD15–AD0 Address/Data Bus (bidirectional, active High, tri-state)**—The AD signals carry addresses to, and data to and from, the device. When the 16-bit nonmultiplexed bus is selected, AD15–AD0 carry data to and from the device. Addresses are provided using a pointer within the device that is loaded with the desired register address. When selecting the 8-bit nonmultiplexed bus (without separate address) only AD7–AD0 are used to transfer data. The pointer is used for addressing, with AD15–AD8 unused. When selecting the 8-bit nonmultiplexed bus (with separate address), AD7–AD0 are used to transfer data with AD15–AD8 used as address bus. When the 16-bit multiplexed bus is selected, addresses are latched from AD7–AD0 and data transfers are sixteen bits wide. When selecting the 8-bit multiplexed bus (without separate address) only AD7–AD0 are used to transfer addresses and data, with AD15–AD8 unused. When the 8-bit multiplexed bus with separate address only AD7–AD0 are used to transfer addresses and data, with AD15–AD8 unused. When the 8-bit multiplexed bus with separate address is selected, only AD7–AD0 are used to transfer ata, while AD15–AD8 are used as an address bus.

**INTA**, **INTB** Interrupt Request (outputs, active Low)—These signals indicate that the channel has an interrupt condition pending and is requesting service. These outputs are NOT open-drain.

**IEIA, IEIB Interrupt Enable In (inputs, active High)**—The IEI signal for each channel is used with the accompanying IEO signal to form an interrupt daisy chain. An active IEI indicates that no device having higher priority is requesting or servicing an interrupt.

**IEOA, IEOB Interrupt Enable Out (outputs, active High)**—The IEO signal for each channel is used with the accompanying IEI signal to form an interrupt daisy chain. IEO is Low if IEI is Low, an interrupt is under service in the channel, or an interrupt is pending during an interrupt acknowledge cycle.

**TxACKA**, **TxACKB Transmit Acknowledge (inputs or outputs, active Low)**—The primary function of these signals is to perform fly-by DMA transfers to the transmit FIFOs. They may also be used as bit inputs or outputs.

**z**ilog<sup>°</sup>

**RxACKA**, **RxACKB** Receive Acknowledge (inputs or outputs, active Low)—The primary function of these signals is to perform fly-by DMA transfers from the receive FIFOs. They may also be used as bit inputs or outputs.

**TxDA, TxDB Transmit Data (outputs, active High, tri-state)**—These signals carry the serial transmit data for each channel.

**RxDA**, **RxDB Receive Data (inputs, active High)**—These signals carry the serial receive data for each channel.

**TxCA**, **TxCB Transmit Clock (inputs or outputs, active Low)**—These signals are used as clock inputs for any of the functional blocks within the device. They may also be used as outputs for various transmitter signals or internal clock signals.

**RxCA, RxCB Receive Clock (inputs or outputs, active Low)**—These signals are used as clock inputs for any of the functional blocks within the device. They may also be used as outputs for various receiver signals or internal clock signals.

**TxREQA, TxREQB Transmit Request (inputs or outputs, active Low)**—The primary function of these signals is to request DMA transfers to the transmit FIFOs. They may also be used as simple inputs or outputs.

**RxREQA, RxREQB Receive Request (inputs or outputs, active Low)**—The primary function of these signals is to request DMA transfers from the receive FIFOs. They may also be used as simple inputs or outputs.

**CTSA, CTSB Clear To Send (inputs or outputs, active Low)**—These signals are used as enables for the respective transmitters. They may also be programmed to generate interrupts on either transition or used as simple inputs or outputs.

**DCDA, DCDB Data Carrier Detect (inputs or outputs, active Low)**—These signals are used as enables for the respective receivers. They may also be programmed to generate interrupts on either transition or used as simple inputs or outputs.

## zilog

### **Electrical Characteristics**

| Symbol                              | Description                                       | Min                | Мах   | Units |

|-------------------------------------|---------------------------------------------------|--------------------|-------|-------|

| V <sub>CC</sub>                     | Supply Voltage (*)                                | -0.3               | +7.0  | V     |

| T <sub>STG</sub>                    | Storage Temp.                                     | –65°               | +150° | С     |

| T <sub>A</sub>                      | Oper Ambient<br>Temp                              |                    | †     | С     |

|                                     | Power Dissipation                                 |                    | 2.2   | W     |

| *Voltage o<br><sup>†</sup> See Orde | n all pins with respect t<br>ering Information on | o GND.<br>page 97. |       |       |

#### Table 2. Absolute Maximum Ratings

Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; operation of the device at any condition above those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Standard Test Conditions**

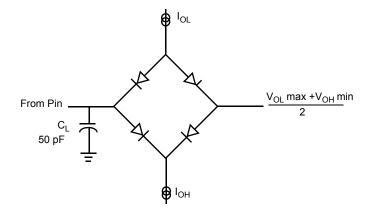

The DC Characteristics and Capacitance section below apply for the following standard test conditions, unless otherwise noted. All voltages are referenced to GND. Positive current flows into the referenced pin (Figure 5 on page 11). Standard conditions are as follows:

- $+4.5 \text{ V} < \text{V}_{\text{CC}} < +5.5 \text{ V}$

- GND = 0 V

- T<sub>A</sub> as specified in Ordering Information on page 97

Figure 5. Test Load Diagram

### Capacitance

#### Table 3. Capacitance

| Symbol           | Parameter                           | Min | Мах | Unit | Condition           |

|------------------|-------------------------------------|-----|-----|------|---------------------|

| C <sub>IN</sub>  | Input Capacitance                   |     | 10  | рF   | Unmeasured Pins     |

| C <sub>OUT</sub> | Output Capacitance                  |     | 15  | pF   | Returned to Ground. |

| CI/O             | Bidirectional Capacitance           |     | 20  | рF   |                     |

| Note: f = 1 MH   | Iz over specified temperature range |     |     |      |                     |

### **Miscellaneous**

Transistor Count: 174,000

### **Temperature Ratings**

Standard = 0 °C to  $\pm$ 70 °C Extended = -40 °C to +85 °C

## zilog <sub>12</sub>

### **DC Characteristics**

| Symbol                  | Parameter                         | Min                  | Тур         | Мах                  | Unit        | Condition                                                            |

|-------------------------|-----------------------------------|----------------------|-------------|----------------------|-------------|----------------------------------------------------------------------|

| V <sub>IH</sub>         | Input High Voltage                | 2.2                  |             | V <sub>CC</sub> +0.3 | V           |                                                                      |

| V <sub>IL</sub>         | Input Low Voltage                 | -0.3                 |             | 0.8                  | V           |                                                                      |

| V <sub>OH1</sub>        | Output High<br>Voltage            | 2.4                  |             |                      | V           | I <sub>OH</sub> = –1.6 mA                                            |

| V <sub>OH2</sub>        | Output High<br>Voltage            | V <sub>CC</sub> -0.8 |             |                      | V           | I <sub>OH</sub> = –250 μA                                            |

| V <sub>OL</sub>         | Output Low<br>Voltage             |                      |             | 0.4                  | V           | I <sub>OL</sub> = +2.0 mA                                            |

| IIL                     | Input Leakage                     |                      |             | ±10.00               | μA          | 0.4 < V <sub>IN</sub> < +2.4 V                                       |

| I <sub>OL</sub>         | Output Leakage                    |                      |             | ±10.00               | μA          | 0.4 < V <sub>OUT</sub> < +2.4 V                                      |

| I <sub>CCI</sub>        | V <sub>CC</sub> Supply<br>Current |                      | 7           | 50                   | mA          | V <sub>CC</sub> = 5 V V <sub>IH</sub> = 4.8 V V <sub>IL</sub> = 0.2V |

| Note: V <sub>CC</sub> = | 5 V ±10% unless other             | wise specifi         | ed, over sp | ecified temp         | erature ran | ge.                                                                  |

#### Table 4. Z16C30 DC Characteristics

### **AC Characteristics**

| Table 5. | Z16C30 | AC | Characteristics |

|----------|--------|----|-----------------|

|----------|--------|----|-----------------|

| No | Symbol    | Parameter                          | Min | Мах | Units | Note |

|----|-----------|------------------------------------|-----|-----|-------|------|

| 1  | Тсус      | Bus Cycle Time                     | 110 |     | ns    |      |

| 2  | TwASI     | AS Low Width                       | 30  |     | ns    |      |

| 3  | TwASh     | AS High Width                      | 60  |     | ns    |      |

| 4  | TwDSI     | DS Low Width                       | 60  |     | ns    |      |

| 5  | TwDSh     | DS High Width                      | 50  |     | ns    |      |

| 6  | TdAS(DS)  | AS Rise to DS Fall Delay<br>Time   | 5   |     | ns    |      |

| 7  | TdDS(AS)  | DS Rise to AS Fall Delay<br>Time   | 5   |     | ns    |      |

| 8  | TdDS(DRa) | DS Fall to Data Active Delay       | 0   |     | ns    |      |

| 9  | TdDS(DRv) | DS Fall to Data Valid Delay        |     | 60  | ns    |      |

| 10 | TdDS(DRn) | DS Rise to Data Not Valid<br>Delay | 0   |     | ns    |      |

| 11 | TdDS(DRz) | DS Rise to Data Float Delay        |     | 20  | ns    |      |

## zilog <sub>13</sub>

| No | Symbol     | Parameter                                                       | Min | Max | Units | Note |

|----|------------|-----------------------------------------------------------------|-----|-----|-------|------|

| 12 | TsCS(AS)   | CS to AS Rise Setup Time                                        | 15  |     | ns    |      |

| 13 | ThCS(AS)   | $\overline{\text{CS}}$ to $\overline{\text{AS}}$ Rise Hold Time | 5   |     | ns    |      |

| 14 | TsADD(AS)  | Direct Address to AS Rise<br>Setup Time                         | 15  |     | ns    | 1    |

| 15 | ThADD(AS)  | Direct Address to $\overline{\text{AS}}$ Rise<br>Hold Time      | 5   |     | ns    | 1    |

| 16 | TsSIA(AS)  | SITACK to AS Rise Setup<br>Time                                 | 15  |     | ns    |      |

| 17 | ThSIA(AS)  | SITACK to AS Rise Hold<br>Time                                  | 5   |     | ns    |      |

| 18 | TsAD(AS)   | Address to AS Rise Setup<br>Time                                | 15  |     | ns    |      |

| 19 | ThAD(AS)   | Address to $\overline{AS}$ Rise Hold Time                       | 5   |     | ns    |      |

| 20 | TsRW(DS)   | $R/W$ to $\overline{DS}$ Fall Setup Time                        | 0   |     | ns    |      |

| 21 | ThRW(DS)   | $R/\overline{W}$ to $\overline{DS}$ Fall Hold Time              | 25  |     | ns    |      |

| 22 | TsDSf(RRQ) | DS Fall to RxREQ Inactive Delay                                 |     | 60  | ns    | 4    |

| 23 | TdDSr(RRQ) | DS Rise to RxREQ Active Delay                                   | 0   |     | ns    |      |

| 24 | TsDW(DS)   | Write Data to $\overline{\text{DS}}$ Rise Setup Time            | 30  |     | ns    |      |

| 25 | ThDW(DS)   | Write Data to $\overline{\text{DS}}$ Rise Hold Time             | 0   |     | ns    |      |

| 26 | TdDSf(TRQ) | DS Fall to TxREQ Inactive Delay                                 |     | 65  | ns    | 5,6  |

| 27 | TdDSr(TRQ) | DS Rise to TxREQ Active Delay                                   | 0   |     | ns    |      |

| 28 | TwRDI      | RD Low Width                                                    | 60  |     | ns    |      |

| 29 | TwRDh      | RD High Width                                                   | 50  |     | ns    |      |

| 30 | TdAS(RD)   | AS Rise to RD Fall Delay<br>Time                                | 5   |     | ns    |      |

| 31 | TdRD(AS)   | RD Rise to AS Fall Delay Time                                   | 5   |     | ns    |      |

| 32 | TdRD(DRa)  | RD Fall to Data Active Delay                                    | 0   |     | ns    |      |

| 33 | TdRD(DRv)  | RD Fall to Data Valid Delay                                     |     | 60  | ns    |      |

| 34 | TdRD(DRn)  | RD Rise to Data Not Valid Delay                                 | 0   |     | ns    |      |

## zilog <sub>14</sub>

| No | Symbol     | Parameter                                                       | Min | Мах | Units | Note |

|----|------------|-----------------------------------------------------------------|-----|-----|-------|------|

| 35 | TdRD(DRz)  | RD Rise to Data Float Delay                                     |     | 20  | ns    |      |

| 36 | TdRDf(RRQ) | RD Fall to RxREQ Inactive Delay                                 |     | 60  | ns    | 4    |

| 37 | TdRDr(RRQ) | RD Rise to RxREQ Active Delay                                   | 0   |     | ns    |      |

| 38 | TwWRI      | WR Low Width                                                    | 60  |     | ns    |      |

| 39 | TwWRh      | WR High Width                                                   | 50  |     | ns    |      |

| 40 | TdAS(WR)   | AS Rise to WR Fall Delay                                        | 5   |     | ns    |      |

| 41 | TdWR(AS)   | WR Rise to AS Fall Delay<br>Time                                | 5   |     | ns    |      |

| 42 | TsDW(WR)   | Write Data to WR Rise Setup Time                                | 30  |     | ns    |      |

| 43 | ThDW(WR)   | Write Data to WR Rise Hold Time                                 | 0   |     | ns    |      |

| 44 | TdWRf(TRQ) | WR Fall to TxREQ Inactive Delay                                 |     | 65  | ns    | 5    |

| 45 | TdWRr(TRQ) | WR Rise to TxREQ Active Delay                                   | 0   |     | ns    |      |

| 46 | TsCS(DS)   | CS to DS Fall Setup Time                                        | 0   |     | ns    | 2    |

| 47 | ThCS(DS)   | $\overline{\text{CS}}$ to $\overline{\text{DS}}$ Fall Hold Time | 25  |     | ns    | 2    |

| 48 | TsADD(DS)  | Direct Address to DS Fall<br>Setup Time                         | 5   |     | ns    | 1,2  |

| 49 | ThADD(DS)  | Direct Address to $\overline{\text{DS}}$ Fall<br>Hold Time      | 25  |     | ns    | 1,2  |

| 50 | TsSIA(DS)  | SITACK to DS Fall Setup<br>Time                                 | 5   |     | ns    | 2    |

| 51 | ThSIA(DS)  | SITACK to DS Fall Hold Time                                     | 25  |     | ns    | 2    |

| 52 | TsCS(RD)   | CS to RD Fall Setup Time                                        | 0   |     | ns    | 2    |

| 53 | ThCS(RD)   | $\overline{\text{CS}}$ to $\overline{\text{RD}}$ Fall Hold Time | 25  |     | ns    | 2    |

| 54 | TsADD(RD)  | Direct Address to RD Fall<br>Setup Time                         | 5   |     | ns    | 1,2  |

| 55 | ThADD(RD)  | Direct Address to RD Fall<br>Hold Time                          | 25  |     | ns    | 1,2  |

| 56 | TsSIA(RD)  | SITACK to RD Fall Setup<br>Time                                 | 5   |     | ns    | 2    |

| 57 | ThSIA(RD)  | SITACK to RD Fall Hold Time                                     | 25  |     | ns    | 2    |

| 58 | TsCS(WR)   | CS to WR Fall Setup Time                                        | 0   |     | ns    | 2    |

## zilog <sub>15</sub>

| No | Symbol      | Parameter                              | Min | Мах | Units | Note |

|----|-------------|----------------------------------------|-----|-----|-------|------|

| 59 | ThCS(WR)    | CS to WR Fall Hold Time                | 25  |     | ns    | 2    |

| 60 | TsADD(WR)   | Direct Address to WR Fall Setup Time   | 5   |     | ns    | 1,2  |

| 61 | ThADD(WR)   | Direct Address to WR Fall<br>Hold Time | 25  |     | ns    | 1,2  |

| 62 | TsSIA(WR)   | SITACK to WR Fall Setup<br>Time        | 5   |     | ns    | 2    |

| 63 | ThSIA(WR)   | SITACK to WR Fall Hold<br>Time         | 25  |     | ns    | 2    |

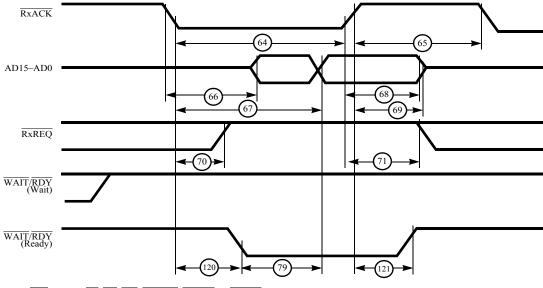

| 64 | TwRAKI      | RxACK Low Width                        | 60  |     | ns    |      |

| 65 | TwRAKh      | RxACK High Width                       | 50  |     | ns    |      |

| 66 | TdRAK(DRa)  | RxACK Fall to Data Active Delay        | 0   |     | ns    |      |

| 67 | TdRAK(DRv)  | RxACK Fall to Data Valid<br>Delay      |     | 60  | ns    |      |

| 68 | TdRAK(DRn)  | RxACK Rise to Data Not<br>Valid Delay  | 0   |     | ns    |      |

| 69 | TdRAK(DRz)  | RxACK Rise to Data Float<br>Delay      |     | 20  | ns    |      |

| 70 | TdRAKf(RRQ) | RxACK Fall to RxREQ                    |     | 60  | ns    | 4    |

| 71 | TdRAKr(RRQ) | RxACK Rise to RxREQ<br>Active Delay    | 0   |     | ns    |      |

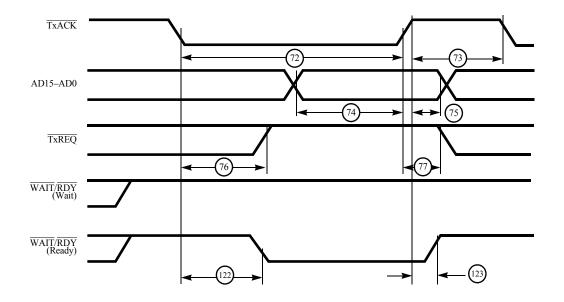

| 72 | TwTAKI      | TxACK Low Width                        | 60  |     | ns    |      |

| 73 | TwTAKh      | TxACK High Width                       | 50  |     | ns    |      |

| 74 | TsDW(TAK)   | Write Data to TxACK Rise<br>Setup Time | 30  |     | ns    |      |

| 75 | ThDW(TAK)   | Write Data to TxACK Rise<br>Hold Time  | 0   |     | ns    |      |

| 76 | TdTAKf(TRQ) | TxACK Fall to TxREQ<br>Inactive Delay  |     | 65  | ns    | 5    |

| 77 | TdTAKr(TRQ) | TxACK Rise to TxREQ Active Delay       | 0   |     | ns    |      |

| 78 | TdDSf(RDY)  | DS Fall (INTACK) to RDY Fall Delay     |     | 200 | ns    |      |

| 79 | TdRDY(DRv)  | RDY Fall to Data Valid Delay           |     | 40  | ns    |      |

| 80 | TdDSr(RDY)  | DS Rise to RDY Rise Delay              |     | 40  | ns    |      |

zilog <sub>16</sub>

| No  | Symbol     | Parameter                                 | Min | Мах | Units | Note |

|-----|------------|-------------------------------------------|-----|-----|-------|------|

| 81  | TsIEI(DSI) | IEI to DS Fall (INTACK)<br>Setup Time     | 10  |     | ns    |      |

| 82  | ThIEI(DSI) | IEI to DS Rise (INTACK) Hold<br>Time      | 0   |     | ns    |      |

| 83  | TdIEI(IEO) | IEI to IEO Delay                          |     | 30  | ns    |      |

| 84  | TdAS(IEO)  | AS Rise (Intack) to IEO Delay             | ,   | 60  | ns    |      |

| 85  | TdDSI(INT) | DS Fall (INTACK) to INT<br>Inactive Delay |     | 200 | ns    | 7    |

| 87  | TdDSI(Wr)  | DS Fall (INTACK) to WAIT<br>Rise Delay    |     | 200 | ns    |      |

| 88  | TdW(DRv)   | WAIT Rise to Data Valid<br>Delay          |     | 40  | ns    |      |

| 89  | TdRDf(RDY) | RD Fall (INTACK) to RDY<br>Fall Delay     |     | 200 | ns    |      |

| 90  | TdRDr(RDY) | RD Rise to RDY Rise Delay                 |     | 40  | ns    |      |

| 91  | TsIEI(RDI) | IEI to RD Fall (INTACK)<br>Setup Time     | 10  |     | ns    |      |

| 92  | ThIEI(RDI) | IEI to RD Rise (INTACK) Hold<br>Time      | 0   |     | ns    |      |

| 93  | TdRDI(INT) | RD Fall (INTACK) to INT<br>Inactive Delay |     | 200 | ns    |      |

| 94  | TdRDI(Wf)  | RD Fall (INTACK) to WAIT Fall Delay       |     | 40  | ns    |      |

| 95  | TdRDI(Wr)  | RD Fall (INTACK) to WAIT<br>Rise Delay    |     | 200 | ns    |      |

| 96  | TwPIAI     | PITACK Low Width                          | 60  |     | ns    |      |

| 97  | TwPIAh     | PITACK High Width                         | 50  |     | ns    |      |

| 98  | TdAS(PIA)  | AS Rise to PITACK Fall<br>Delay Time      | 5   |     | ns    |      |

| 99  | TdPIA(AS)  | PITACK Rise to AS Fall<br>Delay Time      | 5   |     | ns    |      |

| 100 | TdPIA(DRa) | PITACK Fall to Data Active Delay          | 0   |     | ns    |      |

| 101 | TdPIA(DRn) | PITACK Rise to Data Not<br>Valid Delay    | 0   |     | ns    |      |

| 102 | TdPIA(DRz) | PITACK Rise to Data Float<br>Delay        |     | 20  | ns    |      |

## zilog <sub>17</sub>

| No  | Symbol      | Parameter                            | Min | Мах | Units | Note |

|-----|-------------|--------------------------------------|-----|-----|-------|------|

| 103 | TsIEI(PIA)  | IEI to PITACK Fall Setup<br>Time     | 10  |     | ns    |      |

| 104 | ThIEI(PIA)  | IEI to PITACK Rise Hold<br>Time      | 0   |     | ns    |      |

| 105 | TdPIA(IEO)  | PITACK Fall to IEO Delay             |     | 60  | ns    |      |

| 106 | TdPIA(INT)  | PITACK Fall to INT Inactive Delay    |     | 200 | ns    |      |

| 107 | TdPIAf(RDY) | PITACK Fall to RDY Fall Delay        |     | 200 | ns    |      |

| 108 | TdPIAr(RDY) | PITACK Rise to RDY Rise<br>Delay     |     | 40  | ns    |      |

| 109 | TdPIA(Wf)   | PITACK Fall to WAIT Fall Delay       |     | 40  | ns    |      |

| 110 | TdPIA(Wr)   | PITACK Fall to WAIT Rise Delay       |     | 200 | ns    |      |

| 111 | TdSIA(INT)  | SITACK Fall to IEO Inactive<br>Delay |     | 200 | ns    | 2    |

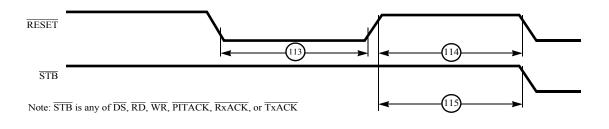

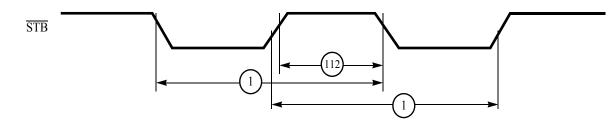

| 112 | TwSTBh      | Strobe High Width                    | 50  |     | ns    | 3    |

| 113 | TwRESI      | RESET Low Width                      | 170 |     | ns    |      |

| 114 | TwRESh      | RESET High Width                     | 60  |     | ns    |      |

| 115 | Tdres(STB)  | RESET Rise to STB Fall               | 60  |     | ns    | 3    |

| 116 | TdDSf(RDY)  | DS Fall to RDY Fall Delay            |     | 50  | ns    |      |

| 117 | TdWRf(RDY)  | WR Fall to RDY Fall Delay            |     | 50  | ns    |      |

| 118 | TdWRr(RDY)  | WR Rise to RDY Rise Delay            |     | 40  | ns    |      |

| 119 | TdRDf(RDY)  | RD Fall to RDY Fall Delay            |     | 50  | ns    |      |

| 120 | TdRAKf(RDY) | RxACK Fall to RDY Fall Delay         |     | 50  | ns    |      |

| 121 | TdRAKr(RDY) | RxACK Rise to RDY Rise Delay         |     | 40  | ns    |      |

| 122 | TdTAKf(RDY) | TxACK Fall to RDY Fall Delay         |     | 50  | ns    |      |

### zilog

#### Table 5. Z16C30 AC Characteristics (Continued)

| No    | Symbol      | Parameter                    | Min | Max | Units | Note |

|-------|-------------|------------------------------|-----|-----|-------|------|

| 123   | TdTAKr(RDY) | TxACK Rise to RDY Rise Delay |     | 40  | ns    |      |

| Notes |             |                              |     |     |       |      |

1. Direct address is any of A/B, D/C, or AD15–AD8 used as an address bus.

2. The parameter applies only when AS is not present.

3. Strobe (STB) is any of DS, RD, WR, PITACK, RXACK or TXACK.

4. Parameter applies only if read empties the receive FIFO.

5. Parameter applies only if write fills the transmit FIFO.

6. For extended temperature part TdDSI(Wf) max = 220 ns.

7. For extended temperature part TdDSF(TRQ) max = 75 ns.

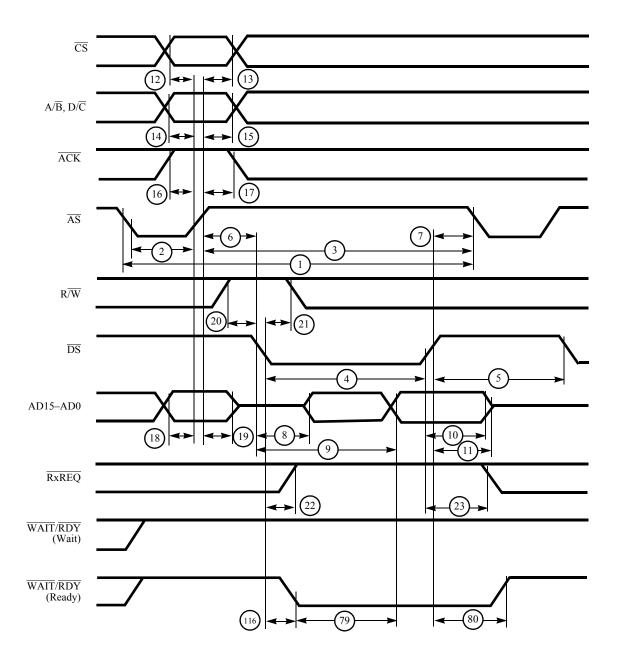

### **USC** Timing

The USC interface timing is similar to that found on a static RAM, except that it is much more flexible. Up to eight separate timing strobe signals may be present on the interface:  $\overline{DS}$ ,  $\overline{RD}$ ,  $\overline{WR}$ ,  $\overline{PITACK}$ ,  $\overline{RxACKA}$ ,  $\overline{RxACKB}$ ,  $\overline{TxACKA}$ , and  $\overline{TxACKB}$ . Only one of these timing strobes may be active at any time. Should the external logic activate more than one of these strobes at the same time the USC will enter a pre-reset state that is only exited by a hardware reset. Do not allow overlap of timing strobes. The timing diagrams beginning on the next page illustrate the different bus transactions possible with the necessary setup hold and delay times.

Figure 6. Reset Timing

Figure 7. Bus Cycle Timing

Note:  $\overline{\text{STB}}$  is any of  $\overline{\text{DS}}$ ,  $\overline{\text{RD}}$ ,  $\overline{\text{WR}}$ ,  $\overline{\text{PITACK}}$ ,  $\overline{\text{RxACK}}$ , or  $\overline{\text{TxACK}}$

Figure 8. DMA Read Cycle

Figure 9. DMA Write Cycle

Figure 10. Multiplexed DS Read Cycle