Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

**ZNEO32! Cortex-M3**

## Z32F0641 MCU

**Product Specification**

PS034404-0417

PRELIMINARY

ii

Warning: DO NOT USE THIS PRODUCT IN LIFE SUPPORT SYSTEMS.

#### LIFE SUPPORT POLICY

ZILOG'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF ZILOG CORPORATION.

#### As used herein

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

#### **Document Disclaimer**

©2017 Zilog, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZILOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. The information contained within this document has been verified according to the general principles of electrical and mechanical engineering.

ZNEO32! is a trademark or registered trademark of Zilog, Inc. All other product or service names are the property of their respective owners.

# Revision History

Each instance in this document's revision history reflects a change from its previous edition. For more details, refer to the corresponding page(s) or appropriate links furnished in the table below.

| Date        | Revision<br>Level | Description                                                         | Page |

|-------------|-------------------|---------------------------------------------------------------------|------|

| Apr<br>2017 | 04                | Updated part numbers to include the Cortex M identifier.            | All  |

| Aor<br>2016 | 03                | Added timing information for peripherals; global edits for clarity. | All  |

| Feb<br>2016 | 02                | Updated Figure 18.2 LQFP-32 Package Dimension.                      | 178  |

| Nov<br>2015 | 01                | Original issue.                                                     |      |

## 1. Overview

### Introduction

Zilog's Z32F0641 MCU, a member of the ZNEO32! Family of microcontrollers, is a cost-effective and high-performance 32-bit microcontroller. The Z32F0641 MCU provides a 3-phase PWM generator unit which is suitable for inverter bridges, including motor drive systems.

Two 12-bit high speed ADC units with 16-channel analog multiplexed inputs support feedback retrieval from the inverter bridge. Multiple powerful external serial interfaces help communicate with on-board sensors and devices.

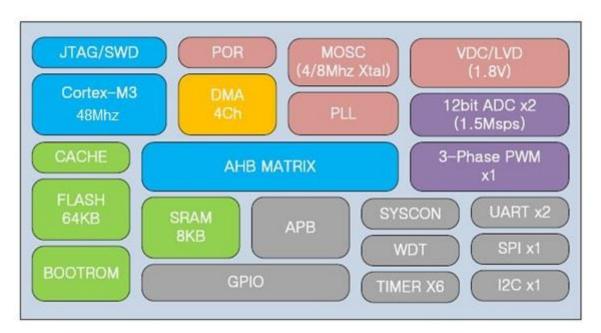

Figure 1.1 shows a block diagram of the Z32F0641 MCU.

Figure 1.1 Block Diagram

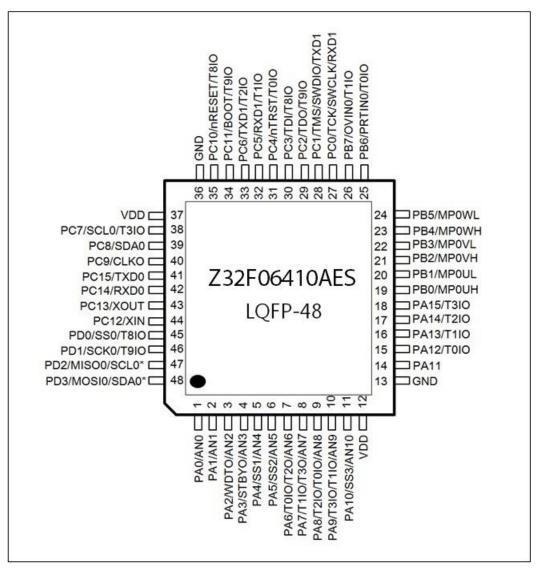

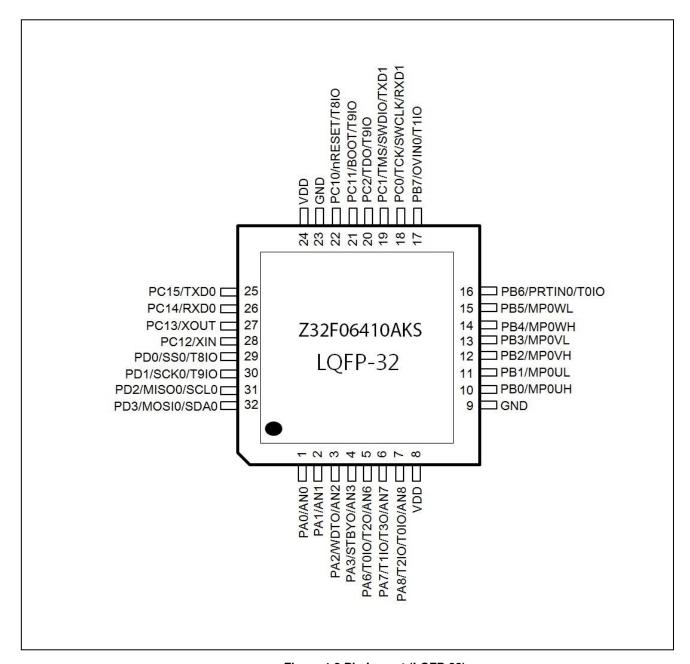

Figure 1.2 and Figure 1.3 show the pin layouts.

Figure 1.2 Pin Layout (LQFP-48)

Figure 1.3 Pin Layout (LQFP-32)

### **Product Features**

The Z32F0641 MCU offers the following features:

- High Performance low-power Cortex-M3 core

- 64 KB code Flash memory with cache function

- 8 KB SRAM

- 3-Phase PWM with ADC triggering function

- 1.5Msps high-speed ADC with sequential conversion function

- 2 units with 11 channel Inputs

- Watchdog timer

- Six general purpose timers

- o Periodic, One-shot, PWM, Capture mode

- Multi-timer synchronization option

- External communication ports:

- o 2 UARTs

- $\circ$  1  $I^2C$

- o 1 SPI

- Direct Memory Access (DMA) controller with 4 channels

- System fail-safe function by clock monitoring

- XTAL OSC fail monitoring

- Debug and emergency stop function

- Serial Wire Debug (SWD) and JTAG Debugger (JTAG is only for LQFP-48)

- Supports UART and SPI ISP

- Two types of package options

- o LQFP-48 (0.5mm pitch)

- LQFP-32 (0.65mm pitch)

- Industrial grade operating temperature (-40 ~ +85 °C)

Table 1.1 Device Type

| Part Number  | Flash | SRAM | UART | SPI | I2C | MPWM | ADC             | I/O Ports | Package |

|--------------|-------|------|------|-----|-----|------|-----------------|-----------|---------|

| Z32F06410AES | 64KB  | 8KB  | 2    | 1   | 1   | 1    | 2-unit<br>11 ch | 44        | LQFP-48 |

| Z32F06410AKS | 64KB  | 8KB  | 2    | 1   | 1   | 1    | 2-unit<br>8 ch  | 30        | LQFP-32 |

### **Architecture**

### **Block Diagram**

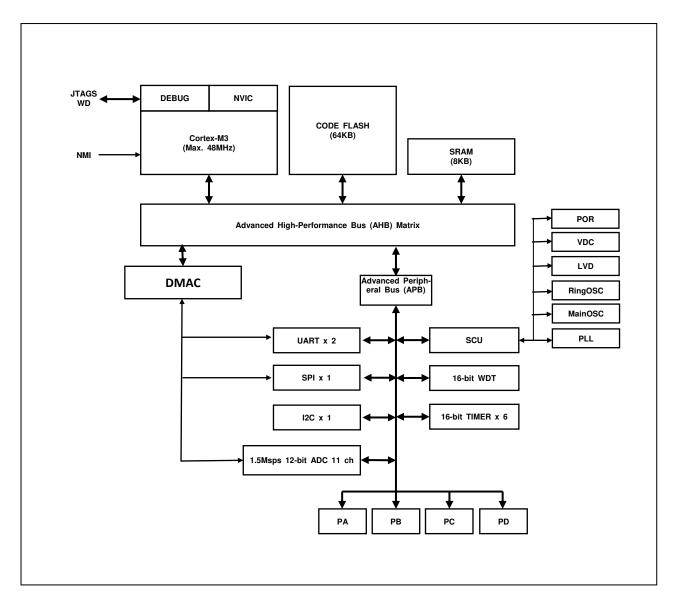

An internal block diagram of the Z32F0641 MCU is shown in Figure 1.4.

Figure 1.4 Internal Block Diagram

### **Functional Description**

The following section provides an overview of the features of the Z32F0641 microcontroller.

#### **ARM Cortex-M3**

- ARM-powered Cortex-M3 core based on ARMv7M architecture, which is optimized for small-size and low-power systems. On core system timer (SYSTICK) provides a simple 24-bit timer that enables easy management of system operations

- Thumb-compatible Thumb-2 only instruction set processor core makes code high-density

- Hardware division and single-cycle multiplication

- Integrated Nested Vectored Interrupt Controller (NVIC) provides deterministic interrupt handling

- JTAG and SWD debugging features

- Maximum 48 MHz operating frequency with zero wait execution

#### **Nested Vector-Interrupt Controller (NVIC)**

- The ARM Nested Vectored Interrupt Controller (NVIC) on the ARM Cortex-M3 core handles all

internal and external exceptions. When an interrupt condition is detected, the processor state is

automatically stored to the stack and automatically restored from the stack at the end of interrupt

service routine.

- The vector is fetched in parallel to the state saving, which enables efficient interrupt entry.

- The processor supports tail-chaining, which allows for back-to-back interrupts to be performed without the overhead of state saving and restoring

#### 64 KB Internal Code Flash Memory

- The Z32F0641 MCU provides internal 64 KB code Flash memory and its controller, which is sufficient to program the motor algorithm and control the system. Self-programming is available and ISP and JTAG programming is also supported in boot or debugging mode.

- Instruction and data cache buffer are present and overcome the low-bandwidth Flash memory. The CPU can execute from Flash memory with zero wait state up to 48 MHz bus frequency.

#### 8 KB 0-wait Internal SRAM

On chip 8 KB 0-wait SRAM can be used for working memory space and program code can be loaded on this SRAM

#### **Boot Logic**

• Smart boot logic supports Flash programming. The Z32F0641 MCU can be accessed by an external boot pin; UART and SPI programming are available in Boot Mode

#### **System Control Unit**

• The System Control Unit (SCU) block manages internal power, clock, reset, and Operation Mode. The SCU also controls analog blocks (Oscillator Block, VDC and LVD)

#### 32-bit Watchdog Timer

• The Watchdog Timer (WDT) performs the system monitoring function. The WDT generates an internal reset or interrupt if the system is in abnormal state

#### Multi-purpose 16-bit Timer

- Six-channel 16-bit general purpose timers support the following functions

- Periodic timer mode

- Counter mode

- PWM mode

- Capture mode

Built-in timer also supports counter-synchronization mode which can generate synchronized waves and timing

#### **Motor PWM Generator**

- 3-phase Motor PWM Generator is implemented. 16-bit up/down counter with prescaler supports triangular and saw tooth waveforms

- PWM has the ability to generate internal ADC trigger signals to measure the signal on time

- Dead time insertion and emergency stop functionality provide overcurrent protection for the chip and system

#### **Serial Peripheral Interface (SPI)**

- The Serial Peripheral Interface (SPI) block provides synchronous serial communication. The Z32F0641 MCU has 1 channel SPI module which includes the DMA function supported by a DMA controller. Transfer data is moved to/from the memory area without CPU operation

- Boot Mode uses this SPI block to download the Flash program

#### **Inter-Integrated Circuit Interface**

The Z32F0641 MCU has 1 channel Inter-Integrated Circuit (I<sup>2</sup>C) block which supports up to 400 kHz I<sup>2</sup>C communication. Master and slave modes are supported

#### **Universal Asynchronous Receiver/Transmitter**

- The Z32F0641 MCU has 2 channels Universal Asynchronous Receiver/Transmitter (UART) block. For accurate baud rate control, the fractional baud rate generator is provided

- The UART features the DMA function, supported by a DMA controller. Transfer data is moved to/from the memory area without CPU operation

#### General PORT I/Os

- 16-bit PA, PB, PC, and PD ports are available and provide multiple functionality:

- o General I/O port

- Independent bit set/clear function

- External interrupt input port

- Programmable pull-up and open-drain selection

- On-chip input debounce filter

#### 12-bit Analog-to-Digital Converter (ADC)

- 2 built-in Analog-to-Digital Converters (ADC) can convert analog signals up to 1.5 Msps conversion rate. 11-channel analog MUX provides various combinations from external analog signals.

- The ADC features the DMA function, supported by a DMA controller. Transfer data is moved to/from the memory area without CPU operation.

# **Pin Description**

Pin configurations are listed in Table 1.2.

Table 1.2 Pin Description

| Pin Name |        | Pin Name Type |        | Description                    | Remark |

|----------|--------|---------------|--------|--------------------------------|--------|

| LQFP48   | LQFP32 | riii Naille   | туре   | Description                    | nemark |

| 1        | 1      | PA0*          | IOUS   | PORT A Bit 0 Input/Output      |        |

| !        | '      | AN0           | IA     | Analog Input 0                 |        |

| 2        | 2 PA1* |               | IOUS   | PORT A Bit 1 Input/Output      |        |

| ۷        | 2      | AN1           | IA     | Analog Input1                  |        |

|          |        | PA2*          | IOUS   | PORT A Bit 2 Input/Output      |        |

| 3        | 3      | WDTO          | 0      | Watchdog timer overflow output |        |

|          |        | AN2           | IA     | Comparator 2 Input             |        |

| 4        | 4      | PA3*          | IOUS   | PORT A Bit 3 Input/Output      |        |

| 4        | 4      | AN3           | IA     | Analog Input 3                 |        |

|          |        | PA4*          | IOUS   | PORT A Bit 4 Input/Output      |        |

| 5        | -      | SS1           | I/O    | Slave Select 1 for SPI0        |        |

|          |        | AN4           | IA     | Analog Input 4                 |        |

|          |        | PA5*          | IOUS   | PORT A Bit 5 Input/Output      |        |

| 6        | -      | SS2           | I/O    | Slave Select 2 for SPI0        |        |

|          |        | AN5           | IA     | Analog Input 5                 |        |

|          |        | PA6*          | IOUS   | PORT A Bit 6 Input/Output      |        |

| 7        | 5      | T0IO          | I/O    | Timer 0 Input/Output           |        |

| /        | 5      | T2IO          | I/O    | Timer 2 Input/Output           |        |

|          |        | AN6           | IA     | Analog Input 6                 |        |

|          |        | PA7*          | IOUS   | PORT A Bit 7 Input/Output      |        |

| 8        | 6      | T1IO          | I/O    | Timer 1 Input/Output           |        |

| 0        | 0      | T3IO          | I/O    | Timer 3 Input/Output           |        |

|          |        | AN7           | IA     | Analog Input 7                 |        |

|          |        | PA8*          | IOUS   | PORT A Bit 8 Input/Output      |        |

| 0        | 7      | T2IO          | I/O    | Timer 2 Input/Output           |        |

| 9        | /      | T0IO          | I/O    | Timer 0 Input/Output           |        |

|          |        | AN8           | IA     | Analog Input 8                 |        |

|          |        | PA9*          | IOUS   | PORT A Bit 9 Input/Output      |        |

| 10       |        | T3IO          | I/O    | Timer 3 Input/Output           |        |

| 10       | -      | T1IO          | I/O    | Timer 1 Input/Output           |        |

|          |        | AN9           | IA     | Analog Input 9                 |        |

|          |        | PA10*         | IOUS   | PORT A Bit 10 Input/Output     |        |

| 11       | -      | SS3           | Output | ETM Trace Data 1               |        |

|          |        | AN10          | IA     | Analog Input 10                |        |

| 12       | 8      | VDD           | Р      | VDD                            |        |

| 13       | 9      | GND           | Р      | Ground                         |        |

| 14       | -      | PA11*         | IOUS   | PORT A Bit 11 Input/Output     |        |

|          |        | PA12*         | IOUS   | PORT A Bit 12 Input/Output     |        |

| 15       | _      | TOIO          | I/O    | Timer 0 Input/Output           |        |

| 10       |        | 1000          | 1,0    | Timor o input/output           |        |

|          |        |               |        |                                |        |

|    |    | PA13*         | IOUS   | PORT A Bit 13 Input/Output            |  |

|----|----|---------------|--------|---------------------------------------|--|

| 16 | _  | T1IO          | I/O    | Timer 1 Input/Output                  |  |

|    |    |               |        |                                       |  |

|    |    | PA14*         | IOUS   | PORT A Bit 14 Input/Output            |  |

| 17 | _  | T2IO          | I/O    | Timer 2 Input/Output                  |  |

|    |    | -             |        | 1,22,23,42,2                          |  |

|    |    | PA15*         | IOUS   | PORT A Bit 15 Input/Output            |  |

| 18 | _  | T3IO          | I/O    | Timer 3 Input/Output                  |  |

|    |    |               |        |                                       |  |

|    |    | PB0           | IOUS   | PORT B Bit 0 Input/Output             |  |

| 19 | 10 | PWM0UH        | Output | PWM0 UH Output                        |  |

| -  |    | PB1           | IOUS   | PORT B Bit 1 Input/Output             |  |

| 20 | 11 | PWM0UL        | Output | PWM0 UL Output                        |  |

| -  |    | PB2           | IOUS   | PORT B Bit 0 Input/Output             |  |

| 21 | 12 | PWM0VH        | Output | PWM0 VH Output                        |  |

|    |    | PB3           | IOUS   | PORT B Bit 1 Input/Output             |  |

| 22 | 13 | PWM0VL        | Output | PWM0 VL Output                        |  |

|    |    | PB4           | IOUS   | PORT B Bit 4 Input/Output             |  |

| 23 | 14 | PWM0WH        | Output | PWM0 WH Output                        |  |

| -  |    | PB5           | IOUS   | PORT B Bit 5 Input/Output             |  |

| 24 | 15 | PWM0WL        | Output | PWM0 WL Output                        |  |

|    |    | PB6           | IOUS   | PORT B Bit 6 Input/Output             |  |

| 25 | 16 | PRTIN0        | Input  | PWM0 Protection Input signal 0        |  |

| _0 |    | TOIO          | I/O    | Timer 0 Input/Output                  |  |

| -  |    | PB7           | IOUS   | PORT B Bit 7 Input/Output             |  |

| 26 | 17 | OVIN0         | Input  | PWM0 Over-voltage input signal 0      |  |

| _0 | '' | T1IO          | I/O    | Timer 1 Input/Output                  |  |

|    |    | PC0           | IOUS   | PORT C Bit 0 Input/Output             |  |

|    |    | TCK/SWC       |        | · · · · · · · · · · · · · · · · · · · |  |

| 27 | 18 | K             | Input  | JTAG TCK, SWD Clock Input             |  |

|    |    | RXD1          | Input  | UART0 Rx Data Input                   |  |

|    |    | PC1           | IOUS   | PORT C Bit 1 Input/Output             |  |

| 28 | 19 | TMS/SWDI<br>O | I/O    | JTAG TMS, SWD Data Input/Output       |  |

|    |    | TXD1          | Input  | UART0 Tx Data Output                  |  |

| -  |    | PC2           | IOUS   | PORT C Bit 2 Input/Output             |  |

| 29 | 20 | TDO/SWO       | Output | JTAG TDO, SWO Output                  |  |

|    |    | T8IO          | I/O    | Timer 8 Input/Output                  |  |

|    |    | PC3           | IOUS   | PORT C Bit 3 Input/Output             |  |

| 30 | -  | TDI           | Input  | JTAG TDI Input                        |  |

|    |    | T9IO          | I/O    | Timer 9 Input/Output                  |  |

|    |    | PC4           | IOUS   | PORT C Bit 4 Input/Output             |  |

| 31 | -  | nTRST         | Input  | JTAG nTRST Input                      |  |

|    |    | TOIO          | Input  | Timer 0 input/Output                  |  |

|    |    | PC5           | IOUS   | PORT C Bit 5 Input/Output             |  |

| 32 | -  | RXD1          | Input  | UART1 RXD Input                       |  |

|    |    | T1IO          | I/O    | Timer 1 input/Output                  |  |

|    |    | PC6           | IOUS   | PORT C Bit 6 Input/Output             |  |

| 33 | -  | TXD1          | Output | UART1 TXD Output                      |  |

| _  |    | ı             | •      | ·                                     |  |

|    |    | T2IO   | I/O    | Timer 2 input/Output                  |         |

|----|----|--------|--------|---------------------------------------|---------|

| _  |    | PC11   | IOUS   | PORT C Bit 11 Input/Output            |         |

| 34 | 21 | BOOT   | Input  | Boot mode Selection Input             |         |

|    |    | T9IO   | I/O    | Timer 9 input/Output                  |         |

|    |    | PC10   | IOUS   | PORT C Bit 10 Input/Output            |         |

| 35 | 22 | nRESET | Input  | External Reset Input                  | Pull-up |

|    |    | T8IO   | I/O    | Timer 8 input/Output                  |         |

| 36 | 23 | GND    | Р      | Ground                                |         |

| 37 | 24 | VDD    | Р      | VDD                                   |         |

|    |    | PC7    | IOUS   | PORT C Bit 7 Input/Output             |         |

| 38 | -  | SCL0   | Output | I <sup>2</sup> C Channel 0 SCL In/Out |         |

|    |    | T3IO   | I/O    | Timer 3 input/Output                  |         |

|    |    | PC8    | IOUS   | PORT C Bit 8Input/Output              |         |

| 39 | -  | SDA0   | Output | I <sup>2</sup> C Channel 0 SDA In/Out |         |

| 40 |    | PC9    | IOUS   | PORT C Bit 9 Input/Output             |         |

| 40 | -  | CLKO   | Output | System Clock Output                   |         |

|    |    | PC15   | IOUS   | PORT C Bit 14 Input/Output            |         |

| 41 | 25 | TXD0   | Output | UART0 TXD Output                      |         |

|    |    | MISO0  | I/O    | SPI0 Master-Input/Slave-Output        |         |

|    |    | PC14   | IOUS   | PORT C Bit 14 Input/Output            |         |

| 42 | 26 | RXD0   | Input  | UART0 RXD Input                       |         |

|    |    | MOSI0  | I/O    | SPI0 Master-Output/Slave-Input        |         |

| 43 | 27 | PC13   | IOUS   | PORT C Bit 13 Input/Output            |         |

| 43 | 21 | XOUT   | OA     | External Crystal Oscillator Output    |         |

| 44 | 28 | PC12   | IOUS   | PORT C Bit 12 Input/Output            |         |

| 44 | 20 | XIN    | IA     | External Crystal Oscillator Input     |         |

|    |    | PD0    | IOUS   | PORT D Bit 0 Input/Output             |         |

| 45 | 29 | SS0    | I/O    | SPI1 Slave Select                     |         |

|    |    | T8IO   | I/O    | Timer 8 input/Output                  |         |

|    |    | PD1    | IOUS   | PORT D Bit 1 Input/Output             |         |

| 46 | 30 | SCK0   | I/O    | SPI0 Clock Input/Output               |         |

|    |    | T9IO   | I/O    | Timer 9 input/Output                  |         |

|    |    | PD2    | IOUS   | PORT D Bit 2 Input/Output             |         |

| 47 | 31 | MISO0  | I/O    | SPI Channel 0 Master In / Slave Out   |         |

|    |    | SCL0   | Output | I <sup>2</sup> C Channel 0 SCL In/Out |         |

|    |    | PD3*   | IOUS   | PORT D Bit 3 Input/Output             |         |

| 48 | 32 | MOSI0  | I/O    | SPI Channel 0 Master Out / Slave In   |         |

|    |    | SDA0   | Output | I <sup>2</sup> C Channel 0 SDA In/Out |         |

#### \*Notation:

I=Input, O=Output, U=Pull-up, D=Pull-down,

S=Schmitt-Trigger Input Type, C=CMOS Input Type, A=Analog, P=Power

(\*) Selected pin function after reset condition

Pin order may be changed with revision notice.

# Memory Map

| Address                                   | Memories mapped                           |

|-------------------------------------------|-------------------------------------------|

| 0x0000_0000                               | FLASH ROM (64KB)                          |

| 0x0000_FFFF<br>0x0001_0000                | RESERVED                                  |

| 0x0001_FFFF<br>0x0002_0000                | RESERVED                                  |

| 0x1FFE_FFFF<br>0x1FFF_0000                | BOOT ROM (2KB)                            |

| 0x1FFF_07FF<br>0x1FFF_0800                | RESERVED                                  |

| 0x1FFF_FFFF<br>0x2000_0000                | SRAM (8KB)                                |

| 0x2000_1FFF<br>0x2000_2000                | RESERVED                                  |

| 0x2FFF_FFFF<br>0x3000_0000                | FLASH ROM Mirrored (64KB)                 |

| 0x3000_FFFF<br>0x3001_0000                | RESERVED                                  |

| 0x3001_FFFF<br>0x3002_0000                | BOOT ROM (2KB)<br>Mirror                  |

| 0x3002_07FF<br>0x3003_0000                | OTP Mirror                                |

| 0x3003_07FF<br>0x3004_0000                | RESERVED                                  |

| 0x3FFF_FFFF<br>0x4000_0000                | PERIPHERALS                               |

| 0x4000_FFFF<br>0x4001 0000                | RESERVED                                  |

| 0x5FFF_FFFF<br>0x6000 0000                | External RAM (Not support)                |

| 0x9FFF_FFFF<br>0xA000_0000                | External DEVICE(Not support)              |

| 0xDFFF_FFFF<br>0xE000_0000                | Private peripheral bus:<br>Internal       |

| 0xE003_FFFF<br>0xE004_0000                | Private peripheral bus:<br>Debug/External |

| 0xE00F_FFFF<br>0xE010_0000<br>0xFFFF_FFFF | Vendor Specific                           |

Figure 1.5 Main Memory Map

| Address                                   | Peripherals mapped |  |

|-------------------------------------------|--------------------|--|

| 0x4000_0000                               | SCU                |  |

| 0x4000_00FF<br>0x4000_0100                | FMC                |  |

| 0x4000_01FF<br>0x4000_0200                | WDT                |  |

| 0x4000_02FF<br>0x4000_0300                | Reserved           |  |

| 0x4000_03FF<br>0x4000_0400                | DMAC               |  |

| 0x4000_04FF<br>0x4000_0500                | Reserved           |  |

| 0x4000_05FF<br>0x4000_0600                | Reserved           |  |

| 0x4000_0FFF<br>0x4000_1000                | PCU                |  |

| 0x4000_1FFF<br>0x4000_2000                | GPIO               |  |

| 0x4000_2FFF<br>0x4000_3000                | TIMER              |  |

| 0x4000_3FFF<br>0x4000_4000                | MPWM0              |  |

| 0x4000_4FFF<br>0x4000_5000                | Reserved           |  |

| 0x4000_7FFF<br>0x4000_8000                | UART0              |  |

| 0x4000_80FF<br>0x4000_8100                | UART1              |  |

| 0x4000_81FF<br>0x4000_8200                | Reserved           |  |

| 0x4000_8FFF<br>0x4000_9000                | SPI0               |  |

| 0x4000_90FF<br>0x4000_9100                | Reserved           |  |

| 0x4000_9FFF<br>0x4000_A000                | I2C0               |  |

| 0x4000_A0FF<br>0x4000_A100                | Reserved           |  |

| 0x4000_AFFF<br>0x4000_B000                | ADC0               |  |

| 0x4000_B0FF<br>0x4000_B100                | ADC1               |  |

| 0x4000_B1FF<br>0x4000_B200<br>0x4000_FFFF | Reserved           |  |

Figure 1.6 Peripheral Memory Map

| Address     | Core Memory Map |

|-------------|-----------------|

| 0xE000_0000 | ITM             |

| 0xE000_0FFF |                 |

| 0xE000_1000 | DWT             |

| 0xE000_1FFF |                 |

| 0xE000_2000 | FPB             |

| 0xE000_2FFF |                 |

| 0xE000_3000 | Reserved        |

| 0xE000_DFFF |                 |

| 0xE000_E000 | System Control  |

| 0xE000_EFFF | •               |

| 0xE000_F000 | Reserved        |

| 0xE003_FFFF |                 |

| 0xE004_0000 | TPIU            |

| 0xE004_0FFF |                 |

| 0xE004_1000 | ETM             |

| 0xE004_1FFF |                 |

| 0xE004_2000 |                 |

| 0xE00F_EFFF | External PPB    |

| 0xE00F F000 | DOM T. I.I      |

| _           | ROM Table       |

| 0xE00F_FFFF |                 |

Figure 1.7 Cortex-M3 Private Memory Map

**Note:** Refer to document number DDI337 from ARM for more information about the memory maps.

## 2. CPU

### **Cortex-M3 Core**

The CPU core is supported by the ARM Cortex-M3 processor which provides a high-performance, low-cost platform. Document number DDI337 from ARM provides more information about Cortex-M3.

## **Interrupt Controller**

**Table 2.1 Interrupt Vector Map**

| Priority | Vector Address | Interrupt Source          |

|----------|----------------|---------------------------|

| -16      | 0x0000_0000    | Stack Pointer             |

| -15      | 0x0000_0004    | Reset Address             |

| -14      | 0x0000_0008    | NMI Handler               |

| -13      | 0x0000_000C    | Hard Fault Handler        |

| -12      | 0x0000_0010    | MPU Fault Handler         |

| -11      | 0x0000_0014    | BUS Fault Handler         |

| -10      | 0x0000_0018    | Usage Fault Handler       |

| -9       | 0x0000_001C    | Reserved                  |

| -8       | 0x0000_0020    | Reserved                  |

| -7       | 0x0000_0024    | Reserved                  |

| -6       | 0x0000_0028    | Reserved                  |

| -5       | 0x0000_002C    | SVCall Handler            |

| -4       | 0x0000_0030    | Debug Monitor Handle<br>r |

| -3       | 0x0000_0034    | Reserved                  |

| -2       | 0x0000_0038    | PenSV Handler             |

| -1       | 0x0000_003C    | SysTick Handler           |

| 0        | 0x0000_0040    | LVDDETECT                 |

| 1        | 0x0000_0044    | SYSCLKFAIL                |

| 2        | 0x0000_0048    | XOSCFAIL                  |

| 3        | 0x0000_004C    | WDT                       |

| 4        | 0x0000_0050    | Reserved                  |

| 5        | 0x0000_0054    | TIMER0                    |

| 6        | 0x0000_0058    | TIMER1                    |

| 7        | 0x0000_005C    | TIMER2                    |

| 8        | 0x0000_0060    | TIMER3                    |

| 9        | 0x0000_0064    | Reserved                  |

| 10       | 0x0000_0068    | Reserved                  |

| 11       | 0x0000_006C    | Reserved                  |

| 12       | 0x0000_0070    | Reserved                  |

| 13       | 0x0000_0074    | TIMER8                    |

| 14       | 0x0000_0078    | TIMER9                    |

| 15       | 0x0000_007C    | Reserved                  |

| 16       | 0x0000_0080    | GPIOAE                    |

| 17       | 0x0000_0084    | GPIOAO                    |

| 18       | 0x0000_0088    | GPIOBE                    |

| 19 | 0x0000 008C | GPIOBO    |

|----|-------------|-----------|

| 20 | 0x0000_0090 | GPIOCE    |

| 21 | 0x0000_0094 | GPIOCO    |

| 22 | 0x0000_0098 | GPIODE    |

| 23 | 0x0000_009C | GPIODO    |

| 24 | 0x0000_00A0 | MPWM0     |

| 25 | 0x0000_00A4 | MPWM0PROT |

| 26 | 0x0000_00A8 | MPWM0OVV  |

| 27 | 0x0000_00AC | Reserved  |

| 28 | 0x0000_00B0 | Reserved  |

| 29 | 0x0000_00B4 | Reserved  |

| 30 | 0x0000_00B8 | Reserved  |

| 31 | 0x0000_00BC | Reserved  |

| 32 | 0x0000_00C0 | SPI0      |

| 33 | 0x0000_00C4 | Reserved  |

| 34 | 0x0000_00C8 | Reserved  |

| 35 | 0x0000_00CC | Reserved  |

| 36 | 0x0000_00D0 | I2C0      |

| 37 | 0x0000_00D4 | Reserved  |

| 38 | 0x0000_00D8 | UART0     |

| 39 | 0x0000_00DC | UART1     |

| 40 | 0x0000_00E0 | Reserved  |

| 41 | 0x0000_00E4 | Reserved  |

| 42 | 0x0000_00E8 | Reserved  |

| 43 | 0x0000_00EC | ADC0      |

| 44 | 0x0000_00F0 | ADC1      |

| 45 | 0x0000_00F4 | Reserved  |

| 46 | 0x0000_00F8 | Reserved  |

| 47 | 0x0000_00FC | Reserved  |

| 48 | 0x0000_0100 | Reserved  |

| 49 | 0x0000_0104 | Reserved  |

| 50 | 0x0000_0108 | Reserved  |

| 51 | 0x0000_010C | Reserved  |

| 52 | 0x0000_0110 | Reserved  |

| 53 | 0x0000_0114 | Reserved  |

| 54 | 0x0000_0118 | Reserved  |

| 55 | 0x0000_011C | Reserved  |

| 56 | 0x0000_0120 | Reserved  |

| 57 | 0x0000_0124 | Reserved  |

| 58 | 0x0000_0128 | Reserved  |

| 59 | 0x0000_012C | Reserved  |

| 60 | 0x0000_0130 | Reserved  |

| 61 | 0x0000_0134 | Reserved  |

| 62 | 0x0000_0138 | Reserved  |

| 63 | 0x0000_013C | Reserved  |

## 3. Boot Mode

### **Boot Mode Pins**

The Z32F0641 MCU includes a Boot Mode option to program internal Flash memory. To enter Boot Mode, set the BOOT pin to **Low** at reset timing.

Note: The Normal state of the BOOT pin is High.

Boot Mode supports UART boot and SPI boot.UART boot uses the UART0 port, and SPI boot uses SPI0.The pins used for Boot Mode are listed in Table 3.1.

| Block   | Pin Name    | Dir | Description             |  |  |

|---------|-------------|-----|-------------------------|--|--|

| SYSTEM  | nRESET/PC10 | I   | Reset Input signal      |  |  |

| SISILIM | BOOT/PC11   | I   | '0' to enter Boot mode  |  |  |

| UART0   | RXD0/PC14   | I   | UART Boot Receive Data  |  |  |

| UANTU   | TXD0/PC15   | 0   | UART Boot Transmit Data |  |  |

|         | SS0/PA12    | I   | SPI Boot Slave Select   |  |  |

| SPI0    | SCK0/PA13   | I   | SPI Boot Clock Input    |  |  |

|         | MOSI0/PA14  | I   | SPI Boot Data Input     |  |  |

|         | MISO0/PA15  | 0   | SPI Boot Data Output    |  |  |

Table 3.1 Boot Mode Pins

### **Boot Mode Connections**

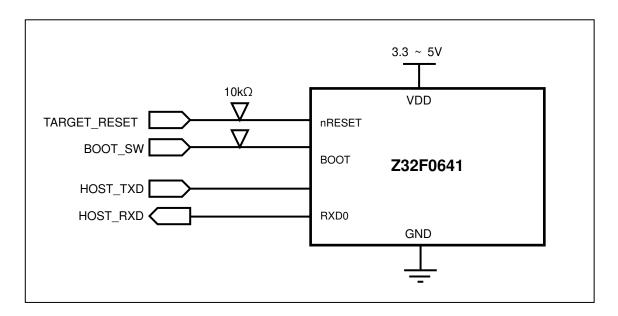

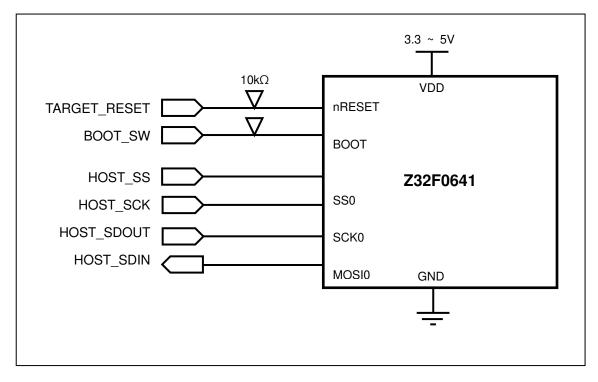

Design the target board using either of the Boot Mode ports – UART or SPI. Figure 3.1 and Figure 3.2 display sample Boot Mode connections.

Figure 3.1 UART Boot Connection Diagram

Figure 3.2 SPI Boot Connection Diagram

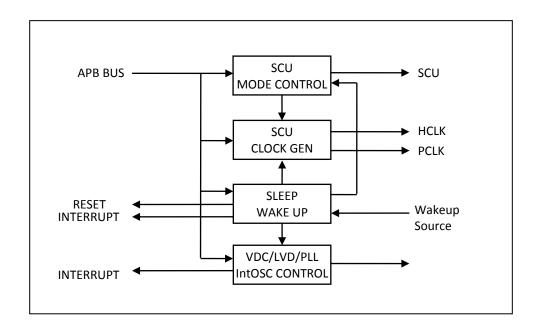

# 4. System Control Unit

### **Overview**

The Z32F0641 microcontroller has an in-built intelligent power control block which manages the system analog blocks and operating modes. Internal reset and clock signals are controlled by the SCU block to maintain optimal system performance and power dissipation.

Figure 4.1 SCU Block Diagram

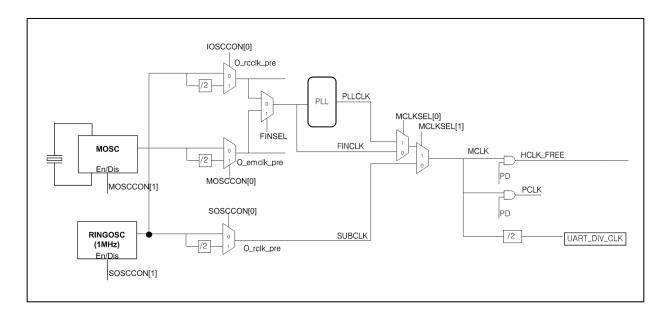

## **Clock System**

The Z32F0641 MCU has the following two main operating clocks:

HCLK - Clock for the CPU and AHB bus system

PCLK - Clock for peripheral systems

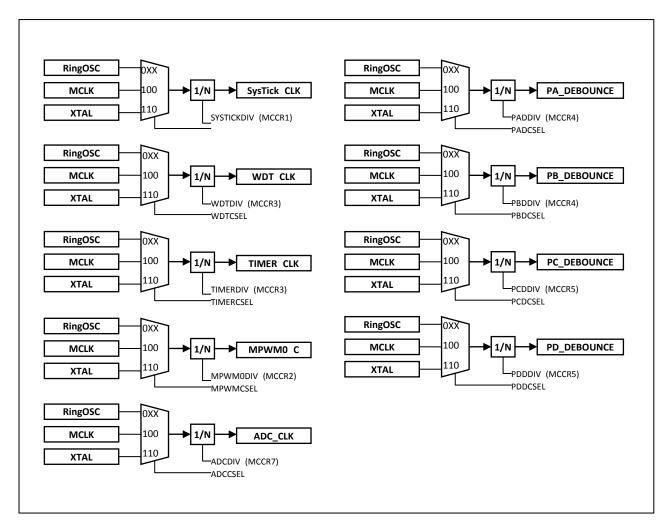

Figure 4.2 and Figure 4.3 show the chip's clock system. Table 4.1 lists the clock source descriptions.

**Figure 4.2 Clock Source Configuration**

Figure 4.3 System Clock Configuration

Each of the multiplexers for switching the clock source contains a circuit which allows glitch-free switching between clock modes.

**Table 4.1 Clock Sources**

| Clock name | Frequency       | Description           |

|------------|-----------------|-----------------------|

| MainOSC    | XTAL(4MHz~8MHz) | External Crystal IOSC |

| PLL Clock  | 8MHz ~ 80MHz    | On Chip PLL           |

| ROSC       | 1MHz            | Internal RING OSC     |

The PLL can synthesize the PLLCLK clock up to 80 MHz with the FIN reference clock. It also has an internal pre-divider and post-divider.

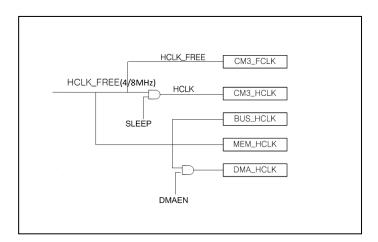

#### **HCLK Clock Domain**

The HCLK clock feeds the clock to the CPU and AHB bus. The Cortex-M3 CPU requires two clocks related with the HCLK clock:

FCLK – FCLK is a free-running clock which runs continuously except during Power-Down Mode HCLK – HCLK can be stopped during Idle Mode

#### Miscellaneous Clock Domain for Cortex-M3

Figure 4.4 Miscellaneous Clock Configuration

#### **PCLK Clock Domain**

PCLK is the master clock of all the peripherals. It can be stopped in Power-Down Mode. Each peripheral clock is generated by the PCER register set.

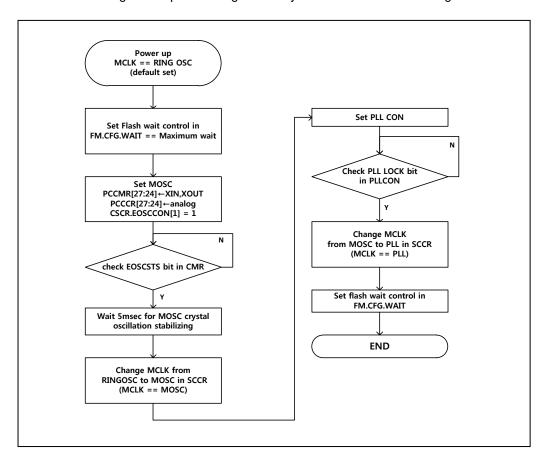

### **Clock Configuration**

After power up, the default system clock is fed by the RINGOSC (1 MHz) clock. RINGOSC is enabled by default at power up. The other clock sources are enabled by user controls with the RINGOSC system clock.

The MOSC clock can be enabled by the CSCR register. Before enabling the MOSC block, the pin mux configuration should be set for XIN, XOUT function. PC12 and PC13 pins are shared with MOSC's XIN and XOUT function - PCCMR and PCCCR registers should be correctly configured. After enabling the MOSC block, you must wait for more than 1 msec to ensure stable operation of crystal oscillation.

The PLL clock can be enabled by the PLLCON register. After enabling the PLL block, you must wait for the PLL lock flag. When the PLL output clock is stable; you can select MCLK for your system requirement. Before changing the system clock, Flash access wait should be set to the maximum value. After the system clock is changed, you will need to set the desired Flash access wait time.

An example flow chart outlining the steps to configure the system clock is shown in Figure 4.5.

Figure 4.5. Clock Configuration Flow Chart

When you speed up the system clock up to maximum operating frequency, you should check the Flash wait control configuration. Flash read access time is one of the limiting factors in performance. The wait control recommendation is provided in Table 4.2.

| Table 4.2 | Flash | Wait Contr | ol Recomme | ndation |

|-----------|-------|------------|------------|---------|

|           |       |            |            |         |

| FM.CFG.WAIT | FLASH Access Wait | Available Max System Clock Frequency |

|-------------|-------------------|--------------------------------------|

| 000         | 0 clock wait      | ~16MHz                               |

| 001         | 1 clock wait      | ~32MHz                               |

| 010         | 2 clock wait      | ~48MHz                               |

| 011         | 3 clock wait      | ~48MHz                               |

#### Reset

The Z32F0641 MCU has two system resets:

- Cold reset by POR, which is effective during power up or down sequence, and

- Warm reset, which is generated by several reset sources. The reset event causes the chip to return to initial state.

The cold reset has only one reset source, POR. The warm reset has the following reset sources:

- nRESET pin

- WDT reset

- LVD reset

- MCLK Fail reset

- MOSC Fail reset

- S/W reset

- CPU request reset

#### **Cold Reset**

Cold reset is an important feature of the chip when power is up. This characteristic globally affects the system boot. Internal VDC is enabled when VDD power is turned on. The internal VDD level slope is followed by the external VDD power slope. The internal PoR trigger level is 1.4 V of internal VDC voltage out level. At this time, boot operation is started. The RINGOSC clock is enabled and counts to 4 msec for internal VDC level stabilizing. During this time, the external VDD voltage level should be greater than the initial LVD level (2.3 V). After counting 4 msec, the CPU reset is released and the operation is started.

Figure 4.6 shows the power up sequence and internal reset waveform.