Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## Z80C30/Z85C30

# CMOS SCC Serial Communications Controller

**Product Specification**

PS011703-0102

This publication is subject to replacement by a later edition. To determine whether a later edition exists, or to request copies of publications, contact:

Windows is a registered trademark of Microsoft Corporation.

#### **Document Disclaimer**

© 2002 by ZiLOG, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZiLOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZiLOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. Except with the express written approval ZiLOG, use of information, devices, or technology as critical components of life support systems is not authorized. No licenses or other rights are conveyed, implicitly or otherwise, by this document under any intellectual property rights.

# **Table of Contents**

| Table of Contentsii                                       |

|-----------------------------------------------------------|

| List of Figures                                           |

| List of Tables vi                                         |

| Overview                                                  |

| Other Features for Z85C30 Only                            |

| General Description                                       |

| Pin Descriptions                                          |

| Z85C30    11      Z80C30    12                            |

| Functional Description                                    |

| I/O Interface Capabilities                                |

| Programming                                               |

| Z85C30                                                    |

| Z85C30/Z80C30 Setup                                       |

| Z85C30 Timing    48      Z80C30 Timing    51              |

| Electrical Characteristics 59                             |

| Absolute Maximum Ratings                                  |

| Standard Test Conditions                                  |

| Capacitance                                               |

| Miscellaneous                                             |

| DC Characteristics                                        |

| AC Characteristics                                        |

| Z85C30 Read/Write Timing Diagrams                         |

| Packaging and Ordering                                    |

| Package Information                                       |

| Ordering Information      84        Z80C30/Z85C30      84 |

PS011703-0102

# List of Figures

| Figure 1.  | SCC Block Diagram                            | 6  |

|------------|----------------------------------------------|----|

| Figure 2.  | Z85C30 and Z80C30 DIP Pin Assignments        | 13 |

| Figure 3.  | Z85C30 and Z80C30 PLCC Pin Assignments       | 14 |

| Figure 4.  | Z85C30 Pin Functions                         | 15 |

| Figure 5.  | Z80C30 Pin Functions                         | 16 |

| Figure 6.  | SCC Transmit Data Path                       | 18 |

| Figure 7.  | SCC Receive Data Path                        | 19 |

| Figure 8.  | SCC Interrupt Priority Schedule              | 23 |

| Figure 9.  | Some SCC Protocols                           | 27 |

| Figure 10. | Detecting 5- or 7-Bit Synchronous Characters | 28 |

| Figure 11. | An SDLC Loop                                 | 31 |

| Figure 12. | Data Encoding Methods                        | 35 |

| Figure 13. | SDLC Frame Status FIFO                       | 38 |

| Figure 14. | SDLC Byte Counting Detail                    | 39 |

| Figure 15. | Write Register Bit Functions                 | 42 |

| Figure 16. | Write Register Bit Functions                 | 43 |

| Figure 17. | Write Register Bit Functions                 | 44 |

| Figure 18. | Write Register Bit Functions                 | 45 |

| Figure 19. | Read Register Bit Functions                  | 47 |

| Figure 20. | Read Register Bit Functions                  | 48 |

| Figure 21. | Read Cycle Timing                            | 49 |

| Figure 22. | Write Cycle Timing                           | 50 |

| Figure 23. | Interrupt Acknowledge Cycle Timing           | 51 |

| Figure 24. | Read Cycle Timing                            | 52 |

| Figure 25. | Write Cycle Timing                           | 53 |

| Figure 26. | Interrupt Acknowledge Cycle Timing           | 54 |

| Figure 27. | Standard Test Load                           | 56 |

| Figure 28. | Open-Drain Test Load                         | 56 |

| Figure 29. | Z85C30 Read/Write Timing Diagram             | 60 |

| Figure 30. | Z85C30 Interrupt Acknowledge Timing Diagram  | 61 |

| Figure 31. | Z85C30 Cycle Timing Diagram                  | 61 |

| Figure 32. | Z85C30 Reset Timing Diagram                  | 62 |

| Figure 33. | Z85C30 General Timing Diagram                | 67 |

| Figure 34. | Z85C30 System Timing Diagram                 | 70 |

PS011703-0102 List of Figures

| Figure 35.   | Z80C30 Read/Write Timing Diagram            | 73 |

|--------------|---------------------------------------------|----|

| Figure 36.   | Z80C30 Interrupt Acknowledge Timing Diagram | 74 |

| Figure 37.   | Z80C30 Reset Timing Diagram                 | 74 |

| Figure 38. Z | Z80C30 General Timing Diagram               | 79 |

| Figure 39.   | Z80C30 System Timing Diagram                | 82 |

| Figure 40. 4 | 10-Pin DIP Package Diagram                  | 83 |

| Figure 41. 4 | 14-Pin PLCC Package Diagram                 | 84 |

List of Figures PS011703-0102

## List of Tables

| Table 1.  | SCC Read Register Functions        |

|-----------|------------------------------------|

| Table 2.  | SCC Write Register Functions       |

| Table 3.  | Capacitance                        |

| Table 4.  | Z80C30/Z85C30 DC Characteristics   |

| Table 5.  | Z85C30 Read/Write Timing 62        |

| Table 6.  | Z85C30 General Timing Table        |

| Table 7.  | Z85C30 System Timing Table         |

| Table 8.  | Z85C30 Read/Write Timing           |

| Table 9.  | Z80C30 Read/Write Timing           |

| Table 10. | Z80C30 General Timing 80           |

| Table 11. | Z80C30 System Timing               |

| Table 12. | Z80C30/Z85C30 Ordering Information |

PS011703-0102 List of Tables

PS011703-0102 List of Tables

1

## **Overview**

- Z85C30: Optimized for Non-Multiplexed Bus Microprocessors.

Z80C30: Optimized for Multiplexed Bus Microprocessors

- Pin Compatible to NMOS Versions

- Two Independent, 0 to 4.1 Mbit/Second, Full-Duplex Channels.

Each channel with Separate Crystal Oscillator, Baud Rate Generator, and Digital Phase-Locked Loop (DPLL) for Clock Recovery.

- Multi-Protocol Operation under Program Control; Programmable for NRZ, NRZI, or FM Data Encoding.

- Asynchronous Mode with Five to Eight Bits and One, One and One-Half, or Two Stop Bits Per Character, Programmable Clock Factor, Break Detection and Generation; Parity, Overrun, and Framing Error Detection.

- Synchronous Mode with Internal or External Character Synchronization on One or Two Synchronous Characters and CRC Generation and Checking with CRC-16 or CRC-CCITT Preset to either 1s or 0s.

- SDLC/HDLC Mode with Comprehensive Frame-Level Control, Automatic Zero Insertion and Deletion, I-Field Residue Handling, Abort Generation and Detection, CRC Generation and Checking, and SDLC Loop.

- Software Interrupt Acknowledge Feature (not available with NMOS)

- Local Loopback and Auto Echo Modes

- Supports T1 Digital Trunk

- Enhanced DMA Support (not available with NMOS) 10 x 19-Bit Status FIFO 14-Bit Byte Counter

PS011703-0102 Overview

#### Speeds:

- Z85C3O-8.5, 10, 16.384 MHz

- Z80C3O-8, 10 MHz

## Other Features for Z85C30 Only

Some of the features listed below are available by default. Some of them (features with \*) are disabled on default to maintain compatibility with the existing SCC design, and "program to enable through WR7".

- New programmable WR7' (write register 7 prime) to enable new features

- Improvements to support SDLC mode of synchronous communication

- Improve functionality to ease sending back-to-back frames

- Automatic SDLC opening Flag transmission\*

- Automatic Tx Underrun/EOM Latch reset in SDLC mode\*

- Automatic RTS deactivation\*

- TxD pin forced High in SDLC NRZI mode after closing flag\*

- Complete CRC reception\*

- Improved response to Abort sequence in status FIFO

- Automatic Tx CRC generator preset/reset

- Extended read for write registers\*

- Write data set-up timing improvement

- Improved AC timing

- Three to 3.6 PCLK access recovery time.

- Programmable DTR/REQ timing\*

PS011703-0102 Overview

3

- Write data to falling edge of WR set-up time requirement is now eliminated

- Reduced INT timing

- Other features include.

- Extended read function to read back the written value to the write registers.\*

- Latching RRO during read

- RRO, bit D7 and RR10, bit D6 now has reset default value.

Overview PS011703-0102

PS011703-0102 Overview

5

## **General Description**

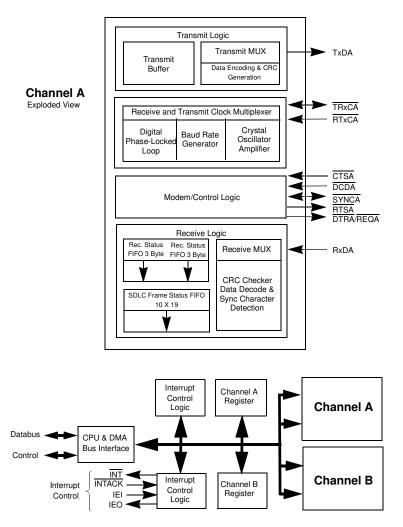

The ZiLOG Z80C30/Z85C30 Serial Communications Controller (SCC), is a pin and software compatible CMOS member of the SCC family introduced by ZiLOG in 1981. It is a dual channel, multi-protocol data communications peripheral that easily interfaces to CPU's with either multiplexed or non-multiplexed address/data buses. The advanced CMOS process offers lower power consumption, higher performance, and superior noise immunity. The programming flexibility of the internal registers allows the SCC to be configured to satisfy a wide variety of serial communications applications. Figure 1 illustrates a block diagram of the SCC.

The many on-chip features such as Baud Rate Generators (BRG), Digital Phase Locked Loops (DPLL), and crystal oscillators reduce the need for external logic. Additional features include a 10 x 19-bit status FIFO and 14-bit byte counter to support high speed SDLC transfers using DMA controllers.

The SCC handles asynchronous formats, synchronous byte-oriented protocols such as IBM Bisync, and synchronous bit-oriented protocols such as HDLC and IBM SDLC. This versatile device supports virtually any serial data transfer application (cassette, diskette, tape drives, etc.).

The device generates and checks CRC codes in any synchronous mode and can be programmed to check data integrity in various modes. The SCC also contains facilities for modem controls in both channels. In applications where these controls are not needed, the modem controls can be used for general-purpose I/O.

The daisy-chain interrupt hierarchy is also supported.

Figure 1. SCC Block Diagram

## **Pin Descriptions**

#### Z85C30/Z80C30 Common Pin Functions

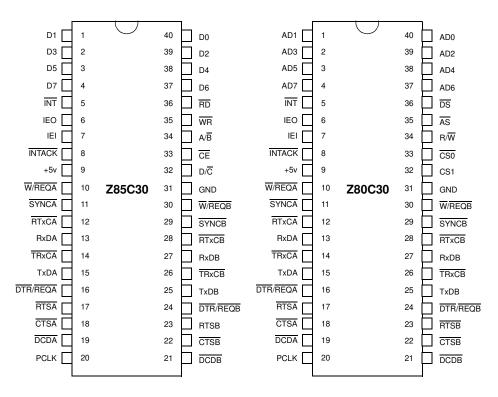

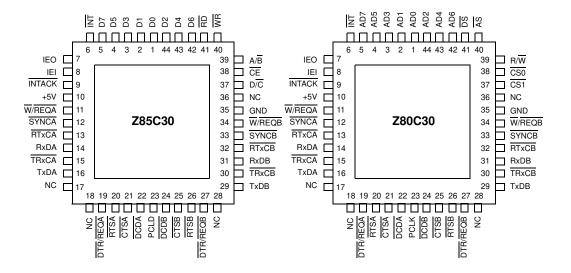

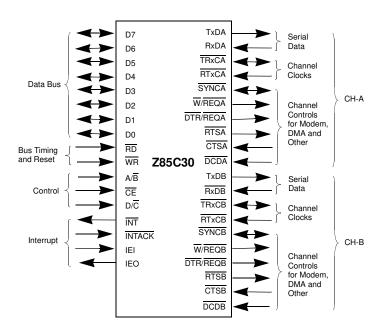

The following section describes the pin functions common to the Z85C30 and the Z80C30. Figures 2 and 3 detail the respective pin assignments and Figures 4 and 5 designate the pin functions.

### CTSA, CTSB

Clear To Send (inputs, active Low). If these pins are programmed for Auto Enable, a Low on the inputs enables the respective transmitters. If not programmed as Auto Enable, they may be used as general-purpose inputs. Both inputs are Schmitt-trigger buffered to accommodate slow rise-time inputs. The SCC detects pulses on these inputs and can interrupt the CPU on both logic level transitions.

## DCDA, DCDB

Data Carrier Detect (inputs, active Low). These pins function as receiver enables if they are programmed for Auto Enable. Otherwise, these pins are used as general-purpose input pins. Both pins are Schmitt-trigger buffered to accommodate slow rise-time signals. The SCC detects pulses on these pins and can interrupt the CPU on both logic level transitions.

### DTR/REQA, DTR/REQB

Data Terminal Ready/Request (outputs, active Low). These outputs follow the state programmed into the DTR bit. They can also be used as general-purpose outputs or as Request lines for a DMA controller.

#### IEI

Interrupt Enable In (input, active High). IEI is used with IEO to form an interrupt daisy-chain when there is more than one interrupt driven device. A high IEI indicates that no other higher priority device has an interrupt under service or is requesting an interrupt.

#### **IEO**

Interrupt Enable Out (output, active High). IEO is High only if IEI is High and the CPU is not servicing the SCC interrupt or the SCC is not requesting an interrupt (interrupt Acknowledge cycle only). IEO is connected to the next lower priority device's IEI input and thus inhibits interrupts from lower priority devices.

#### INT

*Interrupt Request* (output, open-drain, active Low). This signal activates when the SCC requests an interrupt.

#### **INTACK**

Interrupt Acknowledge (input, active Low). This signal indicates an active Interrupt Acknowledge cycle. During this cycle, the SCC interrupt daisy chain settles. When RD or DS becomes active, the SCC places an interrupt vector on the data bus (if IEI is High). INTACK is latched by the rising edge of PCLK.

#### **PCLK**

*Clock* (input). This is the master SCC clock used to synchronize internal signals. PCLK is a TTL level signal. PCLK is not required to have any phase relationship with the master system clock.

#### RxDA, RxDB

Receive Data (inputs, active High). These signals receive serial data at standard TTL levels.

### RTXCA, RTXCB

Receive/Transmit Clocks (inputs, active Low). These pins can be programmed in several different operating modes. In each channel, RTxC may supply the receive clock, the transmit clock, the clock for the Baud Rate Generator, or the clock for the Digital Phase-Locked Loop. These pins can also be programmed for use with the respective SYNC pins as a crystal oscillator. The receive clock may be 1, 16, 32, or 64 times the data rate in Asynchronous modes.

### RTSA, RTSB

Request To Send (outputs, active Low). When the Request To Send (RTS) bit in Write Register 5 (Figure 9) sets, the IRTS signal goes Low. When the RTS bit is reset in the Asynchronous mode and Auto Enable is on, the signal goes High after the transmitter is empty. In Synchronous mode it strictly follows the state of the RTS bit. Both pins can be used as general-purpose outputs.

## SYNCA, SYNCB

Synchronization (inputs or outputs, active Low). These pins function as inputs, outputs, or part of the crystal oscillator circuit. In the Asynchronous Receive mode (crystal oscillator option not selected), these pins are inputs similar to CTS and DCD. In this mode, transitions on these lines affect the state of the Synchronous/Hunt status bits in Read Register 0 (Figure 8) but have no other function.

In External Synchronization mode with the crystal osc<u>illator</u> not selected, these lines also act as inputs. In this mode, <u>SYNC</u> must be driven Low for two receive clock cycles after the last bit in the synchronous character is received. Character assembly begins on the rising <u>edge</u> of the receive clock immediately preceding the activation of <u>SYNC</u>.

In the Internal Synchronization mode (Monosync and Bisync) with the crystal oscillator not selected, these pins act as outputs and are active only during the part of the receive clock cycle in which synchronous characters are recognized This synchronous condition is not latched. These outputs are active each time a synchronization pattern is recognized (regardless of character boundaries). In SDLC mode, these pins act as outputs and are valid on receipt of a flag.

#### TxDA, TxDB

*Transmit Data* (outputs, active High). These output signals transmit serial data at standard TTL levels.

### TRXCA, TRXCB

Transmit/Receive Clocks (inputs or outputs, active low). These pins can be programmed in several different operating modes. TRxC may supply the receive clock or the transmit clock in the input mode or supply the output of the Digital Phase-locked loop, the crystal oscillator, the Baud Rate Generator, or the transmit clock in the output mode.

## W/REQA, W/REQB

Wait/Request (outputs, open-drain when programmed for a Wait function, driven High or low when programmed for a Request function). These dual-purpose outputs may be programmed as

Request lines for a DMA controller or as Wait lines to synchronize the CPU to the SCC data rate. The reset state is Wait.

#### Z85C30

#### $A/\overline{B}$

Channel A/Channel B (input). This signal selects the channel in which the read or write operation occurs.

#### CE

Chip Enable (input, active Low). This signal selects the SCC for a read or write operation.

#### D7-D0

Data Bus (bidirectional, tri-state). These lines carry data and command to and from the SCC.

### $DI\overline{C}$

Data/Control Select (input). This signal defines the type of information transferred to or from the SCC. A High indicates a data transfer; a Low indicates a command.

### $\overline{\mathsf{RD}}$

Read (input, active Low). This signal indicates a read operation and when the SCC is selected, enables the SCC's bus drivers. During the Interrupt Acknowledge cycle, this signal gates the interrupt vector onto the bus if the SCC is the highest priority device requesting an interrupt.

#### $\overline{\mathsf{WR}}$

*Write* (input, active Low). When the SCC is selected, this signal indicates a write operation. The coincidence of IAD and WR is interpreted as a reset.

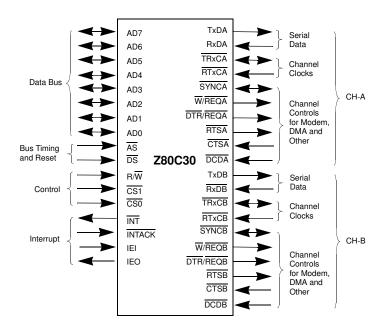

#### Z80C30

#### AD7-AD0

Address/Data Bus (bidirectional, active High, Tri-state). These multiplexed lines carry register addresses to the SCC as well as data or control information.

#### $\overline{\mathsf{AS}}$

Address Strobe (input, active Low). Addresses on AD7–AD0 are latched by the rising edge of this signal.

#### CS<sub>0</sub>

Chip Select 0 (input, active Low). This signal is latched concurrently with the addresses on AD7–AD0 and must be active for the intended bus transaction to occur.

#### CS<sub>1</sub>

Chip Select 1 (input, active High). This second select signal must also be active before the intended bus transaction can occur. CS1 must remain active throughout the transaction.

DS

Data strobe (input, active Low). This signal provides timing for the transfer of data into and out of the SCC. If AS and DS coincide, this confluence is interpreted as a reset.

#### $R/\overline{W}$

Read/Write (input). This signal specifies whether the operation to be performed is a read or a write.

Figure 2. Z85C30 and Z80C30 DIP Pin Assignments

Figure 3. Z85C30 and Z80C30 PLCC Pin Assignments

Figure 4. Z85C30 Pin Functions

Figure 5. Z80C30 Pin Functions

## Functional Description

The architecture of the SCC is described from two points of view:

- As a data communications device which transmits and receives data in a wide variety of protocols;

- As a microprocessor peripheral in which the SCC offers valuable features such as vectored interrupts and DMA support.

The SCC's peripheral and data communication are described in the following sections. Figure 1 on page 6 illustrates the SCC block diagram. Figures 6 and 7 show the details of the communications between the receive and transmit logic to the system bus. The features and data path for each of the SCC's A and B channels is identical.