# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

Z87200

## Spread-Spectrum Transceiver

**Product Specification**

PS010202-0601

ZiLOG Worldwide Headquarters • 910 E. Hamilton Avenue • Campbell, CA 95008 Telephone: 408.558.8500 • Fax: 408.558.8300 • <u>www.ZiLOG.com</u>

Z87200 Spread-Spectrum Transceiver

This publication is subject to replacement by a later edition. To determine whether a later edition exists, or to request copies of publications, contact:

#### **ZiLOG Worldwide Headquarters**

910 E. Hamilton Avenue Campbell, CA 95008 Telephone: 408.558.8500 Fax: 408.558.8300 www.ZiLOG.com

ZiLOG is a registered trademark of ZiLOG Inc. in the United States and in other countries. All other products and/or service names mentioned herein may be trademarks of the companies with which they are associated.

#### **Document Disclaimer**

©2001 by ZiLOG, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZiLOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. Devices sold by ZiLOG, Inc. are covered by warranty and limitation of liability provisions appearing in the ZiLOG, Inc. Terms and Conditions of Sale. ZiLOG, Inc. makes no warranty of merchantability or fitness for any purpose. Except with the express written approval of ZiLOG, use of information, devices, or technology as critical components of life support systems is not authorized. No licenses are conveyed, implicitly or otherwise, by this document under any intellectual property rights.

### **Z87200** Spread-Spectrum Transceiver

#### **FEATURES**

| Device    | Min<br>PN Rate*<br>(Mchips) | Max Data<br>Rate* (Mbps) | Speed<br>(MHz) | Package         |

|-----------|-----------------------------|--------------------------|----------------|-----------------|

| Z87200    | 11                          | 2.048                    | 20/45          | 100-Pin<br>PQFP |

| Note: *45 |                             |                          |                |                 |

Note: \*45 MHz only

- Complete Direct Sequence Spread-Spectrum Transceiver in a Single CMOS IC

- Programmable Functionality Supports Many Different Operational Modes

- Acquires Within One Symbol Duration Using Digital PN Matched Filter

- Two Independent PN Sequences, Each up to 64 Chips Long for Distinct Processing of the Acquisition/Preamble Symbol and Subsequent Data Symbols

- Power Management Features

- Optional Spectral Whitening Code Generation

■ Full- or Half-Duplex Operation

#### **Benefits**

- High Performance and High Reliability for Reduced Manufacturing Costs

- Ideal for a Wide Range of Wireless Applications Including Data Acquisition Systems, Transaction Systems, and Wireless Local Area Networks (WLANs)

- Fast Response and Very Low Overhead when Operating in Burst Modes

- Allows High Processing Gain to Maximize the Acquisition Probability, then Reduced Code Length for Increased Data Rate

- Reduced Power Consumption

- Randomizes Data to Meet Regulatory Requirements

- Permits Dual Frequency (Frequency Division Duplex) or Single Frequency (Time Division Duplex) Operation

- Small Footprint, Surface Mount

#### **GENERAL DESCRIPTION**

The Z87200 is a programmable single-chip, spread-spectrum, direct-sequence transceiver. The Z87200 incorporates Stanford Telecom spread-spectrum and wireless technology and is identical to Stanford Telecom's STEL-2000A. By virtue of its fast acquisition capabilities and its ability to support a wide range of data rates and spreadspectrum parameters, the Z87200 spread-spectrum transceiver supports the implementation of a wide range of burst data communications applications.

Available in both 45- and 20-MHz versions, the Z87200 performs all the digital processing required to implement a fast-acquisition direct sequence (such as pseudonoise- or

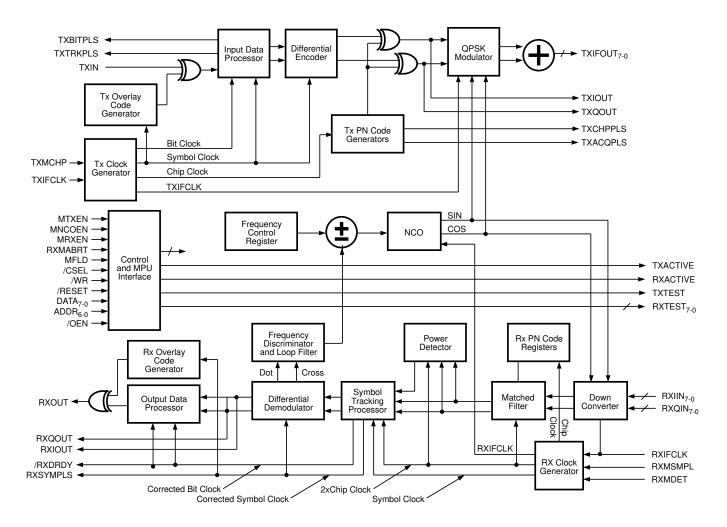

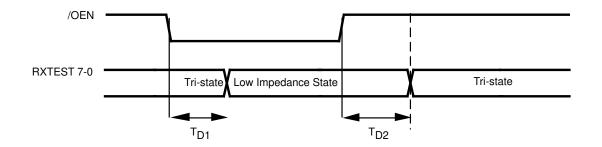

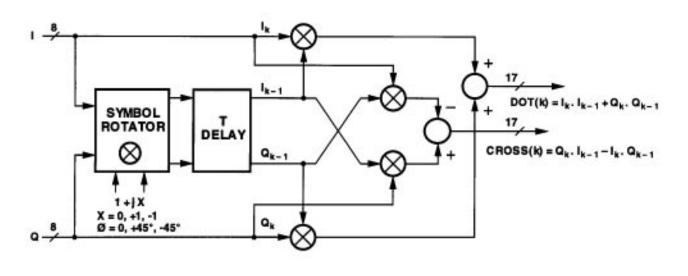

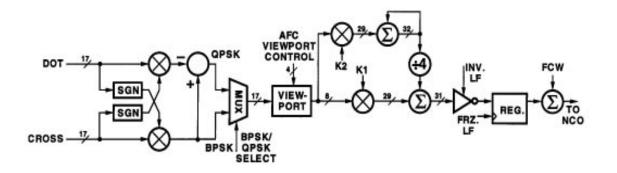

PN-modulated), spread-spectrum full- or half-duplex system. Differentially encoded BPSK and QPSK are fully supported. The receiver section can also handle differentially encoded pi/4 QPSK. A block diagram of the Z87200 is shown in Figure 1; its pin configuration is shown in Z87200 receive functions integrate the capabilities of a digital downconverter, PN matched filter, and DPSK demodulator, where the input signal is an analog-to-digital converted I.F. signal. Z87200 transmit functions include a differential BPSK/QPSK encoder, PN modulator (spreader), and BPSK/QPSK modulator, where the transmitter output is a sampled digitally modulated signal ready for external digi-

### PS010202-0601

#### **GENERAL DESCRIPTION** (Continued)

tal-to-analog conversion (or, if preferred, the spread baseband signal may be output to an external modulator).

These transceiver functions have been designed and integrated for the transmission and reception of bursts of spread data. In particular, the PN Matched Filter has two distinct PN coefficient registers (rather than a single one) in order to speed and improve signal acquisition performance by automatically switching from one to the other upon signal acquisition. The Z87200 is thus optimized to provide reliable, high-speed wireless data communications.

#### Symbol-Synchronous PN Modulation

The Z87200 operates with symbol-synchronous PN modulation in both transmit and receive modes. Symbol-synchronous PN modulation refers to operation where the PN code is aligned with the symbol transitions and repeats once per symbol. By synchronizing a full PN code cycle over a symbol duration, acquisition of the PN code at the receiver simultaneously provides symbol synchronization, thereby significantly improving overall acquisition time.

As a result of the Z87200's symbol-synchronous PN modulation, the data rate is defined by the PN chip rate and length of the PN code; that is, by the number of chips per symbol, where a "chip" is a single "bit" of the PN code. The PN chip rate, R<sub>c</sub> chips/second, is programmable to as much as 1/4 the rate of RXIFCLK, and the PN code length, N, can be programmed up to a value of 64. When operating with BPSK modulation, the data rate for a PN code of length N and PN chip rate R<sub>C</sub> chips/sec is R<sub>C</sub>/N bps. When operating with QPSK modulation (or  $\pi/4$  QPSK with an external modulator), two bits of data are transmitted per symbol, and the data rate for a PN code of length N and PN chip rate R<sub>c</sub> chips/sec is 2R<sub>c</sub>/N bps. Conversely, for a given data rate Rb bps, the length N of the PN code defines the PN chip rate R<sub>c</sub> as N x R<sub>b</sub> chips/sec for BPSK or as (N x R<sub>b</sub>)/2 chips/sec for QPSK.

The data rate  $R_b$  and the PN code length N, however, cannot generally be arbitrarily chosen. United States FCC Part 15.247 regulations require a minimum processing gain of 10 dB for unlicensed operation in the Industrial, Scientific, and Medical (ISM) bands, implying that the value of N must be at least 10. To implement such a short code, a Barker code of length 11 would typically be used in order to obtain desirable auto- and cross-correlation properties, although compliance with FCC regulations depends upon the overall system implementation. The Z87200 further includes transmit and receive code overlay generators to insure that signals spread with such a short PN code length possess the spectral properties required by FCC regulations.

The receiver clock rate established by RXIFCLK must be at least four times the receive PN spreading rate and is limited to a maximum speed of 45.056 MHz in the 45 MHz Z87200 and 20.0 MHz in the 20 MHz Z87200. The ensuing discussion is in terms of the 45 MHz Z87200, but the numerical values may be scaled proportionately for the 20 MHz version. As a result of the maximum 45.056 MHz RX-IFCLK, the maximum supported PN chip rate is 11.264 Mchips/second. When operating with BPSK modulation, the maximum data rate for a PN code of length N is 11.264/N Mbps. When operating with QPSK modulation (or  $\pi/4$  QPSK with an external modulator), two bits of data are transmitted per symbol, and the data rate for a PN code of length N is 22.528/N Mbps. Conversely, for a given data rate R<sub>b</sub>, the length N of the PN code employed must be such that the product of N x R<sub>b</sub> is less than 11.264 Mchips/sec (for BPSK) or 22.528 Mchips/sec (for QPSK). For the 45 MHz Z87200, then, a PN code length of 11 implies that the maximum data rate that can be supported in compliance with the processing gain requirements of FCC regulations is 2.048 Mbps using differential QPSK. Note again, however, that FCC compliance using the Z87200 with a PN code of length 11 depends upon the overall system implementation.

#### Z87200 I.F. Interface

The Z87200 receiver circuitry employs an NCO and complex multiplier referenced to RXIFCLK to perform frequency downconversion, where the input I.F. sampling rate and the clock rate of RXIFCLK must be identical. In "complex input" or Quadrature Sampling Mode, external dual analog-to-digital converters (ADCs) sample quadrature I.F. signals so that the Z87200 can perform true full single sideband downconversion directly from I.F. to baseband. At PN chip rates less than one-eighth the value of RXIF-CLK, downconversion may also be effected using a single ADC in "real input" or Direct I.F. Sampling Mode.

The input I.F. frequency is not limited by the capabilities of the Z87200. The highest frequency to which the NCO can be programmed is 50% of the I.F. sampling rate (the frequency of RXIFCLK); moreover, the signal bandwidth, NCO frequency, and I.F. sampling rate are all interrelated, as discussed in Higher I.F. frequencies, however, can be supported by using one of the aliases of the NCO frequency generated by the sampling process. For example, a spread signal presented to the Z87200's receiver ADCs at an I.F. frequency of f<sub>I.F.</sub>, where f<sub>RXIFCLK</sub> < f<sub>I.F.</sub> < 2 x f<sub>RXIF</sub>. CLK, can generally, as allowed by the signal's bandwidth, be supported by programming the Z87200's NCO to a frequency of (f<sub>I.F.</sub>- f<sub>RXIFCLK</sub>), as discussed in Appendix A of this product specification. The maximum I.F. frequency is then limited by the track-and-hold capabilities of the ADC(s) selected. Signals at I.F. frequencies up to about 100 MHz can be processed by currently available 8-bit ADCs, but the implementation cost as well as the performance can typically be improved by using an I.F. frequency of 30 MHz or lower. Downconversion to baseband is then accomplished digitally by the Z87200, with a programmable loop filter provided to establish a frequency tracking loop.

#### **Burst and Continuous Data Modes**

The Z87200 is designed to operate in either burst or continuous mode: in burst mode, built-in symbol counters allow bursts of up to 65,533 symbols to be automatically transmitted or received; in continuous mode, the data is simply treated as a burst of infinite length. The Z87200's use of a digital PN Matched Filter for code detection and despreading permits signal and symbol timing acquisition in just one symbol. The fast acquisition properties of this design are exploited by preceding each data burst with a single Acquisition/Preamble symbol, allowing different PN codes (at the same PN chip rate) to independently spread the Acquisition/Preamble and data symbols. In this way, a long PN code with high processing gain can be used for the Acquisition/Preamble symbol to maximize the probability of burst detection, and a shorter PN code can be used thereafter to permit a higher data rate.

To improve performance in the presence of high noise and interference levels, the Z87200 receiver's symbol timing recovery circuit incorporates a "flywheel circuit" to maximize the probability of correct symbol timing. This circuit will insert a symbol clock pulse if the correlation peak obtained by the PN Matched Filter fails to exceed the programmed detect threshold at the expected time during a given symbol. During each burst, a missed detect counter tallies each such event to monitor performance and allow a burst to be aborted in the presence of abnormally high interference. A timing gate circuit further minimizes the probability of false correlation peak detection and consequent false symbol clock generation due to noise or interference.

To minimize power consumption, individual sections of the device can be turned off when not in use. For example, the receiver circuitry can be turned off during transmission and, conversely, the transmitter circuitry can be turned off during reception when the Z87200 is operating in a half-duplex/time division duplex (TDD) system. If the NCO is not being used as the BPSK/QPSK modulator (that is, if an external modulator is being used), the NCO can also be turned off during transmission to conserve still more power.

#### Conclusion

The fast acquisition characteristics of the Z87200 make it ideal for use in applications where bursts are transmitted relatively infrequently. In such cases, the device can be controlled so that it is in full "sleep" mode with all receiver, transmitter, and NCO functions turned off over the majority of the burst cycle, thereby significantly reducing the aggregate power consumption. Since the multiply operations of the PN Matched Filter consume a major part of the overall power required during receiver operation, two independent power-saving techniques are also built into the PN Matched Filter to reduce consumption during operation by a significant factor for both short and long PN spreading codes.

The above features make the Z87200 an extremely versatile and useful device for spread-spectrum data communications. Operating at its highest rates, the Z87200 is suitable for use in wireless Local Area Network implementations, while its programmability allows it to be used in a variety of data acquisition, telemetry, and transaction system applications.

#### **GENERAL DESCRIPTION** (Continued)

Figure 1. Z87200 Block Diagram

#### **PIN DESCRIPTION**

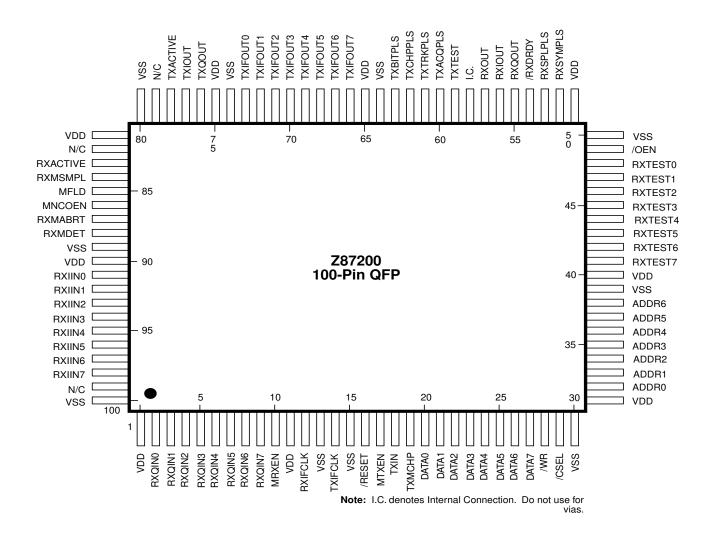

Figure 2. Z87200 100-Pin PQFP Pin Description

#### PIN DESCRIPTION (Continued)

#### Table 1. 100-Pin PQFP Pin Description

| 1,11,31,40,51,6 V       Power Supply         5,75,81,90       DD         2       RXQIN0       Rx Q-Channel Input<br>(Bit 0; LSB)         3       RXQIN1       Rx Q-Channel Input (Bit 1)         4       RXQIN2       Rx Q-Channel Input (Bit 2)         5       RXQIN3       Rx Q-Channel Input (Bit 3)         6       RXQIN4       Rx Q-Channel Input (Bit 4)         7       RXQIN5       Rx Q-Channel Input (Bit 5)         8       RXQIN7       Rx Q-Channel Input (Bit 6)         9       RXQIN7       Rx Q-Channel Input (Bit 7)         10       RXXE       Manual Receiver Enable         12       RXIFCLK       Receiver I.F. Clock         13,15,30,39,50, V       Ground       64,74,80,89         SS       I4       TXIFCLK       Transmitter I.F. Clock         16       //RESET       //Reset         17       MTXE       Manual Transmitter Enable         18       TXIN       Transmitter Input         19       TXMCHP       Transmitter Input         <                     | No              | Symbol   | Function                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------|-------------------------------|

| 2       RXQIN0       RX Q-Channel Input<br>(Bit 0; LSB)         3       RXQIN1       Rx Q-Channel Input (Bit 1)         4       RXQIN2       Rx Q-Channel Input (Bit 2)         5       RXQIN3       Rx Q-Channel Input (Bit 3)         6       RXQIN4       Rx Q-Channel Input (Bit 4)         7       RXQIN6       Rx Q-Channel Input (Bit 5)         8       RXQIN7       Rx Q-Channel Input (Bit 6)         9       RXQIN7       Rx Q-Channel Input (Bit 6)         10       RXXE       Manual Receiver Enable         12       RXIFCLK       Receiver I.F. Clock         16       /RESET       /Reset         17       MTXE       Manual Transmitter Input         19       TXINCHP       Transmitter Input         19       TXMCHP       Transmitter Manual Chip Pulse         20       DATA1       Data Bus (Bit 2)         23       DATA2       Data Bus (Bit 1)         24       DATA4       Data Bus (Bit 5)                  | 1,11,31,40,51,6 | V        | Power Supply                  |

| (Bit 0; LSB)3RXQIN1Rx Q-Channel Input (Bit 1)4RXQIN2Rx Q-Channel Input (Bit 2)5RXQIN3Rx Q-Channel Input (Bit 3)6RXQIN4Rx Q-Channel Input (Bit 5)8RXQIN5Rx Q-Channel Input (Bit 5)8RXQIN7Rx Q-Channel Input (Bit 6)9RXQIN7Rx Q-Channel Input (Bit 6)9RXQIN7Rx Q-Channel Input (Bit 6)10RXXEManual Receiver Enable12RXIFCLKReceiver I.F. Clock13,15,30,39,50, VGround64,74,80,89SS14TXIFCLKTransmitter I.F. Clock16/RESET/Reset17MTXEManual Transmitter Enable18TXINTransmitter Input19TXMCHPTransmitter Input19TXMCHPTransmitter Input19TXMCHPData Bus (Bit 0; LSB)21DATA0Data Bus (Bit 1)22DATA2Data Bus (Bit 3)24DATA4Data Bus (Bit 4)25DATA5Data Bus (Bit 6)27DATA6Data Bus (Bit 7; MSB)28/WRWrite Bar29/CSELChip Select Bar32ADDR0Address Bus (Bit 7; LSB)33ADDR1Address Bus (Bit 0; LSB)33ADDR1Address Bus (Bit 1)34ADDR2Address Bus (Bit 1)35ADDR3Address Bus (Bit 1)36ADDR4Address Bus (Bit 3) <t< td=""><td></td><td>DD</td><td></td></t<>                                                                                                                                                                                                                       |                 | DD       |                               |

| 3       RXQIN1       Rx Q-Channel Input (Bit 1)         4       RXQIN2       Rx Q-Channel Input (Bit 2)         5       RXQIN3       Rx Q-Channel Input (Bit 3)         6       RXQIN4       Rx Q-Channel Input (Bit 4)         7       RXQIN5       Rx Q-Channel Input (Bit 5)         8       RXQIN6       Rx Q-Channel Input (Bit 6)         9       RXQIN7       Rx Q-Channel Input (Bit 6)         9       RXQIN7       Rx Q-Channel Input (Bit 6)         10       RXXE       Manual Receiver Enable         12       RXIFCLK       Receiver I.F. Clock         13.15.30,39,50, V       Ground         64,74,80,89       S         14       TXIFCLK       Transmitter I.F. Clock         16       /RESET       /Reset         17       MTXE       Manual Transmitter Enable         18       TXIN       Transmitter Input         19       TXMCHP       Transmitter Manual Chip Pulse         20       DATA0       Data Bus (Bit 0; LSB)         21       DATA1       Data Bus (Bit 3)         24       DATA5       Data Bus (Bit 4)         25       DATA5       Data Bus (Bit 5)         26       DATA6       Data Bus (Bit                                     | 2               | RXQIN0   |                               |

| 4       RXQIN2       Rx Q-Channel Input (Bit 2)         5       RXQIN3       Rx Q-Channel Input (Bit 3)         6       RXQIN4       Rx Q-Channel Input (Bit 4)         7       RXQIN5       Rx Q-Channel Input (Bit 5)         8       RXQIN6       Rx Q-Channel Input (Bit 6)         9       RXQIN7       Rx Q-Channel Input (Bit 6)         9       RXQIN7       Rx Q-Channel Input (Bit 6)         10       RXXE       Manual Receiver Enable         12       RXIFCLK       Receiver I.F. Clock         13,15,30,39,50, V       Ground         64,74,80,89       SS         14       TXIFCLK       Transmitter I.F. Clock         16       /RESET       /Reset         17       MTXE       Manual Transmitter Enable         18       TXIN       Transmitter Input         19       TXMCHP       Transmitter Manual Chip Pulse         20       DATA0       Data Bus (Bit 0, LSB)         21       DATA1       Data Bus (Bit 1)         22       DATA2       Data Bus (Bit 5)         26       DATA5       Data Bus (Bit 5)         26       DATA6       Data Bus (Bit 6)         27       DATA7       Data Bus (Bit 1)                                           |                 |          |                               |

| 5       RXQIN3       Rx Q-Channel Input (Bit 3)         6       RXQIN4       Rx Q-Channel Input (Bit 4)         7       RXQIN5       Rx Q-Channel Input (Bit 5)         8       RXQIN6       Rx Q-Channel Input (Bit 5)         8       RXQIN7       Rx Q-Channel Input (Bit 6)         9       RXQIN7       Rx Q-Channel Input (Bit 6)         9       RXQIN7       Rx Q-Channel Input (Bit 6)         10       RXXE       Manual Receiver Enable         12       RXIFCLK       Receiver I.F. Clock         13,15,30,39,50, V       Ground         64,74,80,89       SS         14       TXIFCLK       Transmitter I.F. Clock         16       /RESET       /Reset         17       MTXE       Manual Transmitter Input         19       TXIN       Transmitter Input         19       TXMCHP       Transmitter Manual Chip Pulse         20       DATA0       Data Bus (Bit 0; LSB)         21       DATA1       Data Bus (Bit 1)         22       DATA2       Data Bus (Bit 1)         23       DATA5       Data Bus (Bit 5)         26       DATA6       Data Bus (Bit 6)         27       DATA7       Data Bus (Bit 0; LSB) </td <td></td> <td></td> <td> ,</td>  |                 |          | ,                             |

| 6       RXQIN4       Rx Q-Channel Input (Bit 4)         7       RXQIN5       Rx Q-Channel Input (Bit 5)         8       RXQIN6       Rx Q-Channel Input (Bit 5)         9       RXQIN7       Rx Q-Channel Input (Bit 6)         9       RXQIN7       Rx Q-Channel Input (Bit 6)         9       RXQIN7       Rx Q-Channel Input (Bit 6)         10       RXXE       Manual Receiver Enable         12       RXIFCLK       Receiver I.F. Clock         13,15,30,39,50, V       Ground       64,74,80,89         5S       14       TXIFCLK       Transmitter I.F. Clock         16       /RESET       /Reset       17         17       MTXE       Manual Transmitter Enable         18       TXIN       Transmitter Input         19       TXMCHP       Transmitter Manual Chip Pulse         20       DATA0       Data Bus (Bit 0; LSB)         21       DATA1       Data Bus (Bit 1)         22       DATA2       Data Bus (Bit 3)         24       DATA4       Data Bus (Bit 6)         27       DATA5       Data Bus (Bit 0; LSB)         28       /WR       Write Bar         29       /CSEL       Chip Select Bar <t< td=""><td></td><td></td><td>· · · ·</td></t<> |                 |          | · · · ·                       |

| 7RXQIN5Rx Q-Channel Input (Bit 5)8RXQIN6Rx Q-Channel Input (Bit 6)9RXQIN7Rx Q-Channel Input (Bit 6)9RXXEManual Receiver Enable12RXIFCLKReceiver I.F. Clock13,15,30,39,50, VGround64,74,80,89SS14TXIFCLKTransmitter I.F. Clock16/RESET/Reset17MTXEManual Transmitter Enable18TXINTransmitter Input19TXMCHPTransmitter Manual Chip Pulse20DATA0Data Bus (Bit 0; LSB)21DATA1Data Bus (Bit 1)22DATA2Data Bus (Bit 2)23DATA3Data Bus (Bit 3)24DATA4Data Bus (Bit 3)25DATA5Data Bus (Bit 6)27DATA6Data Bus (Bit 6)28//WRWrite Bar29/CSELChip Select Bar32ADDR0Address Bus (Bit 0; LSB)33ADDR1Address Bus (Bit 1)34ADDR2Address Bus (Bit 3)36ADDR3Address Bus (Bit 4)37ADDR5Address Bus (Bit 6)38ADDR6Address Bus (Bit 6)38ADDR6Address Bus (Bit 6)38ADDR5Address Bus (Bit 6)39ADCR6Address Bus (Bit 6)31RXTEST5Receiver Test Output (Bit 6)33RXTEST6Receiver Test Output (Bit 6)34RXTEST7Receiver Test Output (Bit 1                                                                                                                                                                                                                                                          |                 |          |                               |

| 8       RXQIN6       Rx Q-Channel Input (Bit 6)         9       RXQIN7       Rx Q-Channel Input (Bit 6)         9       RXQIN7       Rx Q-Channel Input (Bit 7; MSB)         10       RXXE       Manual Receiver Enable         12       RXIFCLK       Receiver I.F. Clock         13,15,30,39,50, V       Ground         64,74,80,89       SS         14       TXIFCLK       Transmitter I.F. Clock         16       /RESET       /Reset         17       MTXE       Manual Transmitter Enable         18       TXIN       Transmitter Input         19       TXMCHP       Transmitter Manual Chip Pulse         20       DATA0       Data Bus (Bit 0; LSB)         21       DATA1       Data Bus (Bit 1)         22       DATA2       Data Bus (Bit 3)         24       DATA4       Data Bus (Bit 4)         25       DATA5       Data Bus (Bit 7; MSB)         28       /WR       Write Bar         29       /CSEL       Chip Select Bar         32       ADDR0       Address Bus (Bit 0; LSB)         33       ADDR1       Address Bus (Bit 3)         36       ADDR2       Address Bus (Bit 5)         <                                                           |                 |          |                               |

| 9RXQIN7Rx Q-Channel Input<br>(Bit 7; MSB)10RXXEManual Receiver Enable12RXIFCLKReceiver I.F. Clock13,15,30,39,50, VGround64,74,80,89SS14TXIFCLKTransmitter I.F. Clock16/RESET/Reset17MTXEManual Transmitter Enable18TXINTransmitter Input19TXMCHPTransmitter Manual Chip Pulse20DATA0Data Bus (Bit 0; LSB)21DATA1Data Bus (Bit 1)22DATA2Data Bus (Bit 2)23DATA3Data Bus (Bit 3)24DATA4Data Bus (Bit 5)26DATA5Data Bus (Bit 6)27DATA6Data Bus (Bit 6)27DATA7Data Bus (Bit 7; MSB)28/WRWrite Bar29/CSELChip Select Bar32ADDR0Address Bus (Bit 0; LSB)33ADDR1Address Bus (Bit 3)36ADDR2Address Bus (Bit 3)36ADDR4Address Bus (Bit 5)38ADDR5Address Bus (Bit 6; MSB)41RXTEST7Receiver Test Output (Bit 7)42RXTEST8Receiver Test Output (Bit 6)43RXTEST9Receiver Test Output (Bit 4)45RXTEST1Receiver Test Output (Bit 1)48RXTEST0Receiver Test Output (Bit 0)49/OENOutput Enable Bar52RXSYMPLSReceiver Symbol Pulse                                                                                                                                                                                                                                                          |                 |          | · · · ·                       |

| (Bit 7; MSB)10RXXEManual Receiver Enable12RXIFCLKReceiver I.F. Clock13,15,30,39,50, VGround64,74,80,89SS14TXIFCLKTransmitter I.F. Clock16//RESET//Reset17MTXEManual Transmitter Enable18TXINTransmitter Input19TXMCHPTransmitter Manual Chip Pulse20DATA0Data Bus (Bit 0; LSB)21DATA1Data Bus (Bit 1)22DATA2Data Bus (Bit 3)24DATA4Data Bus (Bit 3)24DATA5Data Bus (Bit 5)26DATA6Data Bus (Bit 6)27DATA5Data Bus (Bit 6)27DATA6Data Bus (Bit 7; MSB)28/WRWrite Bar29/CSELChip Select Bar32ADDR0Address Bus (Bit 0; LSB)33ADDR1Address Bus (Bit 2)35ADDR3Address Bus (Bit 3)36ADDR4Address Bus (Bit 4)37ADDR5Address Bus (Bit 5)38ADDR6Address Bus (Bit 6; MSB)41RXTEST6Receiver Test Output (Bit 7)42RXTEST3Receiver Test Output (Bit 4)45RXTEST3Receiver Test Output (Bit 4)46RXTEST3Receiver Test Output (Bit 3)46RXTEST1Receiver Test Output (Bit 0)49/OENOutput Enable Bar52RXSYMPLSReceiver Symbol Pulse </td <td></td> <td></td> <td></td>                                                                                                                                                                                                                        |                 |          |                               |

| 12RXIFCLKReceiver I.F. Clock13,15,30,39,50, VGround64,74,80,89SS14TXIFCLKTransmitter I.F. Clock16/RESET/Reset17MTXEManual Transmitter Enable18TXINTransmitter Input19TXMCHPTransmitter Manual Chip Pulse20DATA0Data Bus (Bit 0; LSB)21DATA1Data Bus (Bit 2)23DATA2Data Bus (Bit 3)24DATA4Data Bus (Bit 5)26DATA5Data Bus (Bit 6)27DATA6Data Bus (Bit 6)27DATA7Data Bus (Bit 7; MSB)28/WRWrite Bar29/CSELChip Select Bar32ADDR0Address Bus (Bit 0; LSB)33ADDR1Address Bus (Bit 3)36ADDR3Address Bus (Bit 3)36ADDR4Address Bus (Bit 4)37ADDR5Address Bus (Bit 5)38ADDR6Address Bus (Bit 6; MSB)41RXTEST6Receiver Test Output (Bit 7)42RXTEST6Receiver Test Output (Bit 6)43RXTEST3Receiver Test Output (Bit 4)45RXTEST3Receiver Test Output (Bit 2)46RXTEST1Receiver Test Output (Bit 1)48RXTEST0Receiver Test Output (Bit 0)49/OENOutput Enable Bar52RXSYMPLSReceiver Symbol Pulse                                                                                                                                                                                                                                                                                       | 9               | RXQIN7   |                               |

| 13,15,30,39,50, V<br>64,74,80,89Ground14TXIFCLKTransmitter I.F. Clock16/RESET/Reset17MTXEManual Transmitter Enable18TXINTransmitter Input19TXMCHPTransmitter Manual Chip Pulse20DATA0Data Bus (Bit 0; LSB)21DATA1Data Bus (Bit 2)23DATA2Data Bus (Bit 3)24DATA4Data Bus (Bit 5)26DATA5Data Bus (Bit 6)27DATA6Data Bus (Bit 6)27DATA7Data Bus (Bit 7; MSB)28/WRWrite Bar29/CSELChip Select Bar32ADDR0Address Bus (Bit 0; LSB)33ADDR1Address Bus (Bit 3)36ADDR3Address Bus (Bit 7)37ADDR5Address Bus (Bit 7)42RXTEST6Receiver Test Output (Bit 7)42RXTEST6Receiver Test Output (Bit 7)44RXTEST3Receiver Test Output (Bit 4)45RXTEST3Receiver Test Output (Bit 3)46RXTEST3Receiver Test Output (Bit 2)47RXTEST1Receiver Test Output (Bit 1)48RXTEST0Receiver Test Output (Bit 0)49/OENOutput Enable Bar52RXSYMPLSReceiver Symbol Pulse                                                                                                                                                                                                                                                                                                                                     | 10              | RXXE     | Manual Receiver Enable        |

| 64,74,80,89SS14TXIFCLKTransmitter I.F. Clock16/RESET/Reset17MTXEManual Transmitter Enable18TXINTransmitter Input19TXMCHPTransmitter Manual Chip Pulse20DATA0Data Bus (Bit 0; LSB)21DATA1Data Bus (Bit 1)22DATA2Data Bus (Bit 2)23DATA3Data Bus (Bit 3)24DATA4Data Bus (Bit 3)24DATA5Data Bus (Bit 5)26DATA6Data Bus (Bit 6)27DATA7Data Bus (Bit 7; MSB)28/WRWrite Bar29/CSELChip Select Bar32ADDR0Address Bus (Bit 0; LSB)33ADDR1Address Bus (Bit 2)35ADDR3Address Bus (Bit 3)36ADDR4Address Bus (Bit 3)37ADDR5Address Bus (Bit 4)37ADDR6Address Bus (Bit 6; MSB)41RXTEST7Receiver Test Output (Bit 7)42RXTEST6Receiver Test Output (Bit 7)44RXTEST3Receiver Test Output (Bit 3)46RXTEST3Receiver Test Output (Bit 3)46RXTEST1Receiver Test Output (Bit 1)48RXTEST0Receiver Test Output (Bit 0)49/OENOutput Enable Bar52RXSYMPLSReceiver Symbol Pulse                                                                                                                                                                                                                                                                                                                   | 12              | RXIFCLK  | Receiver I.F. Clock           |

| 14TXIFCLKTransmitter I.F. Clock16/RESET/Reset17MTXEManual Transmitter Enable18TXINTransmitter Input19TXMCHPTransmitter Manual Chip Pulse20DATA0Data Bus (Bit 0; LSB)21DATA1Data Bus (Bit 1)22DATA2Data Bus (Bit 2)23DATA3Data Bus (Bit 3)24DATA4Data Bus (Bit 3)24DATA5Data Bus (Bit 5)26DATA6Data Bus (Bit 5)26DATA7Data Bus (Bit 7; MSB)28/WRWrite Bar29/CSELChip Select Bar32ADDR0Address Bus (Bit 0; LSB)33ADDR1Address Bus (Bit 2)35ADDR3Address Bus (Bit 3)36ADDR4Address Bus (Bit 3)37ADDR5Address Bus (Bit 4)37ADDR5Address Bus (Bit 5)38ADDR6Address Bus (Bit 6; MSB)41RXTEST7Receiver Test Output (Bit 7)42RXTEST6Receiver Test Output (Bit 7)44RXTEST3Receiver Test Output (Bit 4)45RXTEST3Receiver Test Output (Bit 3)46RXTEST1Receiver Test Output (Bit 1)48RXTEST0Receiver Test Output (Bit 0)49/OENOutput Enable Bar52RXSYMPLSReceiver Symbol Pulse                                                                                                                                                                                                                                                                                                      |                 |          | Ground                        |

| 17MTXEManual Transmitter Enable18TXINTransmitter Input19TXMCHPTransmitter Manual Chip Pulse20DATA0Data Bus (Bit 0; LSB)21DATA1Data Bus (Bit 1)22DATA2Data Bus (Bit 2)23DATA3Data Bus (Bit 3)24DATA4Data Bus (Bit 4)25DATA5Data Bus (Bit 5)26DATA6Data Bus (Bit 6)27DATA7Data Bus (Bit 7; MSB)28/WRWrite Bar29/CSELChip Select Bar32ADDR0Address Bus (Bit 0; LSB)33ADDR1Address Bus (Bit 2)35ADDR3Address Bus (Bit 4)37ADDR5Address Bus (Bit 5)38ADDR6Address Bus (Bit 6; MSB)41RXTEST7Receiver Test Output (Bit 7)42RXTEST6Receiver Test Output (Bit 6)43RXTEST3Receiver Test Output (Bit 3)46RXTEST3Receiver Test Output (Bit 3)46RXTEST1Receiver Test Output (Bit 1)48RXTEST0Receiver Test Output (Bit 0)49/OENOutput Enable Bar52RXSYMPLSReceiver Symbol Pulse                                                                                                                                                                                                                                                                                                                                                                                                       | -               | TXIFCLK  | Transmitter I.F. Clock        |

| 18TXINTransmitter Input19TXMCHPTransmitter Manual Chip Pulse20DATA0Data Bus (Bit 0; LSB)21DATA1Data Bus (Bit 1)22DATA2Data Bus (Bit 2)23DATA3Data Bus (Bit 3)24DATA4Data Bus (Bit 3)25DATA5Data Bus (Bit 5)26DATA6Data Bus (Bit 7; MSB)28/WRWrite Bar29/CSELChip Select Bar32ADDR0Address Bus (Bit 0; LSB)33ADDR1Address Bus (Bit 2)35ADDR3Address Bus (Bit 3)36ADDR4Address Bus (Bit 4)37ADDR5Address Bus (Bit 5)38ADDR6Address Bus (Bit 5)41RXTEST6Receiver Test Output (Bit 7)42RXTEST5Receiver Test Output (Bit 5)44RXTEST4Receiver Test Output (Bit 3)46RXTEST2Receiver Test Output (Bit 3)46RXTEST1Receiver Test Output (Bit 1)48RXTEST0Receiver Test Output (Bit 0)49/OENOutput Enable Bar52RXSYMPLSReceiver Symbol Pulse                                                                                                                                                                                                                                                                                                                                                                                                                                        | 16              | /RESET   | /Reset                        |

| 19TXMCHPTransmitter Manual Chip Pulse20DATA0Data Bus (Bit 0; LSB)21DATA1Data Bus (Bit 1)22DATA2Data Bus (Bit 2)23DATA3Data Bus (Bit 3)24DATA4Data Bus (Bit 4)25DATA5Data Bus (Bit 5)26DATA6Data Bus (Bit 7; MSB)28/WRWrite Bar29/CSELChip Select Bar32ADDR0Address Bus (Bit 0; LSB)33ADDR1Address Bus (Bit 2)35ADDR3Address Bus (Bit 3)36ADDR4Address Bus (Bit 3)37ADDR5Address Bus (Bit 5)38ADDR6Address Bus (Bit 6; MSB)41RXTEST7Receiver Test Output (Bit 7)42RXTEST6Receiver Test Output (Bit 6)43RXTEST3Receiver Test Output (Bit 3)46RXTEST2Receiver Test Output (Bit 3)46RXTEST1Receiver Test Output (Bit 1)48RXTEST0Receiver Test Output (Bit 0)49/OENOutput Enable Bar52RXSYMPLSReceiver Symbol Pulse                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 17              | MTXE     | Manual Transmitter Enable     |

| 20DATA0Data Bus (Bit 0; LSB)21DATA1Data Bus (Bit 1)22DATA2Data Bus (Bit 2)23DATA3Data Bus (Bit 3)24DATA4Data Bus (Bit 4)25DATA5Data Bus (Bit 5)26DATA6Data Bus (Bit 7; MSB)28/WRWrite Bar29/CSELChip Select Bar32ADDR0Address Bus (Bit 0; LSB)33ADDR1Address Bus (Bit 2)35ADDR3Address Bus (Bit 3)36ADDR4Address Bus (Bit 4)37ADDR5Address Bus (Bit 5)38ADDR6Address Bus (Bit 6; MSB)41RXTEST7Receiver Test Output (Bit 7)42RXTEST6Receiver Test Output (Bit 6)43RXTEST3Receiver Test Output (Bit 3)46RXTEST3Receiver Test Output (Bit 2)47RXTEST1Receiver Test Output (Bit 1)48RXTEST0Receiver Test Output (Bit 0)49/OENOutput Enable Bar52RXSYMPLSReceiver Symbol Pulse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 18              | TXIN     | Transmitter Input             |

| 21DATA1Data Bus (Bit 1)22DATA2Data Bus (Bit 2)23DATA3Data Bus (Bit 3)24DATA4Data Bus (Bit 4)25DATA5Data Bus (Bit 5)26DATA6Data Bus (Bit 6)27DATA7Data Bus (Bit 7; MSB)28/WRWrite Bar29/CSELChip Select Bar32ADDR0Address Bus (Bit 0; LSB)33ADDR1Address Bus (Bit 2)35ADDR3Address Bus (Bit 3)36ADDR4Address Bus (Bit 4)37ADDR5Address Bus (Bit 5)38ADDR6Address Bus (Bit 6; MSB)41RXTEST7Receiver Test Output (Bit 7)42RXTEST5Receiver Test Output (Bit 5)44RXTEST4Receiver Test Output (Bit 3)46RXTEST3Receiver Test Output (Bit 2)47RXTEST1Receiver Test Output (Bit 1)48RXTEST0Receiver Test Output (Bit 0)49/OENOutput Enable Bar52RXSYMPLSReceiver Symbol Pulse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 19              | TXMCHP   | Transmitter Manual Chip Pulse |

| 22DATA2Data Bus (Bit 2)23DATA3Data Bus (Bit 3)24DATA4Data Bus (Bit 4)25DATA5Data Bus (Bit 5)26DATA6Data Bus (Bit 7; MSB)28/WRWrite Bar29/CSELChip Select Bar32ADDR0Address Bus (Bit 0; LSB)33ADDR1Address Bus (Bit 2)35ADDR3Address Bus (Bit 3)36ADDR4Address Bus (Bit 3)37ADDR5Address Bus (Bit 6; MSB)41RXTEST7Receiver Test Output (Bit 7)42RXTEST6Receiver Test Output (Bit 5)44RXTEST3Receiver Test Output (Bit 3)46RXTEST3Receiver Test Output (Bit 3)46RXTEST1Receiver Test Output (Bit 1)48RXTEST0Receiver Test Output (Bit 1)49/OENOutput Enable Bar52RXSYMPLSReceiver Symbol Pulse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 20              | DATA0    | Data Bus (Bit 0; LSB)         |

| 23DATA3Data Bus (Bit 3)24DATA4Data Bus (Bit 4)25DATA5Data Bus (Bit 5)26DATA6Data Bus (Bit 6)27DATA7Data Bus (Bit 7; MSB)28/WRWrite Bar29/CSELChip Select Bar32ADDR0Address Bus (Bit 0; LSB)33ADDR1Address Bus (Bit 2)35ADDR2Address Bus (Bit 2)36ADDR4Address Bus (Bit 3)36ADDR5Address Bus (Bit 5)38ADDR6Address Bus (Bit 6; MSB)41RXTEST7Receiver Test Output (Bit 7)42RXTEST6Receiver Test Output (Bit 5)44RXTEST3Receiver Test Output (Bit 3)46RXTEST2Receiver Test Output (Bit 3)46RXTEST1Receiver Test Output (Bit 1)48RXTEST0Receiver Test Output (Bit 0)49/OENOutput Enable Bar52RXSYMPLSReceiver Symbol Pulse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 21              | DATA1    | Data Bus (Bit 1)              |

| 24DATA4Data Bus (Bit 4)25DATA5Data Bus (Bit 5)26DATA6Data Bus (Bit 6)27DATA7Data Bus (Bit 7; MSB)28/WRWrite Bar29/CSELChip Select Bar32ADDR0Address Bus (Bit 0; LSB)33ADDR1Address Bus (Bit 2)35ADDR2Address Bus (Bit 2)36ADDR4Address Bus (Bit 3)36ADDR5Address Bus (Bit 5)38ADDR6Address Bus (Bit 6; MSB)41RXTEST7Receiver Test Output (Bit 7)42RXTEST6Receiver Test Output (Bit 5)44RXTEST3Receiver Test Output (Bit 3)46RXTEST2Receiver Test Output (Bit 2)47RXTEST1Receiver Test Output (Bit 1)48RXTEST0Receiver Test Output (Bit 0)49/OENOutput Enable Bar52RXSYMPLSReceiver Symbol Pulse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 22              | DATA2    | Data Bus (Bit 2)              |

| 25DATA5Data Bus (Bit 5)26DATA6Data Bus (Bit 6)27DATA7Data Bus (Bit 7; MSB)28/WRWrite Bar29/CSELChip Select Bar32ADDR0Address Bus (Bit 0; LSB)33ADDR1Address Bus (Bit 1)34ADDR2Address Bus (Bit 2)35ADDR3Address Bus (Bit 3)36ADDR4Address Bus (Bit 4)37ADDR5Address Bus (Bit 5)38ADDR6Address Bus (Bit 6; MSB)41RXTEST7Receiver Test Output (Bit 7)42RXTEST6Receiver Test Output (Bit 5)44RXTEST3Receiver Test Output (Bit 3)46RXTEST2Receiver Test Output (Bit 3)46RXTEST1Receiver Test Output (Bit 1)48RXTEST0Receiver Test Output (Bit 0)49/OENOutput Enable Bar52RXSYMPLSReceiver Symbol Pulse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 23              | DATA3    | Data Bus (Bit 3)              |

| 26DATA6Data Bus (Bit 6)27DATA7Data Bus (Bit 7; MSB)28/WRWrite Bar29/CSELChip Select Bar32ADDR0Address Bus (Bit 0; LSB)33ADDR1Address Bus (Bit 1)34ADDR2Address Bus (Bit 2)35ADDR3Address Bus (Bit 3)36ADDR4Address Bus (Bit 4)37ADDR5Address Bus (Bit 5)38ADDR6Address Bus (Bit 6; MSB)41RXTEST7Receiver Test Output (Bit 7)42RXTEST6Receiver Test Output (Bit 5)44RXTEST4Receiver Test Output (Bit 4)45RXTEST3Receiver Test Output (Bit 3)46RXTEST2Receiver Test Output (Bit 2)47RXTEST1Receiver Test Output (Bit 1)48RXTEST0Receiver Test Output (Bit 0)49/OENOutput Enable Bar52RXSYMPLSReceiver Symbol Pulse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 24              | DATA4    | Data Bus (Bit 4)              |

| 27DATA7Data Bus (Bit 7; MSB)28/WRWrite Bar29/CSELChip Select Bar32ADDR0Address Bus (Bit 0; LSB)33ADDR1Address Bus (Bit 1)34ADDR2Address Bus (Bit 2)35ADDR3Address Bus (Bit 3)36ADDR4Address Bus (Bit 4)37ADDR5Address Bus (Bit 5)38ADDR6Address Bus (Bit 6; MSB)41RXTEST7Receiver Test Output (Bit 7)42RXTEST6Receiver Test Output (Bit 6)43RXTEST3Receiver Test Output (Bit 4)45RXTEST2Receiver Test Output (Bit 3)46RXTEST2Receiver Test Output (Bit 2)47RXTEST1Receiver Test Output (Bit 1)48RXTEST0Receiver Test Output (Bit 0)49/OENOutput Enable Bar52RXSYMPLSReceiver Symbol Pulse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 25              | DATA5    | Data Bus (Bit 5)              |

| 28/WRWrite Bar29/CSELChip Select Bar32ADDR0Address Bus (Bit 0; LSB)33ADDR1Address Bus (Bit 1)34ADDR2Address Bus (Bit 2)35ADDR3Address Bus (Bit 3)36ADDR4Address Bus (Bit 4)37ADDR5Address Bus (Bit 5)38ADDR6Address Bus (Bit 6; MSB)41RXTEST7Receiver Test Output (Bit 7)42RXTEST6Receiver Test Output (Bit 5)44RXTEST3Receiver Test Output (Bit 4)45RXTEST3Receiver Test Output (Bit 3)46RXTEST1Receiver Test Output (Bit 1)48RXTEST0Receiver Test Output (Bit 0)49/OENOutput Enable Bar52RXSYMPLSReceiver Symbol Pulse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 26              | DATA6    | Data Bus (Bit 6)              |

| 29/CSELChip Select Bar32ADDR0Address Bus (Bit 0; LSB)33ADDR1Address Bus (Bit 1)34ADDR2Address Bus (Bit 2)35ADDR3Address Bus (Bit 3)36ADDR4Address Bus (Bit 4)37ADDR5Address Bus (Bit 5)38ADDR6Address Bus (Bit 6; MSB)41RXTEST7Receiver Test Output (Bit 7)42RXTEST6Receiver Test Output (Bit 6)43RXTEST5Receiver Test Output (Bit 5)44RXTEST4Receiver Test Output (Bit 3)46RXTEST2Receiver Test Output (Bit 2)47RXTEST1Receiver Test Output (Bit 1)48RXTEST0Receiver Test Output (Bit 0)49/OENOutput Enable Bar52RXSYMPLSReceiver Symbol Pulse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 27              | DATA7    | Data Bus (Bit 7; MSB)         |

| 32ADDR0Address Bus (Bit 0; LSB)33ADDR1Address Bus (Bit 1)34ADDR2Address Bus (Bit 2)35ADDR3Address Bus (Bit 3)36ADDR4Address Bus (Bit 4)37ADDR5Address Bus (Bit 5)38ADDR6Address Bus (Bit 6; MSB)41RXTEST7Receiver Test Output (Bit 7)42RXTEST6Receiver Test Output (Bit 6)43RXTEST5Receiver Test Output (Bit 5)44RXTEST4Receiver Test Output (Bit 3)46RXTEST2Receiver Test Output (Bit 2)47RXTEST1Receiver Test Output (Bit 1)48RXTEST0Receiver Test Output (Bit 0)49/OENOutput Enable Bar52RXSYMPLSReceiver Symbol Pulse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 28              | /WR      | Write Bar                     |

| 33ADDR1Address Bus (Bit 1)34ADDR2Address Bus (Bit 2)35ADDR3Address Bus (Bit 3)36ADDR4Address Bus (Bit 4)37ADDR5Address Bus (Bit 5)38ADDR6Address Bus (Bit 6; MSB)41RXTEST7Receiver Test Output (Bit 7)42RXTEST6Receiver Test Output (Bit 6)43RXTEST5Receiver Test Output (Bit 5)44RXTEST4Receiver Test Output (Bit 3)46RXTEST2Receiver Test Output (Bit 2)47RXTEST1Receiver Test Output (Bit 1)48RXTEST0Receiver Test Output (Bit 0)49/OENOutput Enable Bar52RXSYMPLSReceiver Symbol Pulse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 29              | /CSEL    | Chip Select Bar               |

| 34ADDR2Address Bus (Bit 2)35ADDR3Address Bus (Bit 3)36ADDR4Address Bus (Bit 4)37ADDR5Address Bus (Bit 5)38ADDR6Address Bus (Bit 6; MSB)41RXTEST7Receiver Test Output (Bit 7)42RXTEST6Receiver Test Output (Bit 6)43RXTEST5Receiver Test Output (Bit 5)44RXTEST4Receiver Test Output (Bit 3)46RXTEST2Receiver Test Output (Bit 2)47RXTEST1Receiver Test Output (Bit 1)48RXTEST0Receiver Test Output (Bit 0)49/OENOutput Enable Bar52RXSYMPLSReceiver Symbol Pulse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 32              | ADDR0    | Address Bus (Bit 0; LSB)      |

| 35ADDR3Address Bus (Bit 3)36ADDR4Address Bus (Bit 4)37ADDR5Address Bus (Bit 5)38ADDR6Address Bus (Bit 6; MSB)41RXTEST7Receiver Test Output (Bit 7)42RXTEST6Receiver Test Output (Bit 6)43RXTEST5Receiver Test Output (Bit 5)44RXTEST4Receiver Test Output (Bit 4)45RXTEST3Receiver Test Output (Bit 3)46RXTEST2Receiver Test Output (Bit 2)47RXTEST1Receiver Test Output (Bit 1)48RXTEST0Receiver Test Output (Bit 0)49/OENOutput Enable Bar52RXSYMPLSReceiver Symbol Pulse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 33              | ADDR1    | Address Bus (Bit 1)           |

| 36ADDR4Address Bus (Bit 4)37ADDR5Address Bus (Bit 5)38ADDR6Address Bus (Bit 6; MSB)41RXTEST7Receiver Test Output (Bit 7)42RXTEST6Receiver Test Output (Bit 6)43RXTEST5Receiver Test Output (Bit 5)44RXTEST4Receiver Test Output (Bit 4)45RXTEST3Receiver Test Output (Bit 3)46RXTEST2Receiver Test Output (Bit 2)47RXTEST1Receiver Test Output (Bit 1)48RXTEST0Receiver Test Output (Bit 0)49/OENOutput Enable Bar52RXSYMPLSReceiver Symbol Pulse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 34              | ADDR2    | Address Bus (Bit 2)           |

| 37ADDR5Address Bus (Bit 5)38ADDR6Address Bus (Bit 6; MSB)41RXTEST7Receiver Test Output (Bit 7)42RXTEST6Receiver Test Output (Bit 6)43RXTEST5Receiver Test Output (Bit 5)44RXTEST4Receiver Test Output (Bit 4)45RXTEST3Receiver Test Output (Bit 3)46RXTEST2Receiver Test Output (Bit 2)47RXTEST1Receiver Test Output (Bit 1)48RXTEST0Receiver Test Output (Bit 0)49/OENOutput Enable Bar52RXSYMPLSReceiver Symbol Pulse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 35              | ADDR3    | Address Bus (Bit 3)           |

| 38ADDR6Address Bus (Bit 6; MSB)41RXTEST7Receiver Test Output (Bit 7)42RXTEST6Receiver Test Output (Bit 6)43RXTEST5Receiver Test Output (Bit 5)44RXTEST4Receiver Test Output (Bit 4)45RXTEST3Receiver Test Output (Bit 3)46RXTEST2Receiver Test Output (Bit 2)47RXTEST1Receiver Test Output (Bit 1)48RXTEST0Receiver Test Output (Bit 0)49/OENOutput Enable Bar52RXSYMPLSReceiver Symbol Pulse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 36              |          | Address Bus (Bit 4)           |

| 41RXTEST7Receiver Test Output (Bit 7)42RXTEST6Receiver Test Output (Bit 6)43RXTEST5Receiver Test Output (Bit 5)44RXTEST4Receiver Test Output (Bit 4)45RXTEST3Receiver Test Output (Bit 3)46RXTEST2Receiver Test Output (Bit 2)47RXTEST1Receiver Test Output (Bit 1)48RXTEST0Receiver Test Output (Bit 0)49/OENOutput Enable Bar52RXSYMPLSReceiver Symbol Pulse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 37              | ADDR5    | Address Bus (Bit 5)           |

| 42RXTEST6Receiver Test Output (Bit 6)43RXTEST5Receiver Test Output (Bit 5)44RXTEST4Receiver Test Output (Bit 4)45RXTEST3Receiver Test Output (Bit 3)46RXTEST2Receiver Test Output (Bit 2)47RXTEST1Receiver Test Output (Bit 1)48RXTEST0Receiver Test Output (Bit 0)49/OENOutput Enable Bar52RXSYMPLSReceiver Symbol Pulse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 |          |                               |

| 43RXTEST5Receiver Test Output (Bit 5)44RXTEST4Receiver Test Output (Bit 4)45RXTEST3Receiver Test Output (Bit 3)46RXTEST2Receiver Test Output (Bit 2)47RXTEST1Receiver Test Output (Bit 1)48RXTEST0Receiver Test Output (Bit 0)49/OENOutput Enable Bar52RXSYMPLSReceiver Symbol Pulse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                 |          |                               |

| 44RXTEST4Receiver Test Output (Bit 4)45RXTEST3Receiver Test Output (Bit 3)46RXTEST2Receiver Test Output (Bit 2)47RXTEST1Receiver Test Output (Bit 1)48RXTEST0Receiver Test Output (Bit 0)49/OENOutput Enable Bar52RXSYMPLSReceiver Symbol Pulse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                 |          |                               |

| 45RXTEST3Receiver Test Output (Bit 3)46RXTEST2Receiver Test Output (Bit 2)47RXTEST1Receiver Test Output (Bit 1)48RXTEST0Receiver Test Output (Bit 0)49/OENOutput Enable Bar52RXSYMPLSReceiver Symbol Pulse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                 |          |                               |

| 46RXTEST2Receiver Test Output (Bit 2)47RXTEST1Receiver Test Output (Bit 1)48RXTEST0Receiver Test Output (Bit 0)49/OENOutput Enable Bar52RXSYMPLSReceiver Symbol Pulse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                 | RXTEST4  |                               |

| 47RXTEST1Receiver Test Output (Bit 1)48RXTEST0Receiver Test Output (Bit 0)49/OENOutput Enable Bar52RXSYMPLSReceiver Symbol Pulse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                 | RXTEST3  |                               |

| 48RXTEST0Receiver Test Output (Bit 0)49/OENOutput Enable Bar52RXSYMPLSReceiver Symbol Pulse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                 |          | ,                             |

| 49/OENOutput Enable Bar52RXSYMPLSReceiver Symbol Pulse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                 |          |                               |

| 52 RXSYMPLS Receiver Symbol Pulse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 |          |                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                 |          | •                             |

| 53 RXSPLPLS Receiver Sample Pulse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 |          | -                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 53              | RXSPLPLS | Receiver Sample Pulse         |

#### Table 1. 100-Pin PQFP Pin Description

| No    | Symbol   | Function                            |

|-------|----------|-------------------------------------|

| 54    | /RXDRDY  | Receiver Data Ready Bar             |

| 55    | RXQOUT   | Receiver Q Channel Output           |

| 56    | RXIOUT   | Receiver I Channel Output           |

| 57    | RXOUT    | Receiver Output                     |

| 58    | I.C.     | [Note]                              |

| 59    | TXTEST   | Transmitter Test Output             |

| 60    | TXACQPLS | Transmitter Acquisition Pulse       |

| 61    | TXTRKPLS | Transmitter Data Track Pulse        |

| 62    | TXCHPPLS | Transmitter Chip Pulse              |

| 63    | TXBITPLS | Transmitter Bit Pulse               |

| 66    | TXIFOUT7 | Tx I.F. Output (Bit 7, MSB)         |

| 67    | TXIFOUT6 | Tx I.F. Output (Bit 6)              |

| 68    | TXIFOUT5 | Tx I.F. Output (Bit 5)              |

| 69    | TXIFOUT4 | Tx I.F. Output (Bit 4)              |

| 70    | TXIFOUT3 | Tx I.F. Output (Bit 3)              |

| 71    | TXIFOUT2 | Tx I.F. Output (Bit 2)              |

| 72    | TXIFOUT1 | Tx I.F. Output (Bit 1)              |

| 73    | TXIFOUT0 | Tx I.F. Output (Bit 0, LSB)         |

| 76    | TXQOUT   | Tx Q-Channel Output                 |

| 77    | TXIOUT   | Tx I-Channel Output                 |

| 78    | TXACTIVE | Transmitter Active                  |

| 79,82 | N.C.     | No Connection                       |

| 83    | RXACTIVE | Receiver Active                     |

| 84    | RXMSMPL  | Receiver Manual Sample Clock        |

| 85    | MFLD     | Manual Frequency Load               |

| 86    | MNCOEN   | Manual NCO Enable                   |

| 87    | RXMABRT  | Receiver Manual Abort               |

| 88    | RXMDET   | Receiver Manual Detect              |

| 91    | RXIIN0   | Rx I-Channel Input<br>(Bit 0; LSB)  |

| 92    | RXIIN1   | Rx I-Channel Input (Bit 1)          |

| 93    | RXIIN2   | Rx I-Channel Input (Bit 2)          |

| 94    | RXIIN3   | Rx I-Channel Input (Bit 3)          |

| 95    | RXIIN4   | Rx I-Channel Input (Bit 4)          |

| 96    | RXIIN5   | Rx I-Channel Input (Bit 5)          |

| 97    | RXIIN6   | Rx I-Channel Input (Bit 6)          |

| 98    | RXIIN7   | Rx I-Channel Input (<br>Bit 7; MSB) |

| 99    | N.C.     | No Connection                       |

| 100   | V<br>SS  | Ground                              |

Note: I.C. denotes Internal Connection. Do not use for vias.

#### ABSOLUTE MAXIMUM RATINGS

| Symbol                | Parameter                         | Range                      | Units     |

|-----------------------|-----------------------------------|----------------------------|-----------|

| T <sub>STG</sub>      | Storage Temperature               | –55 to +150                | °C        |

| V <sub>DD</sub> (max) | Supply Voltage on V <sub>DE</sub> | <sub>0</sub> –0.3 to + 7   | Volts     |

| V <sub>I</sub> (max)  | Input Voltage                     | -0.3 to V <sub>DD</sub> +0 | ).3 Volts |

| I                     | DC Input Current                  | ±10                        | mA        |

| T <sub>A</sub>        | Operating<br>Temperature (Ambient | 0 to +70<br>:)             | °C        |

Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; operation of the device at any condition above those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended period may affect device reliability.

#### **D.C. CHARACTERISTICS**

Operating Conditions: V\_DD = 5.0V  $\pm 5\%,$  V\_SS = 0V

|                       | Parameter                       | $T_A = 0^\circ t$    | to +70°C            | Тур    |          |                                                                    |

|-----------------------|---------------------------------|----------------------|---------------------|--------|----------|--------------------------------------------------------------------|

| Symbol                |                                 | Min                  | Max                 | @ 25°C | Units    | Conditions                                                         |

| I <sub>DDQ</sub>      | Supply Current,<br>Quiescent    |                      | 1.0                 |        | mA       | Static, no clock                                                   |

| I <sub>DD</sub>       | Supply Current,<br>Operational  |                      | 380<br>170          | [Note] | mA<br>mA | f <sub>RXIFCLK</sub> = 45.056 MHz<br>f <sub>RXIFCLK</sub> = 20 MHz |

| V <sub>IH</sub> (min) | High Level Input<br>Voltage     | 0.7V <sub>DD</sub>   | V <sub>DD</sub> +.3 | 2.6    | Volts    | Logic '1'                                                          |

| V <sub>IL</sub> (min) | Low Level Input Voltage         | V <sub>SS</sub> –.3  | 0.2V <sub>DD</sub>  | 1.5    | Volts    | Logic '0'                                                          |

| I <sub>IH</sub> (min) | High Level Input<br>Current     |                      | 10                  |        | μA       | All inputs, $V_{IN} = V_{DD}$                                      |