# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### CEL California Eastern Laboratories

#### APPLICATIONS

- Home Automation and Security

- Automatic Meter Reading

- Factory Automation and Motor Control

- Medical Patient Monitoring

- Voice Applications

- Replacement for legacy wired UART

- Energy Management

- Remote Keyless Entry w/ Acknowledgement

- Toys

- PC peripherals

#### **KEY FEATURES**

- Embedded 8051 Compatible Microprocessor with 96KB Embedded Flash Memory for Program Space plus 8KB of Data Memory

- Scalable Data Rate: 250kbps for ZigBee, 500kbps and 1Mbps for custom applications.

- Voice Codec Support: μ-law/a-law/ADPCM

- High RF RX Sensitivity: -98dBm @1.5V

- High RF TX Power: +8dBm @1.5V

- 4 Level Power Management Scheme with Deep Sleep Mode (0.3µA)

- Single Voltage operation: 1.9 to 3.3V using an internal regulator (1.5V core)

- Software Tools and Libraries for the Development of Custom Applications

#### DESCRIPTION:

**ZIC2410** is a true single-chip solution, compliant with ZigBee specifications and IEEE802.15.4, a complete wireless solution for all ZigBee applications. The **ZIC2410** consists of an RF transceiver with baseband modem, a hardwired MAC and an embedded 8051 microcontroller with internal flash memory. The device provides numerous general-purpose I/O pins,

#### peripheral functions such as timers and UART and is one of the first devices to provide an embedded Voice CODEC. This chip is ideal for very low power applications.

ZIC2410 Datasheet

The *ZIC2410* is available in two industry standard packages: a 48-pin QFN (7x7mm) or a 72-pin VFBGA (5x5mm) package.

CEL provides its customers with the *CEL ZigBee Stack*, software in a compiled library, as well as all the hardware & software tools required to develop custom applications. User application software can be compiled using any popular C-language compiler such as Keil.

#### **RF Transceiver**

- Single-chip 2.4GHz RF Transceiver

- Programmable Output Power up to +8dBm@1.5V

- High Sensitivity of –98dBm@1.5V

- Scalable Data Rate: 250Kbps for ZigBee, 500Kbps and 1Mbps for custom application

- On-chip VCO, LNA, and PA

- Low Operating Voltage of 1.5V

- Direct Sequence Spread Spectrum

- O-QPSK Modulation

- RSSI Measurement

- Compliant to IEEE802.15.4

- No External T/R Switch or Filter needed

#### Hardwired MAC

- Two 256-byte circular FIFOs

- FIFO management

- AES Encryption/Decryption Engine (128bit)

- CRC-16 Computation and Check

#### 8051-Compatible Microcontroller

- 8051 Compatible (single cycle execution)

- 96KB Embedded Flash Memory

- 8KB Data Memory

- 128-byte CPU dedicated Memory

- 1KB Boot ROM

- Dual DPTR Support

- Multi-Bank Support for 96KB Program Memory (3Banks of 32KB)

- I2S/PCM Interface with two128-byte FIFOs

- µ-law/a-law/ADPCM Voice Codec

- Two High-Speed UARTs with Two 16-byte FIFOs (up to 1Mbps)

- 4 Timers/2 PWMs

- Watchdog Timer

- Sleep Timer

- Quadrature Signal Decoder

- 24 General Purpose I/Os

- Internal RC oscillator for Sleep Timer

- On-chip Power-on-Reset

- 4-channel 8-bit ADC

- SPI Master/Slave Interface

- ISP (In System Programming)

- Internal Temperature Sensor

#### **Clock Inputs**

- 16MHz Crystal for System Clock (optional 19.2MHz)

- 32.768KHz Crystal for Sleep Timer (optional)

#### Power

- Internal Regulator for Single Voltage Operation w/ a large input voltage range (1.9~3.3V)

- 4-Level Power Management Scheme with Deep Sleep Mode (0.3µA)

- Separate On-chip Regulators for Analog and Digital Circuitry.

- Battery Monitoring Support

#### **Included Software**

- Application Framework

- Software Tools

- IEEE and ZigBee Compliant Libraries

#### **Package Options**

- Lead-Free 48-pin QFN Package (shown below)

(7mm x 7mm x 0.9mm)

- Lead-Free 72-pin VFBGA Package (5mm × 5mm x 0.9mm)

#### **ORDERING INFORMATION**

| Ordering Part Number | Description                | Minimum Order Quantity (MOQ) |

|----------------------|----------------------------|------------------------------|

| ZIC2410QN48R         | 48-pin QFN Package (T/R)   | Tape & Reel (2500 per reel)  |

| ZIC2410FG72R         | 72-pin VFBGA Package (T/R) | Tape & Reel (2500 per reel)  |

| ZIC2410-EDK-1        | Demonstration Kit          | 1                            |

### **Table of Contents**

| 1 | FUNCTIONAL DESCRIPTION                                                                                 | 5  |

|---|--------------------------------------------------------------------------------------------------------|----|

|   | 1.1 FUNCTIONAL OVERVIEW                                                                                | 6  |

|   | 1.2 MEMORY ORGANIZATION                                                                                |    |

|   | 1.2.1 PROGRAM MEMORY                                                                                   |    |

|   |                                                                                                        | 8  |

|   | <ul><li>1.2.3 GENERAL PURPOSE REGISTERS (GPR)</li><li>1.2.4 SPECIAL FUNCTION REGISTERS (SFR)</li></ul> |    |

|   | 1.3 RESET                                                                                              |    |

|   | 1.4 CLOCK SOURCE                                                                                       |    |

|   | 1.5 INTERRUPT SCHEMES                                                                                  |    |

|   | 1.6 POWER MANAGEMENT                                                                                   |    |

|   | 1.7 ON-CHIP PERIPHERALS                                                                                |    |

|   | 1.7.1 TIMER 0/1                                                                                        |    |

|   | 1.7.2 TIMER 2/3, PWN 2/3                                                                               |    |

|   | 1.7.3 WATCHDOG TIMER                                                                                   |    |

|   | 1.7.4 SLEEP TIMER                                                                                      |    |

|   | 1.7.5 INTERNAL RC OSCILLATOR<br>1.7.6 UART0/1                                                          |    |

|   | 1.7.7 SPI MASTER/SLAVE                                                                                 |    |

|   | 1.7.8 VOICE                                                                                            |    |

|   | 1.7.9 RANDOM NUMBER GENERATOR (RNG)                                                                    |    |

|   | 1.7.10 QUAD DECODER                                                                                    |    |

|   | 1.7.11 INTERNAL VOLTAGE REGULATOR                                                                      | 53 |

|   | 1.7.12 4-CHANNEL 8-BIT SENSOR ADC                                                                      |    |

|   | 1.7.13 ON-CHIP POWER-ON RESET<br>1.7.14 TEMPERATURE SENSOR                                             |    |

|   | 1.7.14 TEMPERATURE SENSOR                                                                              |    |

|   | 1.8 MEDIUM ACCESS CONTROL LAYER (MAC)                                                                  |    |

|   | 1.8.1 RECEIVED MODE                                                                                    |    |

|   | 1.8.2 TRANSMIT MODE                                                                                    | 60 |

|   | 1.8.3 DATA ENCRYPTION AND DECRYPTION                                                                   | 60 |

|   | 1.9 PHYSICAL LAYER (PHY)                                                                               |    |

|   | 1.9.1 INTERRUPT                                                                                        |    |

|   | 1.9.2 REGISTERS                                                                                        |    |

|   | 1.10 IN-SYSTEM PROGRAMMING (ISP)                                                                       |    |

|   | <ul><li>1.11 ZIC2410 INSTRUCTION SET SUMMARY</li><li>1.12 DIGITAL I/O</li></ul>                        |    |

| _ |                                                                                                        |    |

| 2 | AC & DC CHARACTERISTICS                                                                                | 93 |

|   | 2.1 ABSOLUTE MAXIMUM RATINGS                                                                           |    |

|   | 2.2 DC CHARACTERISTICS                                                                                 |    |

|   | 2.3 ELECTRICAL SPECIFICATIONS                                                                          |    |

|   | 2.3.1 ELECTRICAL SPECIFICATIONS with an 8MHz CLOCK                                                     |    |

|   | 2.3.2 ELECTRICAL SPECIFICATIONS with a 16MHz CLOCK                                                     |    |

|   | 2.3.3 AC CHARACTERISTICS                                                                               |    |

| 3 | PACKAGE & PIN DESCRIPTIONS                       | 101 |

|---|--------------------------------------------------|-----|

|   | 3.1 PIN ASSIGNMENTS                              | 101 |

|   | 3.1.1 QN48 Package                               | 101 |

|   | 3.1.2 FG72 Package                               | 104 |

|   | 3.2 PACKAGE INFORMATION                          | 107 |

|   | 3.2.1 PACKAGE INFORMATION: ZIC2410QN48 (QN48pkg) | 107 |

|   | 3.2.2 PACKAGE INFORMATION: ZIC2410FG72 (FG72pkg) | 110 |

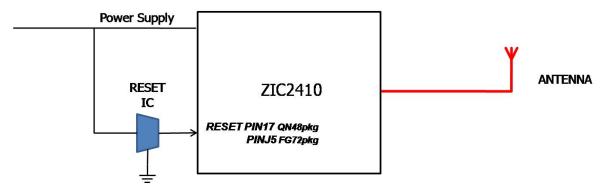

|   | 3.3 APPLICATION CIRCUITS                         | 112 |

|   | 3.3.1 APPLICATION CIRCUITS (QN48 package)        | 112 |

|   | 3.3.2 APPLICATION CIRCUITS (FG72 package)        | 114 |

| 4 | REFERENCES                                       | 116 |

|   | 4.1 TABLE OF TABLES                              |     |

|   | 4.2 TABLE OF FIGURES                             |     |

|   | 4.3 TABLE OF EQUATIONS                           |     |

| 5 | REVISION HISTORY                                 | 119 |

#### **1** FUNCTIONAL DESCRIPTION

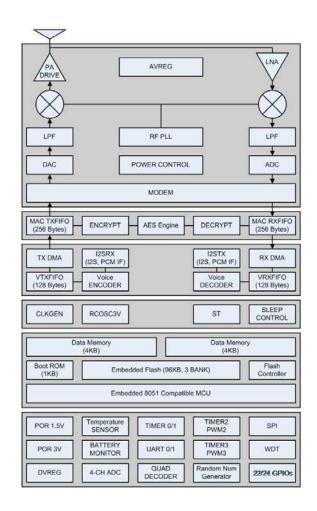

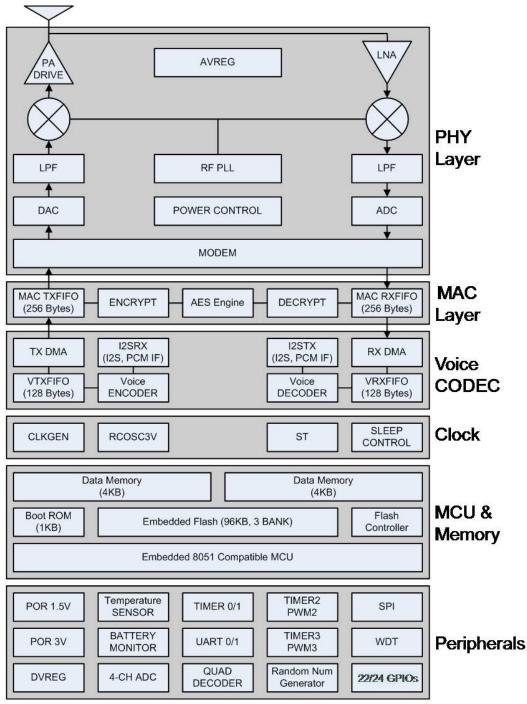

Figure 1 shows the block diagram of ZIC2410. The ZIC2410 consists of a 2.4GHz RF, Modem (PHY Layer), a MAC hardware engine, a Voice CODEC block, Clocks, Peripherals, and a memory and Microcontroller (MCU) block.

**Figure 1 – Functional Block Diagram of ZIC2410 Note:** The ZIC2410QN48 has 22 GPIOs; the ZIC2410FG72 has 24.

#### **1.1 FUNCTIONAL OVERVIEW**

In the receive mode, the received RF signal is amplified by the Low Noise Amplifier (LNA), down-converted to a quadrature signal and then to baseband. The baseband signal is filtered, amplified, converted to a digital signal by the ADC and transferred to a modem. The data, which is the result of signal processing such as dispreading, is transferred to the MAC block.

In transmit mode, the buffered data at the MAC is transferred to a baseband modem which, after signal processing such as spreading and pulse shaping, outputs a signal through the DAC. The Analog baseband signal is filtered by the low-pass filter, converted to RF signal by the up-conversion mixer, is amplified by PA, and finally applied to the antenna.

The MAC block provides IEEE802.15.4 compliant hardware and it is located between microprocessor and a baseband modem. MAC block includes FIFOs for transmitting/receiving packet, AES engine for security operation, CRC and related control circuit. In addition, it supports automatic CRC check and address decoding.

ZIC2410 integrates a high performance embedded microcontroller, compatible to an Intel i8051 microcontroller in an instruction level. This embedded microcontroller has 8-bit operation architecture sufficient for controller applications. The embedded microcontroller has 4-stage pipeline architecture to improve the performance over previous compatible chips making it capable of executing simple instructions during a single cycle.

The memory organization of the embedded microcontroller consists of program memory and data memory. The data memory has 2 memory areas. For more detailed explanation, refer to the data memory section (1.2.2.)

The ZIC2410 includes 22 GPIO for the QN48 packaged device and 24 GPIO for the FG72 packaged part and various peripheral circuits to aid in the development of an application circuit with an interrupt handler to control the peripherals. ZIC2410 uses 16MHz crystal oscillator for RF PLL and 8MHz clock generated from 16MHz in clock generator is used for microcontroller, MAC, and the clock of a baseband modem.

The ZIC2410 supports a voice function as follows. The data generated by an external ADC is input to the voice block via I2S interface. After the data is received via I2S it is compressed by the voice codec, and stored in Voice TXFIFO. The data in Voice TXFIFO is transferred to the MAC TXFIFO and then transmitted via PHY. In contrast, the received data in MAC RXFIFO is transferred to voice RXFIFO via DMA operation. The data in voice RXFIFO is decompressed by the internal voice codec. The decompressed data is then transferred to the external DAC via I2S interface.

#### **1.2 MEMORY ORGANIZATION**

#### 1.2.1 PROGRAM MEMORY

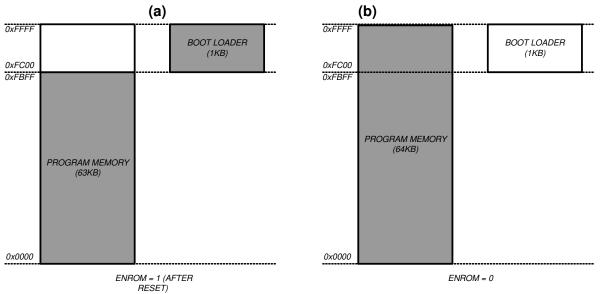

The address space of the program memory is 64KB (0x0000~0XFFFF). Basically, the lower 63KB of program memory is implemented by Non-volatile memory. The upper 1KB from 0XFC00 to 0XFFFF is implemented by both Non-volatile memory and ROM. As shown in Figure 2 below, there are two types of memory in the same address space. The address space, which is implemented by Non-volatile memory, is used as general program memory and the address space, which is implemented by ROM, is used for ISP (In-System Programming).

As shown in (a) of Figure 2 below, when Power is turned on, the upper 1KB of program memory is mapped to ROM. As shown in (b) of Figure 2, if this program area (1KB) is used as non-volatile program memory, ENROM should be set to '0'. See the SFR section (1.2.4) for ENROM.

Figure 2 – Address Map of Program Memory

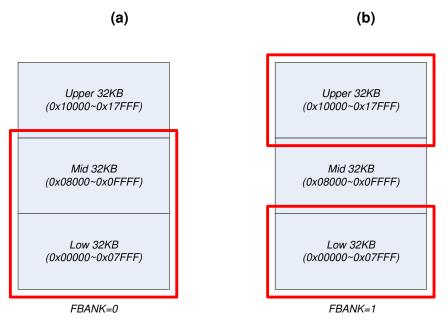

ZIC2410 includes non-volatile memory of 96KB. However, as described already, program memory area is 64KB. Therefore, if necessary, the upper 64KB of physical 96KB non-volatile memory is separated into two 32KB memory banks. Each bank is logically mapped to the program memory. When FBANK value is '0', lower 64KB of non-volatile memory is used as shown in (a) of Figure 3. When FBANK value is '1', lower 32 KB and upper 32KB of non-volatile memory are used as shown in (b) of Figure 3. See the SFR section (1.2.4) for FBANK.

Figure 3 – Bank Selection of Program Memory

#### **1.2.2 DATA MEMORY**

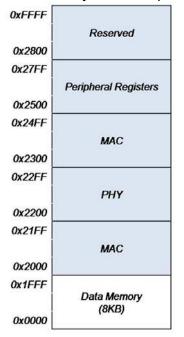

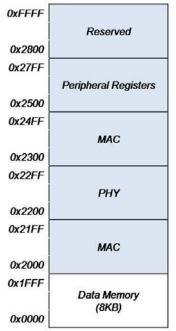

ZIC2410 reserves 64 KB of data memory address space. This address space can be accessed

by the MOVX command.

Figure 4 shows the address map of this data memory.

Figure 4 – Address Map of Data Memory

The data memory used in the application programs resides in the address range 0x0000-0x1FFF.

The registers and memory used in the MAC block reside in the address range 0x2000-0x21FF and 0x2300-0x24FF respectively. The registers to control or report the status of the PHY block reside in the address range 0x2200-0x22FF.

Registers related to the numberous peripheral functions of the embedded microprocessor reside in the address range of 0x2500-0x27FF.

#### **1.2.3 GENERAL PURPOSE REGISTERS (GPR)**

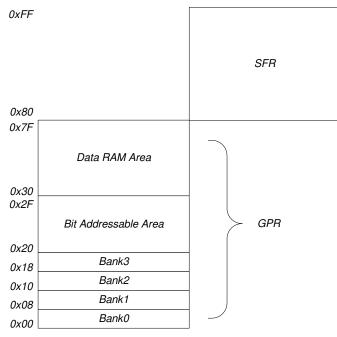

Figure 5 describes the address map of the General Purpose Registers (GPRs). GPRs can be addressed either directly or indirectly. As shown in the lower address space of Figure 5, a bank consists of 8 registers.

The address space above the bank area is the bit addressable area, which is used as a flag by software or by a bit operation. The address space above the bit addressable area includes registers used as a general purpose of a byte unit. For the detailed information, refer to the paragraphs following Figure 5 below.

Figure 5 – GPRs Address Map

**Register Bank 0-3:** It is located from 0x00 to 0x1F (32 bytes). One bank consists of each 8 registers out of 32 registers. Therefore, there are total 4 banks. Each bank should be selected by software as referring the RS field in PSW register. The bank (8 registers) selected by RS value can be accessed by a name (R0-R7) by software. After reset, the default value is set to bank0.

**Bit Addressable Area:** The address is assigned to each bit of 16 bytes (0x20-0x2F) and registers, which is the multiple of 8, in SFR. Each bit can be accessed by the address which is assigned to these bits. 128 bits (16 bytes, 0x20-0x2F) can be accessed by direct addressing for each bit (0-127) and by a byte unit as using the address from 0x20-0x2F.

**Data RAM Area:** A user can use registers (0x30~0x7F) as a general purpose.

#### **1.2.4 SPECIAL FUNCTION REGISTERS (SFR)**

Generally, a register is used to store the data. MCU needs the memory to control the embedded hardware or the memory to show the hardware status. Special Function Registers (SFRs) process the functions described above. SFRs include the status or control of the I/O ports, the timer registers, the stack pointers and so on. Table 1 shows the address to all SFRs in ZIC2410.

All SFRs are accessed by a byte unit. However, when SFR address is a multiple of 8, it can be accessed by a bit unit.

| Register<br>Name | SFR<br>Address | B7 | B6    | B5    | B4    | B3   | B2    | B1   | B0   | Initial<br>Value |

|------------------|----------------|----|-------|-------|-------|------|-------|------|------|------------------|

| EIP              | 0xF8           |    | VCEIP | SPIIP | RTCIP | T3IP | AESIP | T2IP | RFIP | 0x00             |

| В                | 0xF0           |    |       |       |       |      |       |      |      | 0x00             |

| EIE              | 0xE8           |    | VCEIE | SPIIE | RTCIE | T3IE | AESIE | T2IE | RFIE | 0x00             |

| Table 1 – Special Function Register (SFR) Map | Table 1 – | Special | Function | <b>Register</b> ( | (SFR) M | lap |

|-----------------------------------------------|-----------|---------|----------|-------------------|---------|-----|

|-----------------------------------------------|-----------|---------|----------|-------------------|---------|-----|

| Register<br>Name | SFR<br>Address | B7    | B6    | B5   | B4    | B3    | B2      | B1       | В0       | Initial<br>Value |

|------------------|----------------|-------|-------|------|-------|-------|---------|----------|----------|------------------|

| ACC              | 0xE0           |       |       |      |       |       |         |          |          | 0x00             |

| EICON            | 0xD8           |       |       |      |       | RTCIF |         |          |          | 0x00             |

| WDT              | 0xD2           |       |       |      | WDTWE | WDTEN | WDTCLR  | WD1      | IPRE     | 0x0B             |

| PSW              | 0xD0           | CY    | AC    | F0   | R     | S     | OV      | F1       | Р        | 0x00             |

| WCON             | 0xC0           |       |       |      |       |       | ISPMODE | ENROM    |          | 0x00             |

| P3REN            | 0xBC           |       |       |      |       |       |         |          |          | 0xFF             |

| P1REN            | 0xBA           |       |       |      |       |       |         |          |          | 0xFF             |

| P0REN            | 0xB9           |       |       |      |       |       |         |          |          | 0xFF             |

| IP               | 0xB8           |       | PS1   |      | PS0   | PT1   | PX1     | PT0      | PX0      | 0x00             |

| P30EN            | 0xB4           |       |       |      |       |       |         |          |          | 0x00             |

| P10EN            | 0xB2           |       |       |      |       |       |         |          |          | 0x00             |

| P00EN            | 0xB1           |       |       |      |       |       |         |          |          | 0x00             |

| P3               | 0xB0           |       |       |      |       |       |         |          |          | 0x3F             |

| TL3              | 0xAD           |       |       |      |       |       |         |          |          | 0x00             |

| TL2              | 0xAC           |       |       |      |       |       |         |          |          | 0x00             |

| TH3              | 0xAB           |       |       |      |       |       |         |          |          | 0x00             |

| TH2              | 0xAA           |       |       |      |       |       |         |          |          | 0x00             |

| T23CON           | 0xA9           |       |       |      |       | TR3   | M3      | TR2      | M2       | 0x00             |

| IE               | 0xA8           | EA    | ES1   |      | ES0   | ET1   | EX1     | ET0      | EX0      | 0x00             |

| AUXR1            | 0xA2           |       |       |      |       |       |         |          | DPS      | 0x00             |

| FBANK            | 0xA1           | RAM1  | RAM0  |      |       |       |         | FB/      | ANK      | 0x00             |

| EXIF             | 0x91           | T3IF  | AESIF | T2IF | RFIF  |       |         |          |          | 0x00             |

| P1               | 0x90           |       |       |      |       |       |         |          |          | 0xFF             |

| TH1              | 0x8D           |       |       |      |       |       |         |          |          | 0x00             |

| TH0              | 0x8C           |       |       |      |       |       |         |          |          | 0x00             |

| TL1              | 0x8B           |       |       |      |       |       |         |          |          | 0x00             |

| TL0              | 0x8A           |       |       |      |       |       |         |          |          | 0x00             |

| TMOD             | 0x89           | GATE1 | CT1   |      | M1    | GATE0 | CT0     | N        | /0       | 0x00             |

| TCON             | 0x88           | TF1   | TR1   | TF0  | TR0   | IE1   | IT1     | IE0      | IT0      | 0x00             |

| PCON             | 0x87           |       |       |      |       |       |         | PD       | IDLE     | 0x00             |

| P0SEL            | 0x85           |       |       |      |       |       |         | ExNoEdge | P0AndSEL | 0x00             |

| P0MSK            | 0x84           |       | 1     |      | 1     |       |         |          |          | 0xFF             |

| DPH              | 0x83           |       | 1     |      | 1     |       |         |          |          | 0x00             |

| DPL              | 0x82           |       |       |      | 1     |       |         |          |          | 0x00             |

| SP               | 0x81           |       |       |      | 1     |       |         |          |          | 0x07             |

| P0               | 0x80           |       |       |      |       |       |         |          |          | 0xFF             |

The following section describes each SFR related to microprocessor.

#### Table 2 – Register Bit Conventions

| Symbol | Access Mode |

|--------|-------------|

| RW     | Read/write  |

| RO     | Read Only   |

| Bit                              | Name                                                             | Descriptions                                                                                                                                                                                                                                                                                                                                             | R/W                                       | <u>Reset</u>          |

|----------------------------------|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-----------------------|

|                                  |                                                                  |                                                                                                                                                                                                                                                                                                                                                          | <u></u>                                   | Value                 |

|                                  |                                                                  | NTROL REGISTER, 0xC0)<br>ntrol the upper 1KB of program memory.                                                                                                                                                                                                                                                                                          |                                           |                       |

| 7:3                              |                                                                  | Reserved                                                                                                                                                                                                                                                                                                                                                 |                                           | 0                     |

| 2                                | ISPMODE                                                          | <b>ISP Mode Indication</b> : When MS [1:0], an external pin, is '3', this field is set to 1 by hardware. It notifies the MCU whether ISPMODE or not.                                                                                                                                                                                                     | RO                                        | -                     |

| 1                                | ENROM                                                            | When this field is '1', the upper 1KB (0xFC00~0xFFFF) is mapped to ROM. When this field is '0', the upper 1KB (0xFC00~0xFFFF) is mapped to non-volatile memory.                                                                                                                                                                                          | R/W                                       | 1                     |

| 0                                |                                                                  | Reserved                                                                                                                                                                                                                                                                                                                                                 |                                           | 0                     |

|                                  | NK (PROGRA                                                       | M MEMORY BANK SELECTION REGISTER, 0xA1)                                                                                                                                                                                                                                                                                                                  |                                           |                       |

| 7:1                              |                                                                  | Reserved                                                                                                                                                                                                                                                                                                                                                 |                                           | 0x00                  |

| 0                                | FBANK                                                            | Program Memory Bank Select.<br>0: Bank0 (Default)<br>1: Bank1<br>2: Not Used<br>3: Not Used                                                                                                                                                                                                                                                              | R/W                                       | 0                     |

| ACC                              | UMULATOR (C                                                      |                                                                                                                                                                                                                                                                                                                                                          |                                           |                       |

|                                  |                                                                  | ed as A or ACC and it is related to all the operations.                                                                                                                                                                                                                                                                                                  |                                           |                       |

| 7:0                              | Α                                                                | Accumulator                                                                                                                                                                                                                                                                                                                                              | R/W                                       | 0x00                  |

| conta<br>opera<br>time,<br>after | ains the MSB dation, this regist<br>before division<br>division. | e used as a general-purpose register. After multiplication is process<br>ata and 'A register' contains LSB data for the multiplication result. In<br>ter stores the value before division (dividend) and the remainder after<br>, the divisor should be stored in 'A register' and result value (quotier                                                 | n division<br>er divisior<br>nt) is store | . At this<br>ed in it |

| 7:0                              | В                                                                | B register. Used in MUL/DIV instructions.                                                                                                                                                                                                                                                                                                                | R/W                                       | 0x00                  |

|                                  |                                                                  | S WORD (PSW, 0xD0)<br>the status of the program. The explanation for each bit is as follows.                                                                                                                                                                                                                                                             |                                           |                       |

| 7                                | CY                                                               | Carry flag                                                                                                                                                                                                                                                                                                                                               | R/W                                       | 0                     |

| 6                                | AC                                                               | Auxiliary carry flag                                                                                                                                                                                                                                                                                                                                     | R/W                                       | 0                     |

| 5                                | F0                                                               | Flag0. User-defined                                                                                                                                                                                                                                                                                                                                      | R/W                                       | 0                     |

| 4:3                              | RS                                                               | Register bank select.<br>0: Bank0<br>1: Bank1<br>2: Bank2<br>3: Bank3                                                                                                                                                                                                                                                                                    | R/W                                       | 0                     |

| 2                                | OV                                                               | Overflow flag                                                                                                                                                                                                                                                                                                                                            | R/W                                       | 0                     |

| 1                                | F1                                                               | Flag1. User-defined                                                                                                                                                                                                                                                                                                                                      | R/W                                       | 0                     |

| 0                                | Ρ                                                                | Parity flag.<br>Set to 1 when the value in accumulator has odd number of '1'<br>bits.                                                                                                                                                                                                                                                                    | R/W                                       | 0                     |

| When<br>store<br>a ger<br>This   | d in stack to inf<br>neral purpose ((<br>register value is       | <b>0x81)</b><br>ALL commands are executed, some data (like the parameters by fur<br>form the values. In the embedded MCU, the data memory area whic<br>0x08~0x7F) is used as a stack area.<br>Is increased before the data is stored and the register value is decrea<br>ta of stack is disappeared by POP and RET command. The default<br>Stack Pointer | ch can be<br>ased afte                    | used for<br>the data  |

#### Table 3 – Special Function Registers

| <u>Bit</u>  | <u>Name</u>                        | Descriptions                                                                                                                                                                                                           | <u>R/W</u> | <u>Reset</u><br>Value |

|-------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------------------|

|             |                                    | PH: 0x83, DPL: 0x82)                                                                                                                                                                                                   |            |                       |

| acce        | ssed by 16-bit i                   | s of a high byte (DPH) and a low byte (DPL) to support 16-bit addres<br>register or by two 8-bit registers respectively.                                                                                               |            | be                    |

| 7:0         | DPH                                | Data pointer, high byte                                                                                                                                                                                                | R/W        | 0x00                  |

| 7:0         | DPL                                | Data pointer, low byte                                                                                                                                                                                                 | R/W        | 0x00                  |

| This<br>DPT | register is used<br>R1. However, I | Y CONTROL REGISTER, 0xA2)<br>I to implement Dual DPTR functions. Physically, DPTR consists of D<br>DPTR0 and DPTR1 can be accessed depending on the DPS value o<br>er words, they cannot be accessed at the same time. |            |                       |

| 7:1         | <b>,</b>                           | Reserved                                                                                                                                                                                                               |            | 0x00                  |

| 0           | DPS                                | <b>Dual DPTR Select</b> : Used to select either DPTR0 or DPTR1.<br>When DSP is '0', DPTR0 is selected. When DSP is '1', DPTR1 is selected.                                                                             | R/W        | 0                     |

|             | )xB0)                              |                                                                                                                                                                                                                        |            |                       |

| Inis        | port register ca                   | n be used as other functions besides general purpose I/O.                                                                                                                                                              |            |                       |

|             | P3.7                               | This port register is used as a general purpose I/O port (12mA Drive).                                                                                                                                                 |            |                       |

|             | /PWM3                              | When Timer3 is operated as a PWM mode, it outputs PWM wave (PWM3) of Timer3.                                                                                                                                           |            |                       |

| 7           | /CTS1                              | When port register is used as UART1, it is used as a CTS signal (CTS1) of UART1.                                                                                                                                       | R/W        | 0                     |

|             | /SPICSN                            | When used as a Master mode, SPI Slave Select signal is outputted. When used as a Slave mode, this port register receives SPI Slave Select signal. This signal activate in low                                          |            |                       |

|             | P3.6                               | This port register is used as a general purpose I/O port (12mA Drive)                                                                                                                                                  |            |                       |

|             | /PWM2                              | When Timer2 is operated as a PWM mode, it outputs PWM wave (PWM2) of Timer2.                                                                                                                                           |            |                       |

| 6           | /RTS1                              | When port register is used as UART1, it is used as a RTS signal (RTS1) of UART1.                                                                                                                                       | R/W        | 0                     |

|             | /SPICLK                            | When used as a Master mode, SPI clock is outputted. When used as a Slave mode, this port register receives SPI clock.                                                                                                  |            |                       |

|             | P3.5                               | This port register is used as a general purpose I/O port.                                                                                                                                                              |            |                       |

|             | /T1                                | When Timer1 is operated as a COUNTER mode, it is operated as a counter input signal (T1) of Timer1.                                                                                                                    |            |                       |

| 5           | /CTS0                              | When port register is used as UART0, it is used as a CTS signal (CTS0) of UART0.                                                                                                                                       | R/W        | 1                     |

|             | /SPIDO                             | In a Master mode or a Slave mode, this port register is used for outputting SPI data.                                                                                                                                  |            |                       |

|             | /QUADYB                            | When port register is used as QUAD function, it is used as the input signal of YB value.                                                                                                                               |            |                       |

|             | P3.4                               | This port register is used as a general purpose I/O port.                                                                                                                                                              |            |                       |

| 4           | / <b>T</b> 0                       | When Timer0 is operated as a COUNTER mode, it is operated as a counter input signal (T0) of Timer0.                                                                                                                    | R/W        | 1                     |

|             | /RTS0                              | When port register is used as UART0, it is used as a RTS signal (RTS0) of UART0.                                                                                                                                       |            |                       |

| <u>Bit</u> | Name                                                                                | Descriptions                                                                                                                                  | <u>R/W</u> | Reset<br>Value |

|------------|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------|----------------|

|            | /SPIDI                                                                              | In a Master mode or a Slave mode, this port register is used for receiving SPI data.                                                          |            |                |

|            | /QUADYA                                                                             | When port register is used as QUAD function, it is used as the input signal of YA value.                                                      |            |                |

|            | P3.3                                                                                | This port register is used as a general purpose I/O port.                                                                                     |            |                |

| 3          | /INT1                                                                               | When port register is used as an input signal, it can receive an external interrupt (INT1).                                                   | R/W        | 1              |

|            | P3.2                                                                                | This port register is used as a general purpose I/O port.                                                                                     |            |                |

| 2          | /INT0                                                                               | When port register is used as an input signal, it can receive an external interrupt (INT0).                                                   | R/W        | 1              |

|            | P3.1                                                                                | This port register is used as a general purpose I/O port.                                                                                     |            |                |

| 1          | /TXD0                                                                               | When port register is used as UART0, it is used as a UART0 data output (TXD0).                                                                | R/W        | 1              |

|            | /QUADXB                                                                             | When port register is used as QUAD function, it is used as the input signal of XB value.                                                      |            |                |

|            | P3.0                                                                                | This port register is used as a general purpose I/O port.                                                                                     |            |                |

| 0          | /RXD0 When port register is used as UART0, it is used as a UART0 data input (RXD0). |                                                                                                                                               |            | 1              |

|            | /QUADXA                                                                             | When port register is used as QUAD function, it is used as the input signal of XA value.                                                      |            |                |

|            |                                                                                     | n be used as other functions besides general purpose I/O.                                                                                     |            |                |

|            | P1.7                                                                                | This port register is used as a general purpose I/O port.                                                                                     |            |                |

| 7          | /P0AND                                                                              | When P0AndSel value in P0SEL register is set to '1', P1.7 outputs the result of bit-wise AND operation of (P0 OR P0MSK).                      | R/W        | 1              |

|            | /TRSW                                                                               | It can be used as TRSW (RF TX/RX Indication signal) signal by setting the PHY register.                                                       |            |                |

|            | P1.6                                                                                | This port register is used as a general purpose I/O port.                                                                                     |            |                |

| 6          | /TRSWB                                                                              | It can be used as TRSWB (TRSW Inversion) signal by setting the PHY register.                                                                  | R/W        | 1              |

| 5          | P1.5                                                                                | This port register is used as a general purpose I/O port.                                                                                     | R/W        | 1              |

|            | P1.4                                                                                | This port register is used as a general purpose I/O port.                                                                                     |            |                |

| 4          | /QUADZB                                                                             | When this port register is used as QUAD function, it is used as the input signal of ZB value.                                                 | R/W        | 1              |

|            | /RTXTALI                                                                            | This port register is used for connecting to the external crystal (32.768KHz), which is used in the Sleep Timer, by setting the PHY register. |            |                |

|            | P1.3                                                                                | This port register is used as a general purpose I/O port.                                                                                     |            |                |

| 3          | /QUADZA                                                                             | When this port register is used as QUAD function, it is used as the input signal of ZA value.                                                 | R/W        | 1              |

| <u>Bit</u>             | <u>Name</u>                       | Descriptions                                                                                                                                  | <u>R/W</u> | <u>Reset</u><br>Value |

|------------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------------------|

|                        | /RTXTALO                          | This port register is used for connecting to the external crystal (32.768KHz), which is used in the Sleep Timer, by setting the PHY register. |            |                       |

|                        | /RTCLKO                           | This port register is used to output the internal RCOSC by setting the PHY register.                                                          |            |                       |

| 2                      | P1.2                              | This port register is used as a general purpose I/O port.                                                                                     | R/W        | 1                     |

|                        | P1.1                              | This port register is used as a general purpose I/O port.                                                                                     |            |                       |

| 1                      | /TXD1                             | When this port register is used as UART1, it is used as UART1 data output (TXD1).                                                             | R/W        | 1                     |

|                        | P1.0                              | This port register is used as a general purpose I/O port.                                                                                     |            |                       |

| 0                      | /RXD1                             | When this port register is used as UART1, it is used as UART1 data input (RXD1).                                                              | R/W        | 1                     |

|                        | ) <b>x80)</b><br>port register ca | n be used as other functions besides general purpose I/O.                                                                                     | ,          |                       |

|                        | P0.7                              | This port register is used as a general purpose I/O port.                                                                                     |            |                       |

| 7                      | /I2STXMCL<br>K                    | When this port register is used as I2S, it is operated as TX<br>Master clock of I2S interface.                                                | R/W        | 1                     |

|                        | P0.6                              | This port register is used as a general purpose I/O port.                                                                                     |            |                       |

| 6                      | /I2STXBCL<br>K                    | When this port register is used as I2S, it is operated as TX Bit clock of I2S interface.                                                      | R/W        | 1                     |

|                        | P0.5                              | This port register is used as a general purpose I/O port.                                                                                     |            |                       |

| 5                      | /I2STXLRC<br>K                    | When this port register is used as I2S, it is operated as TX LR clock of I2S interface.                                                       | R/W        | 1                     |

|                        | P0.4                              | This port register is used as a general purpose I/O port.                                                                                     |            |                       |

| 4                      | /I2STXDO                          | When this port register is used as I2S, it is operated as TX data output of I2S interface.                                                    | R/W        | 1                     |

|                        | P0.3                              | This port register is used as a general purpose I/O port.                                                                                     |            |                       |

| 3                      | /I2SRXMCL<br>K                    | When this port register is used as I2S, it is operated as RX Master clock of I2S interface.                                                   | R/W        | 1                     |

|                        | P0.2                              | This port register is used as a general purpose I/O port.                                                                                     |            |                       |

| 2                      | /I2SRXBCL<br>K                    | When this port register is used as I2S, it is operated as RX Bit clock of I2S interface.                                                      | R/W        | 1                     |

| •                      | P0.1                              | This port register is used as a general purpose I/O port.                                                                                     | DAA        | 4                     |

| 1                      | /I2SRXLRC<br>K                    | When this port register is used as I2S, it is operated as the RX LR clock of the I2S interface.                                               | R/W        | 1                     |

|                        | P0.0                              | This port register is used as a general purpose I/O port.                                                                                     |            |                       |

| 0                      | /I2SRXDI                          | When this port register is used as I2S, it is operated as the RX data input of the I2S interface.                                             | R/W        | 1                     |

| P0OI<br>outpu<br>of po | EN, P10EN and                     |                                                                                                                                               |            | e output              |

| 7                      |                                   | Reserved                                                                                                                                      |            | 0                     |

| BitNameDescriptionsB/W7:0P30ENIt controls the TX buffer function for each pin in Port3. When<br>each bit field is set to '0', the TX buffer of the corresponding pin<br>outputs the value.R/W6:0P10ENIt controls the TX buffer function for each pin in Port1. When<br>each bit field is set to '0', the TX buffer of the corresponding pin<br>outputs the value. P1.7 only acts as output.R/W7:0P00ENIt controls the TX buffer function for each pin in Port0. When<br>each bit field is set to '0', the TX buffer of the corresponding pin<br>outputs the value. P1.7 only acts as output.R/W7:0P00ENIt controls the TX buffer function for each pin in Port0. When<br>each bit field is set to '0', the TX buffer of the corresponding pin<br>outputs the value.R/W7:0P0REN/P1REN/P3REN (0xB9, 0xBA, 0xBC)<br>POREN, P1REN, P3REN (0xB9, 0xBA, 0xBC)P0REN, P1REN, P3REN (0xB9, 0xBA, 0xBC)<br>It controls the Pull-up of port 0, 1 and 3. When each bit area is cleared to '0', t<br>up of the corresponding port is enabled.It controls the Pull-up function for each pin in Port3. When each<br>bit field is set to '0', the Pull-up function of the corresponding pin<br>is operated.R/W6:0P1RENIt controls the Pull-up function for each pin in Port1. When each<br>bit field is set to '0', the Pull-up function of the corresponding pin<br>is operated.R/W6:0P1RENIt controls the Pull-up function for each pin in Port1. When each<br>bit field is set to '0', the Pull-up function of the corresponding pin<br>is operated.R/W6:0P1RENIt controls the Pull-up function for each pin in Port1. When each<br>bit field is set to '0', the Pull-up function of the corresponding | Value<br>0x00<br>0x00<br>0x00<br>the Pull-<br>1<br>0xFF |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| 7:0P30ENeach bit field is set to '0', the TX buffer of the corresponding pin<br>outputs the value.R/W6:0P10ENIt controls the TX buffer function for each pin in Port1. When<br>each bit field is set to '0', the TX buffer of the corresponding pin<br>outputs the value. P1.7 only acts as output.R/W7:0P00ENIt controls the TX buffer function for each pin in Port0. When<br>each bit field is set to '0', the TX buffer of the corresponding pin<br>outputs the value. P1.7 only acts as output.R/W7:0P00ENIt controls the TX buffer function for each pin in Port0. When<br>each bit field is set to '0', the TX buffer of the corresponding pin<br>outputs the value.R/W7:0P0REN/P1REN/P3REN (0xB9, 0xBA, 0xBC)<br>P0REN, P1REN, P3REN enable Pull-up of port 0, 1 and 3. When each bit area is cleared to '0', t<br>up of the corresponding port is enabled.It controls the Pull-up function for each pin in Port3. When each<br>bit field is set to '0', the Pull-up function of the corresponding pin<br>is operated.R/W6:0P1RENIt controls the Pull-up function for each pin in Port1. When each<br>bit field is set to '0', the Pull-up function of the corresponding pin<br>is operated.R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0x00<br>0x00<br>the Pull-                               |

| outputs the value.       outputs the value.         6:0       P10EN       It controls the TX buffer function for each pin in Port1. When each bit field is set to '0', the TX buffer of the corresponding pin outputs the value. P1.7 only acts as output.       R/W         7:0       P00EN       It controls the TX buffer function for each pin in Port0. When each bit field is set to '0', the TX buffer of the corresponding pin outputs the value.       R/W         900EN       It controls the TX buffer function for each pin in Port0. When each bit field is set to '0', the TX buffer of the corresponding pin outputs the value.       R/W         90REN/P1REN/P3REN (0xB9, 0xBA, 0xBC)       POREN, P1REN, P3REN enable Pull-up of port 0, 1 and 3. When each bit area is cleared to '0', t up of the corresponding port is enabled.       Reserved         7       Reserved       It controls the Pull-up function for each pin in Port3. When each bit field is set to '0', the Pull-up function of the corresponding pin is operated.       R/W         6:0       P1REN       It controls the Pull-up function for each pin in Port1. When each bit field is set to '0', the Pull-up function of the corresponding pin is operated.       R/W         6:0       P1REN       It controls the Pull-up function for each pin in Port1. When each bit field is set to '0', the Pull-up function of the corresponding pin is operated.       R/W                                                                                                                                                                                                                             | 0x00<br>0x00<br>the Pull-                               |

| 6:0       P10EN       each bit field is set to '0', the TX buffer of the corresponding pin<br>outputs the value. P1.7 only acts as output.       R/W         7:0       P00EN       It controls the TX buffer function for each pin in Port0. When<br>each bit field is set to '0', the TX buffer of the corresponding pin<br>outputs the value.       R/W         P0REN/P1REN/P3REN (0xB9, 0xBA, 0xBC)       P0REN, P1REN, P3REN enable Pull-up of port 0, 1 and 3. When each bit area is cleared to '0', t<br>up of the corresponding port is enabled.       Reserved         7       Reserved       It controls the Pull-up function for each pin in Port3. When each<br>bit field is set to '0', the Pull-up function of the corresponding pin<br>is operated.       R/W         6:0       P1REN       It controls the Pull-up function for each pin in Port1. When each<br>bit field is set to '0', the Pull-up function of the corresponding pin<br>is operated.       R/W         6:0       P1REN       It controls the Pull-up function for each pin in Port1. When each<br>bit field is set to '0', the Pull-up function of the corresponding pin<br>is operated.       R/W         6:0       P1REN       It controls the Pull-up function for each pin in Port1. When each<br>bit field is set to '0', the Pull-up function of the corresponding pin<br>is operated.       R/W                                                                                                                                                                                                                                                                                                   | 0x00<br>the Pull-<br>1                                  |

| outputs the value. P1.7 only acts as output.         7:0       POOEN         It controls the TX buffer function for each pin in Port0. When<br>each bit field is set to '0', the TX buffer of the corresponding pin<br>outputs the value.         POREN/P1REN/P3REN (0xB9, 0xBA, 0xBC)         POREN, P1REN, P3REN enable Pull-up of port 0, 1 and 3. When each bit area is cleared to '0', t<br>up of the corresponding port is enabled.         7       Reserved         7:0       P3REN         It controls the Pull-up function for each pin in Port3. When each<br>bit field is set to '0', the Pull-up function of the corresponding pin<br>is operated.         6:0       P1REN         6:0       P1REN         K       *P1.7 doesn't have a control field because it is operated as an<br>output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0x00<br>the Pull-<br>1                                  |

| 7:0POOENIt controls the TX buffer function for each pin in Port0. When<br>each bit field is set to '0', the TX buffer of the corresponding pin<br>outputs the value.R/WPOREN/P1REN/P3REN (0xB9, 0xBA, 0xBC)<br>P0REN, P1REN, P3REN enable Pull-up of port 0, 1 and 3. When each bit area is cleared to '0', t<br>up of the corresponding port is enabled.Reserved7ReservedIt controls the Pull-up function for each pin in Port3. When each<br>bit field is set to '0', the Pull-up function of the corresponding pin<br>is operated.R/W6:0P1RENIt controls the Pull-up function for each pin in Port1. When each<br>bit field is set to '0', the Pull-up function of the corresponding pin<br>is operated.R/W6:0P1RENIt controls the Pull-up function for each pin in Port1. When each<br>bit field is set to '0', the Pull-up function of the corresponding pin<br>is operated.R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | the Pull-                                               |

| 7:0       POOEN       each bit field is set to '0', the TX buffer of the corresponding pin outputs the value.       R/W         POREN/P1REN/P3REN (0xB9, 0xBA, 0xBC)       POREN, P1REN, P3REN enable Pull-up of port 0, 1 and 3. When each bit area is cleared to '0', t up of the corresponding port is enabled.       Reserved       It controls the Pull-up function for each pin in Port3. When each bit field is set to '0', the Pull-up function of the corresponding pin is operated.       R/W         7:0       P3REN       It controls the Pull-up function for each pin in Port3. When each bit field is set to '0', the Pull-up function of the corresponding pin is operated.       R/W         6:0       P1REN       It controls the Pull-up function for each pin in Port1. When each bit field is set to '0', the Pull-up function of the corresponding pin is operated.       R/W         6:0       P1REN       RP1.7 doesn't have a control field because it is operated as an output.       R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | the Pull-                                               |

| outputs the value. <b>POREN/P1REN/P3REN (0xB9, 0xBA, 0xBC)</b> POREN, P1REN, P3REN enable Pull-up of port 0, 1 and 3. When each bit area is cleared to '0', t         up of the corresponding port is enabled.         7       Reserved         7       It controls the Pull-up function for each pin in Port3. When each bit field is set to '0', the Pull-up function of the corresponding pin is operated.         7:0       P3REN         It controls the Pull-up function for each pin in Port3. When each bit field is set to '0', the Pull-up function of the corresponding pin is operated.         6:0       P1REN         is operated.       R/W         *P1.7 doesn't have a control field because it is operated as an output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | the Pull-                                               |

| POREN/P1REN/P3REN (0xB9, 0xBA, 0xBC)         POREN, P1REN, P3REN enable Pull-up of port 0, 1 and 3. When each bit area is cleared to '0', t         up of the corresponding port is enabled.         7       Reserved         1       It controls the Pull-up function for each pin in Port3. When each bit field is set to '0', the Pull-up function of the corresponding pin is operated.         7:0       P3REN         8:0       P1REN         1       It controls the Pull-up function for each pin in Port3. When each bit field is set to '0', the Pull-up function of the corresponding pin is operated.         6:0       P1REN         8:0       P1REN         1       R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1                                                       |

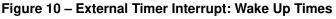

| POREN, P1REN, P3REN enable Pull-up of port 0, 1 and 3. When each bit area is cleared to '0', t         up of the corresponding port is enabled.         7       Reserved         7:0       P3REN         It controls the Pull-up function for each pin in Port3. When each bit field is set to '0', the Pull-up function of the corresponding pin is operated.         6:0       P1REN         is operated.       It controls the Pull-up function for each pin in Port1. When each bit field is set to '0', the Pull-up function of the corresponding pin is operated.         6:0       P1REN         8:0       P1REN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1                                                       |