Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## **Contents**

| 5  |

|----|

| 6  |

| 6  |

| 7  |

| 8  |

| 13 |

| 13 |

| 14 |

| 14 |

| 18 |

| 20 |

| 22 |

| 22 |

| 23 |

| 23 |

| 23 |

| 25 |

| 27 |

| 27 |

| 29 |

| 34 |

| 44 |

| 51 |

| 51 |

| 53 |

| 53 |

| 53 |

| 54 |

| 54 |

| 54 |

| 54 |

| 54 |

| 55 |

| 56 |

|    |

| 3.6.4. PGB Layout considerations                        | 58 |

|---------------------------------------------------------|----|

| 4 Application Information                               | 60 |

| 5 Pin Configuration, Latch-Up and ESD Protection        | 65 |

| 5.1. Pin Configuration and Latch-up Conditions          | 65 |

| 5.2. ESD-Protection                                     |    |

| 6 Package                                               | 67 |

| 6.1. Package Details QFN24 4x4mm                        | 67 |

| 6.1.1. Pin Hardware Configurations                      | 67 |

| 6.1.2. Pin Diagram                                      | 67 |

| 6.1.3. Optimal PCB Layout                               | 68 |

| 6.1.4. Package Outline                                  | 69 |

| 6.1.5. Device Marking                                   | 70 |

| 6.2. Package Details WL-CSP                             | 71 |

| 6.2.1. Pin Hardware Configurations                      | 71 |

| 6.2.2. Pin Diagram                                      |    |

| 6.2.3. Optimal PCB Layout                               | 72 |

| 6.2.4. Package Outline                                  | 73 |

| 6.2.5. Device Marking                                   | 74 |

| 7 Ordering Information                                  | 75 |

| 8 Related Documents                                     |    |

| 9 Glossary                                              | 77 |

| 9.1. Terms and Abbreviations                            | 77 |

| 9.2. Symbols used in this Datasheet                     |    |

| 10 Document Revision History                            |    |

| Appendix A ZIOL2xxx Diagnostic Techniques               |    |

| A.1. General Remarks                                    |    |

| A.2. Overload Counter Behavior and Peak Register Access |    |

| A.3. Overload Counter and Lock Reset Methods            |    |

| Appendix B ZIOL2xxx Configuration Techniques            |    |

| Appendix C ZIOL2xxx Line Fail Detector                  | 90 |

# **List of Figures**

| Figure 2.1  | Max. Total Power Dissipation                                                     | 6  |

|-------------|----------------------------------------------------------------------------------|----|

| Figure 2.2  | Efficiency of the DC/DC converter for VOUT=5V, C=10μF and L=10μH                 | 12 |

| Figure 3.1  | Functional Block Diagram of the ZIOL2xxx                                         |    |

| Figure 3.2  | ZIOL24xx Transceiver Data Path in Principle                                      | 14 |

| Figure 3.3  | ZIOL22xx Transceiver Data Path in Principle                                      | 15 |

| Figure 3.4  | ZIOL21xx Transceiver Data Path in Principle                                      | 16 |

| Figure 3.5  | ZIOL24xx in Device and Master Mode Application                                   | 19 |

| Figure 3.6  | Typical IO-Link Device Configuration with HS driver only                         | 22 |

| Figure 3.7  | Wake-Up Signal Recognition                                                       | 24 |

| Figure 3.8  | The Basic Scheme of the IC Self Protection                                       | 26 |

| Figure 3.9  | Memory Unit                                                                      | 28 |

| Figure 3.10 | General timing of a byte transfer                                                | 30 |

| Figure 3.11 | Structure of SPI accesses                                                        | 31 |

| Figure 3.12 | SPI Command Structure                                                            | 32 |

| Figure 3.13 | SPI Timing                                                                       | 34 |

| Figure 3.14 | Interrupt (INT_L pin) and Wake-up (WURQ_L pin) Signaling                         | 45 |

| Figure 3.15 | COM Channel Lock Control                                                         | 46 |

|             | AUX Channel Lock Control                                                         |    |

| Figure 3.17 | Over-Temperature Lock Control                                                    | 48 |

| Figure 3.18 | Internal IC Sensors and related Overload and Over-Temperature Detection Circuits | 50 |

| Figure 3.19 | Low Voltage Supply Concept                                                       | 52 |

| Figure 3.20 | PFD Working Principle                                                            | 53 |

| Figure 3.21 | DC/DC Converter in Principle                                                     | 55 |

| Figure 3.22 | DC/DC Converter Output Voltage as Function of R1 (R2 = 10kOhms)                  | 57 |

| Figure 3.23 | High frequency critical loops of DC/DC converter for PCB layout                  | 58 |

| Figure 3.24 | PCB layout of Evaluation board as an example                                     | 59 |

| Figure 4.1  | Simplified Application Circuit with the ZIOL2xxx in Device Mode                  | 60 |

| Figure 4.2  | Simplified Application Circuit with the ZIOL2xxx in Master Mode                  | 61 |

| Figure 4.3  | Power Line Fail Detection                                                        | 62 |

| Figure 4.4  | PCB Layout Recommendations                                                       | 63 |

| Figure 6.1  | Pin Diagram of the ZIOL2xxx                                                      |    |

| Figure 6.2  | Package Dimensions                                                               | 69 |

| Figure 6.3  | Top Marking of the ZIOL2xxx                                                      | 70 |

| Figure 6.4  | Package Dimensions                                                               | 72 |

| Figure 6.5  | Package Dimensions WL-CSP                                                        | 73 |

| Figure 6.6  | Top Marking of the ZIOL2xxx CSP                                                  |    |

| Figure 9.1  | Register Representation in Principle (Example)                                   | 78 |

| Figure 10.1 | Peak Register Access Scenarios                                                   |    |

| Figure 10.2 | Overload Counter Behavior in permanent Over-Current Situations                   | 83 |

| Figure 10.3 | Overload Counter Behavior in permanent Over-Temperature Situations     | 84 |

|-------------|------------------------------------------------------------------------|----|

| Figure 10.4 | Overload Counter Behavior in typical Over-Temperature Situations       | 85 |

| Figure 10.5 | Partial Reset of Overload Counter or the entire Lock circuit           | 86 |

| Figure 10.6 | Configuration Checker Report of the ZIOL2xxx Application Kit (Example) | 88 |

| List of     | Tables                                                                 |    |

| Table 1.1   | ZIOL2xxx Product Matrix and Product Naming Convention                  | 5  |

| Table 2.1   | Absolute Maximum Ratings                                               | 6  |

| Table 2.2   | Operating Conditions                                                   | 7  |

| Table 2.3   | Electrical Characteristics                                             | 8  |

| Table 3.1   | Master-Device-Mode Function Table                                      | 17 |

| Table 3.2   | Driver configurations                                                  | 20 |

| Table 3.3   | Receiver configurations                                                | 21 |

| Table 3.4   | Sink Mode Configuration in Detail                                      | 22 |

| Table 3.5   | Example for building the SHIFT Byte                                    | 32 |

| Table 3.6   | Valid Address and Length Combinations                                  | 32 |

| Table 3.7   | Register Table                                                         | 35 |

| Table 3.8   | Temperature Sensor Levels                                              | 51 |

| Table 3.9   | Examples for the resistors R1 and R2 using E96 resistor series         | 56 |

| Table 4.1   | Recommended External Components                                        | 64 |

| Table 5.1   | Pin Configuration and Latch-Up Conditions                              | 65 |

| Table 6.1   | Availability of Pin Interconnections                                   | 67 |

| Table 6.2   | Package Dimensions in mm                                               | 69 |

| Table 6.3   | Availability of Pin Interconnections                                   | 71 |

| Table 6.4   | Bump Pin Configuration                                                 | 72 |

| Table 6.5   | Package Dimensions in mm                                               | 73 |

| Table 10.1  | Abnormal Power Supply Situations                                       | 90 |

|             |                                                                        |    |

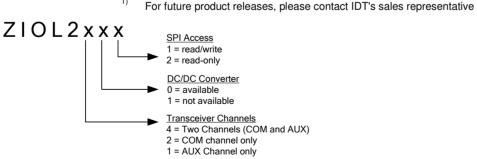

## 1 The ZIOL2xxx IC Family Overview

IDT provides a universal and IO-Link compatible cable driver IC by issuing the ZIOL2401 integrated circuit. The ZIOL2401 is highly configurable and suitable for a wide range of applications in process and factory automation. In order to fulfill the requirements of specific applications stripped down versions of the IC were required. The ZIOL2xxx IC family is derived from the ZIOL2401 by modification (elimination or disabling) of certain functional building blocks. In this combination the following building blocks or functions are affected:

- The transceiver channels COM and AUX

- The availability of the integrated DC/DC converter

- The activation of a read-only data access via the SPI interface

This datasheet describes the entire IC family ZIOL2xxx. Respective notes or footnotes describe the availability the above mentioned building blocks or functionality with respect to certain IC family members. Table 1.1 shows an overview concerning the ZIOL2xxx IC family and the used naming convention.

Table 1.1 ZIOL2xxx Product Matrix and Product Naming Convention

| ZIOL2xxx<br>Member | Transceiver<br>Channel | DC/DC<br>Converter | SPI<br>Access | Remarks              |

|--------------------|------------------------|--------------------|---------------|----------------------|

| ZIOL2401           | COM + AUX              | yes                | r/w           | Base type - released |

| ZIOL2201           | COM                    | yes                | r/w           | released             |

| ZIOL2101           | AUX                    | yes                | r/w           | 1)                   |

| ZIOL2411           | COM + AUX              | no                 | r/w           | released             |

| ZIOL2211           | COM                    | no                 | r/w           | released             |

| ZIOL2111           | AUX                    | no                 | r/w           | 1)                   |

| ZIOL2402           | COM + AUX              | yes                | r             | 1)                   |

| ZIOL2202           | COM                    | yes                | r             | 1)                   |

| ZIOL2102           | AUX                    | yes                | r             | 1)                   |

| ZIOL2412           | COM + AUX              | no                 | r             | 1)                   |

| ZIOL2212           | COM                    | no                 | r             | 1)                   |

| ZIOL2112           | AUX                    | no                 | r             | 1)                   |

|                    | 1)                     |                    |               | IDTI I IDTI-         |

## 2 Electrical Characteristics

## 2.1. Absolute Maximum Ratings

Parameters apply in operation temperature range and without time limitations.

Table 2.1 Absolute Maximum Ratings

| Symbol             | Parameter                       | Min  | Max               | Unit | Conditions                              |

|--------------------|---------------------------------|------|-------------------|------|-----------------------------------------|

| V <sub>DD_HV</sub> | Supply voltage                  | -0.3 | 40                | V    |                                         |

| V <sub>HV</sub>    | Voltage at HV pins              | -0.3 | $V_{DD\_HV}+0.3$  | V    |                                         |

| V <sub>LV</sub>    | Voltage at LV pins              | -0.3 | $V_{DD\_LV}$ +0.3 | ٧    | 2)                                      |

| V <sub>imp</sub>   | Impulse voltage withstand       | 60   |                   | ٧    | according to IEC 60947-5-2              |

| V <sub>ESD</sub>   | Abs. ESD test voltage           |      | 2k                | V    | according to HBM                        |

| Ts                 | Junction temperature            |      | 125               | °C   | 1)                                      |

| Ta                 | Storage temperature             | -50  | 150               | °C   |                                         |

| P <sub>tot</sub>   | Average total power dissipation |      | 2.6               | W    | integration period < 10ms <sup>3)</sup> |

<sup>1)</sup> Average die-temperature.

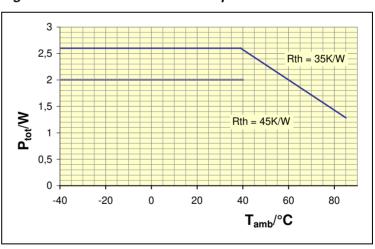

Figure 2.1 Max. Total Power Dissipation

Exceptions are the digital input pins (μC interface) which tolerate 5V logic signals (refer to Table 5.1).

The allowed total power dissipation depends on the in the PCB design achieved thermal resistance R<sub>th</sub> (package/ambient) and the ambient operation temperature as shown in Figure 2.1. In order to obtain optimal heat distribution (R<sub>th</sub> < 35K/W) certain PCB layout rules shall be applied. Those rules are described in the application note for the used QFN package (refer to chapter 8, [4]).

#### 2.2. **Operating Conditions**

Table 2.2 **Operating Conditions**

| Symbol               | Parameter                                | Min  | Typ <sup>1)</sup> | Max | Unit | Conditions                                                                                                                       |

|----------------------|------------------------------------------|------|-------------------|-----|------|----------------------------------------------------------------------------------------------------------------------------------|

| $V_{DD\_HV}$         | Supply voltage                           | 8.0  | 24                | 36  | V    |                                                                                                                                  |

| V <sub>in</sub>      | Linear regulator input voltage           | 4.75 |                   | 36  | >    | LR_IN can be connected to $V_{DD\_HV}$ or DC/DC output voltage.                                                                  |

| $V_{DD\_LV}$         | Linear regulator output voltage          | 3.0  | 3.3               | 3.6 | V    | Voltage LR_OUT → GND pin                                                                                                         |

| l <sub>out</sub>     | Linear regulator output current          |      |                   | 10  | mA   | LR_OUT provides supply current for external applications. <sup>2)</sup>                                                          |

| t <sub>startup</sub> | Startup timing @ V <sub>DD_HV</sub> = 8V |      |                   | 5   | ms   | Time for system start up including loading of configuration registers from EEPROM                                                |

| T <sub>amb</sub>     | Operating ambient temperature            | -40  |                   | +85 | °C   |                                                                                                                                  |

| f <sub>osc</sub>     | Internal oscillator frequency            | 4.5  |                   | 5.5 | MHz  | Internal clock is not available externally. All digital circuit timing parameters of the IC are derived from the internal clock. |

The mentioned typical values of IC properties are provided for information only.

While start-up (until the voltage at LR\_OUT has reached 1V) the output current may be limited to 5mA.

#### 2.3. **Electrical Parameters**

All parameter values are valid under operating conditions specified in chapter 2.2 if no other conditions are mentioned.

Table 2.3 **Electrical Characteristics**

| Symbol                     | Parameter                                                             | Min | Typ <sup>1)</sup> | Max                 | Unit | Conditions                                                         |

|----------------------------|-----------------------------------------------------------------------|-----|-------------------|---------------------|------|--------------------------------------------------------------------|

| Transmitter Ou             | tput Stages (COM¹/AUX²)                                               |     |                   |                     |      |                                                                    |

| I <sub>DAL_0</sub>         | Alarm level threshold                                                 | 50  |                   | I <sub>Dout_0</sub> | mA   | Dual mode                                                          |

| I <sub>DAL_1</sub>         | corresponding to configurable output current limitation <sup>2)</sup> | 100 |                   | I <sub>Dout_1</sub> | mA   | The active setting is defined in                                   |

| I <sub>DAL_2</sub>         | Dual Driver Mode                                                      | 200 |                   | I <sub>Dout_2</sub> | mA   | the configuration registers                                        |

| I <sub>DAL_3</sub>         | <u> </u>                                                              | 250 |                   | I <sub>Dout_3</sub> | mA   |                                                                    |

| I <sub>MAL_0</sub>         | Alarm level threshold                                                 | 100 |                   | I <sub>Mout_0</sub> | mA   | Tandem mode                                                        |

| I <sub>MAL_1</sub>         | corresponding to configurable output current limitation <sup>2)</sup> | 200 |                   | I <sub>Mout_1</sub> | mA   | The active setting is defined in                                   |

| I <sub>MAL_2</sub>         | Tandem Driver Mode                                                    | 400 |                   | I <sub>Mout_2</sub> | mA   | the configuration registers.                                       |

| I <sub>MAL_3</sub>         |                                                                       | 500 |                   | I <sub>Mout_3</sub> | mA   |                                                                    |

| I <sub>Dout_0</sub>        | Configurable output current limit <sup>2)</sup>                       | 56  |                   | 95                  | mA   | Dual mode                                                          |

| I <sub>Dout_1</sub>        | <u>Dual Driver Mode</u>                                               | 112 |                   | 180                 | mA   | The active setting is defined in                                   |

| I <sub>Dout_2</sub>        |                                                                       | 224 |                   | 330                 | mA   | the configuration registers.                                       |

| I <sub>Dout_3</sub>        |                                                                       | 280 |                   | 410                 | mA   |                                                                    |

| I <sub>Mout_0</sub>        | Configurable output current limit <sup>2)</sup>                       | 112 |                   | 180                 | mA   | Tandem mode                                                        |

| I <sub>Mout_1</sub>        | Tandem Driver Mode                                                    | 224 |                   | 360                 | mA   | The active setting is defined in                                   |

| I <sub>Mout_2</sub>        |                                                                       | 448 |                   | 660                 | mA   | the configuration registers.                                       |

| I <sub>Mout_3</sub>        |                                                                       | 560 |                   | 820                 | mA   |                                                                    |

| SR <sub>38</sub>           | 3)                                                                    | 6   | 10                | 14 <sup>5)</sup>    | V/µs | referring to IO-Link Spec.: 38,4kBaud (COM2),                      |

| SR <sub>230</sub>          | Slew rate <sup>3)</sup>                                               | 40  | 60                | 80 <sup>5)</sup>    | V/µs | referring to IO-Link Spec.:<br>230.4kBaud (COM3)                   |

| t <sub>TLHdelay</sub> COM3 | Propagation delay L-H edge                                            |     |                   | 250                 | ns   | Time from LV L-H edge till HV edge begins to rise (COM3 baud rate) |

| t <sub>THLdelay</sub> COM3 | Propagation delay H-L edge                                            |     |                   | 250                 | ns   | Time from LV H-L edge till HV edge begins to fall (COM3 baud rate) |

| t <sub>TLHdelay</sub> COM2 | Propagation delay L-H edge                                            |     |                   | 700                 | ns   | Time from LV L-H edge till HV edge begins to rise (COM2 baud rate) |

$<sup>^{\</sup>rm 1}$  The COM transmitter is only available inside the products ZIOL24xx/22xx  $^{\rm 2}$  The AUX transmitter is only available inside the products ZIOL24xx/21xx

| Symbol                    | Parameter                                                   | Min   | Typ <sup>1)</sup> | Max              | Unit                 | Conditions                                                                                               |

|---------------------------|-------------------------------------------------------------|-------|-------------------|------------------|----------------------|----------------------------------------------------------------------------------------------------------|

| t <sub>THLdelayCOM2</sub> | Propagation delay H-L edge                                  |       |                   | 700              | ns                   | Time from LV H-L edge till HV edge begins to fall (COM2 baud rate)                                       |

| Receiver Input            | Channels (COM <sup>1</sup> /AUX <sup>2</sup> )              |       |                   |                  |                      |                                                                                                          |

| V <sub>ih1</sub>          | IO-Link specific threshold, High                            | 10.75 |                   | 12.75            | V                    |                                                                                                          |

| V <sub>il1</sub>          | IO-Link specific threshold, Low                             | 8.75  |                   | 10.75            | V                    |                                                                                                          |

| V <sub>ihyst1</sub>       | IO-Link specific thresholds,<br>Hysteresis                  | 1.5   |                   | 2.5              | V                    |                                                                                                          |

| V <sub>ih2</sub>          | Ratiometric threshold, High                                 | 52    |                   | 57               | %*V <sub>DD_HV</sub> |                                                                                                          |

| V <sub>il2</sub>          | Ratiometric threshold, Low                                  | 43    |                   | 47.7             | %*V <sub>DD_HV</sub> |                                                                                                          |

| V <sub>ihyst2</sub>       | Ratiometric thresholds,<br>Hysteresis                       | 7     |                   | 11.6             | %*V <sub>DD_HV</sub> |                                                                                                          |

| R <sub>in</sub>           | Input resistance                                            | 150   |                   |                  | kOhms                |                                                                                                          |

| C <sub>in</sub>           | Input capacitance                                           |       |                   | 20               | pF                   |                                                                                                          |

| t <sub>Rdelay</sub>       | Propagation delay without filtering                         |       |                   | 80<br>100<br>200 | ns<br>ns<br>ns       | No filter within signal path.<br>Input edge with:<br>>30V/µs (COM3)<br>>5V/µs (COM2)<br>>0.75V/µs (COM1) |

| tFRdelay                  | Propagation delay with analog filtering                     | 750   | 850               | 950              | ns                   | @V <sub>DD_HV</sub> = 24V, Input edge with: >30V/μs (COM3)                                               |

| t <sub>Rpulse</sub>       | Minimal propagated pulse width without filtering            |       | 25                |                  | ns                   |                                                                                                          |

| t <sub>FRpulse</sub>      | Minimal propagated pulse width with analog filtering        |       | 1.1               |                  | μs                   |                                                                                                          |

| t <sub>DIGdelay</sub>     | Additional propagation delay with digital filtering         | 180   |                   | 440              | ns                   |                                                                                                          |

| f <sub>cut</sub>          | Input filter – cut off frequency (-3dB) COM and AUX channel | 100   |                   | 250              | kHz                  | filter characteristic: 1 <sup>st</sup> order                                                             |

| I <sub>sink1</sub>        | Sink strength 1                                             | 2     | 2.5               | 3                | mA                   | Line input voltage >5V                                                                                   |

| I <sub>sink2</sub>        | Sink strength 2                                             | 5     | 6                 | 7                | mA                   | According to IO-Link<br>Specification                                                                    |

| $R_pull$                  | Configurable pull-up/pull-down resistor @ COM_O/AUX_O       | 100k  |                   | 250k             | Ohms                 |                                                                                                          |

$<sup>^1</sup>$  The COM receiver is only available inside the products ZIOL24xx/22xx  $^2$  The AUX receiver is only available inside the products ZIOL24xx/21xx

| Symbol                        | Parameter                                                      | Min             | Typ <sup>1)</sup> | Max  | Unit      | Conditions                                                                |  |

|-------------------------------|----------------------------------------------------------------|-----------------|-------------------|------|-----------|---------------------------------------------------------------------------|--|

| WURQ Detecti                  | on                                                             |                 |                   |      |           |                                                                           |  |

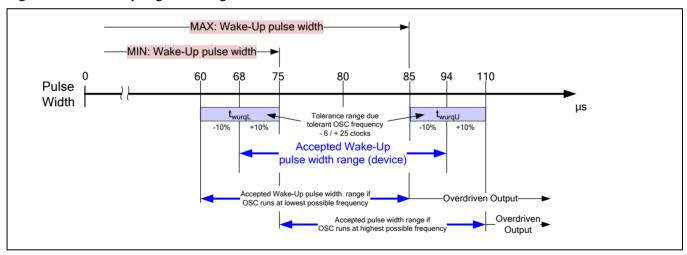

| t <sub>wurqL</sub>            | Lower pulse width limit of signal evaluated as IO-Link wake-up | 60              | 68                | 75   | μs        | Refer to chapter 3.3.4                                                    |  |

| $t_{wurqU}$                   | Upper pulse width limit of signal evaluated as IO-Link wake-up | 85              | 94                | 109  | μs        | Refer to chapter 3.3.4                                                    |  |

| DC/DC conver                  | ter <sup>1</sup>                                               |                 | •                 |      |           |                                                                           |  |

| V <sub>OUT</sub>              | Output voltage Range <sup>6)</sup>                             | 3               |                   | 15   | V         | @ V <sub>DD_HV</sub> > V <sub>out</sub> + 2V<br>(step down function only) |  |

| I <sub>LOAD</sub>             | Output load current                                            | 5 <sup>4)</sup> |                   | 50   | mA        | Current that flows to the application and the R-Divider                   |  |

| I <sub>PK</sub>               | Over current limit for output transistor                       |                 | 240               |      | mA        | Averaged current over complete short at DCDC converter output             |  |

| $f_{osc}$                     | Operating frequency                                            | 2.25            |                   | 2.75 | MHz       |                                                                           |  |

| $V_{ref}$                     | Reference/feedback Voltage                                     |                 | 1.225             |      | V         | at FB pin in steady state                                                 |  |

| $\Delta V_{\text{OUT\_Line}}$ | DC Output Line Regulation                                      |                 | 8                 |      | mV/V      | @V <sub>out</sub> =5V, I <sub>LOAD</sub> = 5mA<br>Filter: C=10µF, L=10µH  |  |

| $\Delta V_{\text{OUT\_Load}}$ | DC Output Load Regulation                                      |                 |                   |      | mV/mA     | Filter: C=10μF, L=10μH                                                    |  |

|                               | @Vout=3.3V                                                     | 0.7             |                   | 1.4  |           | $V_{OUT} = 5V$                                                            |  |

|                               | @Vout=15V                                                      | 3.3             |                   | 6.9  |           |                                                                           |  |

| $V_{ripple}$                  | Ripple of Output Voltage                                       |                 |                   |      | $mV_{PP}$ | Filter: C=10μF, L=10μH                                                    |  |

|                               | @ VDD_HV >= 24V                                                |                 | 65 <sup>7)</sup>  |      |           | $V_{OUT} = 5V$                                                            |  |

|                               | @ VDD_HV < 24V                                                 |                 | 25 <sup>7)</sup>  |      |           |                                                                           |  |

| t <sub>strt</sub>             | Settling time after POR is released                            |                 | 1                 |      | ms        | For C=10μF, L=10μH<br>Higher C may result in higher t <sub>str</sub>      |  |

| t <sub>DLY</sub>              | digital delay for DC_RDY signal                                | 45              | 50                | 55   | ms        | If enabled in configuration                                               |  |

| η                             | Efficiency                                                     | 8)              |                   |      | %         | Filter: C=10μF, L=10μH                                                    |  |

$<sup>^{\</sup>rm 1}$  The DC/DC converter is only available inside the products ZIOL2401/2402/2201/2202/2101/2102

| Symbol                       | Parameter                   |                                                            |      | Typ <sup>1)</sup> | Max  | Unit                 | Conditions                                                                                                                          |  |  |  |  |

|------------------------------|-----------------------------|------------------------------------------------------------|------|-------------------|------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Microcontroller Interface 9) |                             |                                                            |      |                   |      |                      |                                                                                                                                     |  |  |  |  |

| V <sub>LIH</sub>             | Voltage range t             | or input "high"                                            | 2.5  |                   | 5.5  | V                    | $\bigcirc$ $V_{DD\_LV} = 3.6V$ , otherwise $V_{LIH\text{-min}} = 0.7 * V_{DD\_LV}$                                                  |  |  |  |  |

| $V_{LIL}$                    | Voltage range t             | or input "low" level                                       | -0.3 |                   | 0.9  | V                    | $\bigcirc$ V <sub>DD_LV</sub> = 3.0V, otherwise<br>V <sub>LIL-max</sub> = 0.3 * V <sub>DD_LV</sub>                                  |  |  |  |  |

| I <sub>LIH</sub>             | Logic "high" input current  | @ pins without<br>pull-up/pull-down                        | -1   |                   | 1    | μΑ                   | $\textcircled{0} V_{LIH} = V_{DD\_LV}$                                                                                              |  |  |  |  |

| I <sub>LIL</sub>             | Logic "low" input current   | resistors:<br>INT_L, WURQ_L                                | -1   |                   | 1    | μΑ                   | @ V <sub>LIL</sub> = 0V                                                                                                             |  |  |  |  |

| I <sub>LIH_PD</sub>          | Logic "high" input current  | @ pins with pull-<br>down resistors:                       | -300 |                   | -150 | μΑ                   |                                                                                                                                     |  |  |  |  |

| l <sub>LIL_PD</sub>          | Logic "low" input current   | TX_EN/SPI_CLK,<br>TX/MOSI,<br>AUX_EN,<br>AUX_TX,<br>DC_RDY | -1   |                   | 1    | μА                   | $\textcircled{0} \ V_{LIL} = 0V, \ V_{DD\_LV-max} = 3.6V \\ \textcircled{0} \ V_{LIL} = 0V, \ V_{DD\_LV-max} = 3.0V \\ \end{array}$ |  |  |  |  |

| I <sub>LIH_PU</sub>          | Logic "high" input current  | @ pins with pull-<br>up resistors:                         | -1   |                   | 1    | μΑ                   |                                                                                                                                     |  |  |  |  |

| I <sub>LIL_PU</sub>          | Logic "low" input current   | RST_L,<br>SPI_EN_L                                         | -150 |                   | 250  | μΑ                   |                                                                                                                                     |  |  |  |  |

| $V_{LOL}$                    | Logic "high" output voltage | @ output pins:<br>RX/MISO,                                 | 0    |                   | 5    | %*V <sub>DD_LV</sub> | @ I <sub>LIL</sub> = 1mA                                                                                                            |  |  |  |  |

| $V_{LOH}$                    | Logic "high" output voltage | AUX_RX                                                     | 95   |                   | 100  | %*V <sub>DD_LV</sub> | @ I <sub>LIH</sub> = -1mA                                                                                                           |  |  |  |  |

| Internal Curren              | t Consumption               | 10)                                                        |      |                   |      |                      |                                                                                                                                     |  |  |  |  |

| I <sub>VDD</sub>             | Current into VDD            |                                                            |      | 1.7               | 2.5  | mA                   | SPI_EN=3.3V                                                                                                                         |  |  |  |  |

| I <sub>LR_IN</sub>           | Current into LF             | R_IN                                                       |      | 2.2               | 3.4  | mA                   | SPI_EN=3.3V                                                                                                                         |  |  |  |  |

The mentioned typical values of IC properties are provided for information only and shall not be considered as statistical guaranteed mean values. Typical values are not subject for measurement while the electrical test of each IC – they are correct by design.

Absolute edge rise and fall times are proportional to V<sub>DD\_HV</sub>

- 5) Slew-rate measured after settlement time of the output signal

- 6) Configurable with an external voltage divider (refer to chapter 3.5)

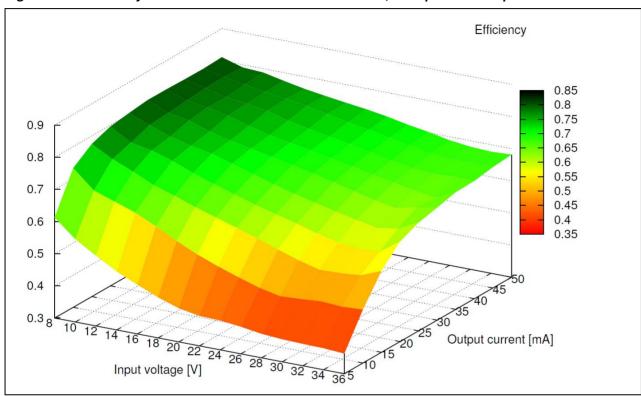

- The efficiency of the DC/DC converter is depending on the external components and the used PCB layout. Moreover, there is an influence from several operational conditions which is illustrated in the diagram of Figure 2.2

- Microcontroller interface pins are: RST\_L, SPI\_EN\_L, INT\_L, WURQ\_L, TX\_EN/SPI\_CLK, TX/MOSI, RX/MISO, AUX\_EN, AUX\_TX, AUX\_RX, DC\_RDY

- Current consumption is measured by applying the maximum supply voltage at the supply pins VDD and LR\_IN (V<sub>VDD\_HV</sub>=36V, V<sub>in</sub>=36V) and using a decoupling cap of 10μF between LR\_OUT and ground. Both VDD and both VSS pins are interconnected, respectively. Pins TX\_EN/SPI\_CLK, AUX\_TX, TX\_EN, AUX\_EN, PFD, COM\_I, AUX\_I are connected to ground.

If the output current exceeds the configured current limit, the IC will raise an overload signal which causes up-counting of the overload counter (if configured) and which definitely limits the output current. However, the current limit will be performed after a certain settling time in order to ensure the configured slope of the output signal.

<sup>&</sup>lt;sup>4)</sup> A minimum of the output current must be provided by the application circuit. Otherwise the DC/DC converter shall be unused by interconnecting the FB pin with the LR\_OUT pin. The required voltage divider (refer to Figure 3.21) may provide this current partly or in full.

The ripple on the output voltage depends significantly on both the external components and the PCB layout. Reference PCB layouts are available from IDT. The layouts used in the application kits are shown in Figure 4.4; detailed layout data of the application kits are available from IDT upon request.

Figure 2.2 Efficiency of the DC/DC<sup>1</sup> converter for VOUT=5V, C=10μF and L=10μH

$<sup>^{\</sup>rm 1}$  The DC/DC converter is only available inside the products ZIOL2401/2402/2201/2202/2101/2102

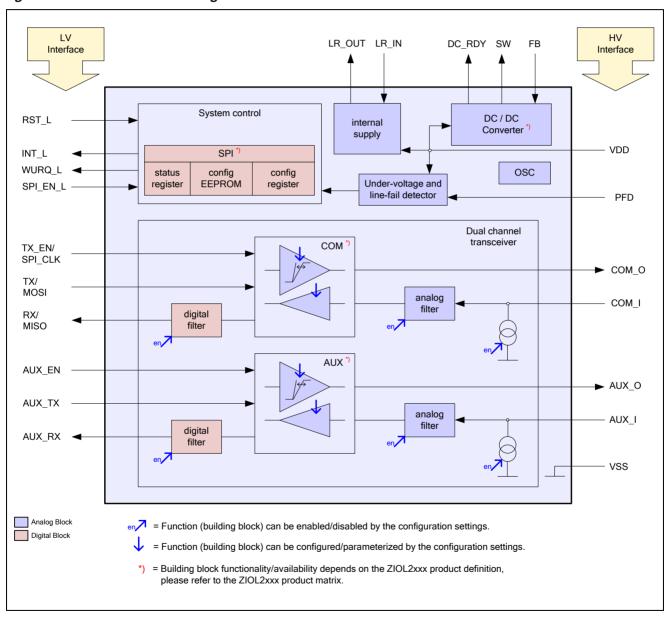

# 3 Detailed Description

### 3.1. Block schematic

Figure 3.1 Functional Block Diagram of the ZIOL2xxx

#### 3.2. Dual Channel Transceiver

#### 3.2.1. IC Data Path Configuration

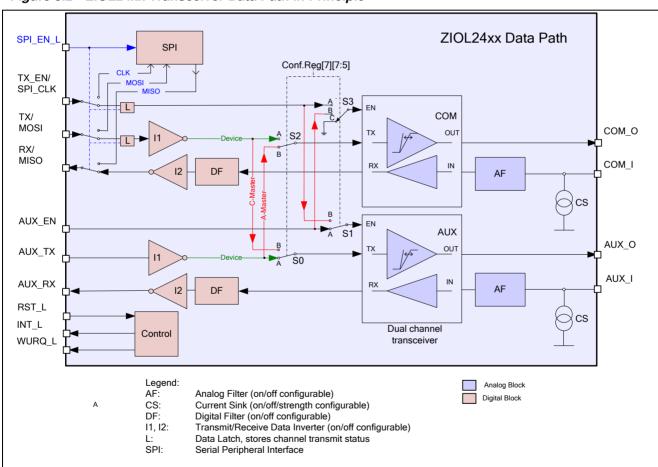

The ZIOL2xxx ICs contains one (ZIOL22xx/21xx) or two (ZIOL24xx) transceiver channels. The channels inside the product versions with two channels can work independently in the "Dual Mode" or coordinated in "Tandem Mode". The data path of the ZIOL24xx Ics is illustrated in Figure 3.2. Both channels, which are designed identically, are widely configurable. Due to configuration and the range of supported supply voltages the Ics can be used in a broad field of applications. Example applications can be level shifter for standard sensor applications or driver for resistive, capacitive or inductive loads.

Figure 3.2 ZIOL24xx Transceiver Data Path in Principle

Maximum driver capability of minimum 500mA can be achieved by combining both drivers. In this case the drivers work in parallel (Tandem Mode).

14

In order to gain optimal EMC behavior the slew rate of the output signals of both drivers can be adjusted. The input threshold levels of the receiver can be set to ratiometric or to IO-Link conform levels, which enables the IC to be used in applications having a wide supply voltage range.

The configuration of the transceiver can be changed during operation. After power-on this configuration is automatically loaded from the on-chip EEPROM.

Driver and receiver are kept totally separated, so full duplex mode in data communication systems is supported. The ability to enable/disable the drivers output also enables applications in half duplex mode, where output and input are connected. Having the I/O-pins separated also enables additional external input filtering.

The COM channel send and receive signals (TX\_EN, TX, RX) are multiplexed with the signals of the SPI functional unit of the IC (SPI\_CLK, MOSI, MISO) as shown in Figure 3.2. The SPI unit is used for IC configuration and diagnostic purposes (refer to chapter 3.3.8). As long the SPI unit is active (SPI\_EN\_L = low), the send status of the COM channel is kept (for information refer to chapter 3.3.8 and Figure 3.10).

ZIOL22xx Data Path SPI EN LE SPI Conf.Reg[7][7:5] CLK TX EN/ MISO SPI\_CLK L COM TX TX OUT MOS S2 占сом\_о В RX/ RX IN MISO 12 DF <u></u>сом г ΑF CS AUX EN S1 B 占 AUX O AUX TX Š0 AUX I DF 12 AUX RX RST L Single channel Control INT L transceiver WURQ L Legend: Analog Block Analog Filter (on/off configurable) AF. Digital Block CS: Current Sink (on/off/strength configurable) DF: Digital Filter (on/off configurable) Transmit/Receive Data Inverter (on/off configurable) 11, 12: Data Latch, stores channel transmit status SPI: Serial Peripheral Interface

Figure 3.3 ZIOL22xx Transceiver Data Path in Principle

April 26, 2016

The (stripped down) IC versions ZIOL22xx/21xx contain only one channel. Figure 3.3 and Figure 3.4 show the data path of the ZIOL22xx versions and ZIOL21xx versions, respectively. The following chapters regarding details of the transmitter and receiver apply to IC versions with two channels (ZIOL24xx). The in the following described functionality applies to IC versions with one channel (ZIOL22xx/21xx) correspondingly. With the implicit understanding that one channel IC versions cannot perform tandem (master) mode operations or coordinated transceiver operations no explicit statement in the following chapters will reflect this.

ZIOL21xx Data Path SPI EN LC SPI Conf.Reg[7][7:5] TX EN/ SPI CLK n c TX/ MOSI S2 <u></u>Сом о n.c nс B RX/ MISO Дсом\_г ΕN AUX EN AUX S1 В OUT ካaux o AUX TX S0 AUX I IN RX ΑF AUX\_RX RST L CS Single channel INT L Control WURQ L Legend: Analog Block AF: Analog Filter (on/off configurable) Digital Block CS: Current Sink (on/off/strength configurable) DF: Digital Filter (on/off configurable) 11, 12: Transmit/Receive Data Inverter (on/off configurable) Data Latch, stores channel transmit status SPI: Serial Peripheral Interface

Figure 3.4 ZIOL21xx Transceiver Data Path in Principle

The master mode configuration flags MASTER\_MODE, EN\_FOLLOW\_PRIM\_CH and PRIMARY\_MASTER\_CH located in the MASTER\_SENS\_CTRL configuration register (refer to Table 3.7) control the switches S0, S1, S2 and S3 (Figure 3.2, Figure 3.3 and Figure 3.4) thus they control the actually used data path. In principle, the ZIOL2xxx IC family supports five data path types which are mentioned in Table 3.1. In case the MASTER\_MODE flag is cleared (=0), the IC operates in device mode. For more information about the operation in device/master mode, please refer to chapter 3.2.2.1.

Table 3.1 Master-Device-Mode Function Table

| Data Path Configuration |                                                                              | MASTER_SENS<br>_CTRL[7:5]                                               | Data Path<br>Switch<br>Position |        |        |        | Receiver available       | RX/<br>MISO          | REMARKS                                                       |

|-------------------------|------------------------------------------------------------------------------|-------------------------------------------------------------------------|---------------------------------|--------|--------|--------|--------------------------|----------------------|---------------------------------------------------------------|

| T<br>y<br>p<br>e        | Global IC Function                                                           | [7] = MASTER_MODE<br>[6] = EN_FOLLOW_PRIM_CH<br>[5] = PRIMARY_MASTER_CH | S<br>0                          | S<br>1 | S<br>2 | S<br>3 | 1)                       | State<br>control     | REIVIANNS                                                     |

| 0                       | Device Mode                                                                  | 0 X X                                                                   | Α                               | Α      | Α      | Α      | COM <sup>2)</sup><br>AUX | push/ pull           | Equivalent to<br>IC Rev A<br>Device Mode                      |

| 1                       | Master Mode, COM = prim channel, AUX enable not following prim-ch            | 100                                                                     | В                               | Α      | Α      | Α      | COM <sup>2)</sup>        | push/ pull           | Equivalent to<br>IC Rev A<br>Master Mode                      |

| 2                       | Master Mode,<br>COM = prim channel,<br>AUX enable is following<br>prim-ch 1) | 110                                                                     | В                               | В      | Α      | Α      | COM <sup>2)</sup><br>AUX | push/ pull           | Saves one interconnection wire (AUX_EN) to µC                 |

| 3                       | Master Mode, AUX = prim channel, COM enable is following prim-ch 3)          | 111                                                                     | Α                               | Α      | В      | В      | AUX                      | push/ pull high-Z if | Process (IO-<br>Link) and<br>Service (SPI)<br>data separation |

| 4                       | Master Mode, AUX = prim channel, COM is disabled 4)                          | 101                                                                     | Α                               | Α      | В      | С      |                          | = high               | - SPI pin bus wiring!                                         |

<sup>1)</sup> If AUX\_EN is permanently wired to GND, the total driver strength can be controlled by toggling the MASTER\_SENS\_CTRL[6] bit (0: AUX disabled using just COM/ 1: AUX enabled if COM is enabled = double strength).

Switching between type 1 and 2 via SPI

<sup>&</sup>lt;sup>2)</sup> The logic value of the COM receiver output (RX) is available if the SPI communication is disabled (SPI\_EN\_L = 1).

<sup>3)</sup> Driver strength is "double" – "WAKE\_UP\_MODE". The total driver strength can be decreased by switching to type 4 (single strength).

4) Driver strength is "single". The total driver strength can be increased by switching to type 3 (double strength)

#### 3.2.2. Transmitter

#### 3.2.2.1. General functionality

The IC versions ZIOL24xx consists of two<sup>1</sup> independent driver stages. Each driver (COM/AUX) is configurable as regards the parameter

- Output current limitation

- Output slew rate

- Driver function (push, pull, pull ups/downs)

Several Modes of operation are supported – as independent or as combined driver outputs.

#### 3.2.2.2. Modes of operation (IO-Link specific Operation)

Operating both on-chip drivers independently or in parallel ensures the IC utilization in a wide range of applications. An example can be the different requirements of driver capability in master or device mode regarding the IO-Link specification (refer also to chapter 3.3.2). Both modes are supported by the ZIOL2xxx Ics. The active mode is defined in the configuration register [7] bit 7. The chosen mode influences the IC's driver behavior as well as the handling of overload exceptions. Both input channels do not depend on the operational mode.

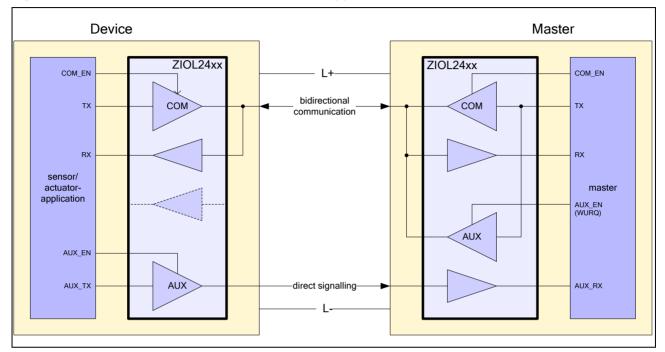

**In master mode**<sup>2</sup> the data inputs (TX) of both drivers are connected internally. As regards their functionality both drivers work in parallel. Therefore, the driver outputs have to be interconnected externally in master mode.

**In device mode** both drivers are working independently. A respective current overload signal will be generated if at one or at both drivers the output current exceeds the set current limit for longer than the configured amount of time.

Figure 3.5 shows a simplified application circuit including ZIOL24xx lcs in device and in master mode, respectively. Although both drivers are controlled by the same "TX" signal in master mode, the driver strength can be influenced with the COM\_EN and AUX\_EN signal thus the resulting driver strength can be reduced in this mode.

Starting with Rev B of the IC the MASTER\_MODE flag (configuration register MASTER\_SENS\_CTRL[7] replaces the formerly used control via an input pin. Summarizing the above, the MASTER MODE flag controls:

- The Data path; it controls whether both channels use an individual or common TX signal

- The current sinks at the receiver's inputs in the IO-Link sink mode (refer to Table 3.4)

For more information about the data path configuration of the IC in device and in mode master, please refer to chapter 3.2.1.

<sup>&</sup>lt;sup>1</sup> Note: The IC versions ZIOL22xx/21xx have just one channel. With respect to those IC versions the statements concerning the existence of two channels shall be ignored or interpreted analogously.

<sup>&</sup>lt;sup>2</sup> Not applicable for the IC versions ZIOL22xx/21xx

Figure 3.5 ZIOL24xx in Device and Master Mode Application

The illustration in Figure 3.5 shows the principal way of using the ZIOL2xxx integrated circuit in master and device mode. Figure 3.5 does not include all required electronic components of the application circuit which are mentioned in chapter 4 (Figure 4.1 and Figure 4.2).

#### 3.2.2.3. Configuration

The COM and AUX drivers are built identically. Their features can be configured in a wide range. The behavior of the output stages can be set to push, pull or push/pull. Current limitation and the overload timing can be set individually. In order to improve the EMC system behavior the slew rate of the output signal is controlled and can be set according to the needs of the application. The following table gives an overview of the possible configurations for the COM and AUX driver in master and device mode, respectively.

Table 3.2 Driver configurations

| Parameter                                       | ConfigRegister                      | Reg<br>Addr. | Bit-<br>Field | Ranges                                         | s & Coding                                               | Unit           | Remarks <sup>1)</sup>                                                                                               |

|-------------------------------------------------|-------------------------------------|--------------|---------------|------------------------------------------------|----------------------------------------------------------|----------------|---------------------------------------------------------------------------------------------------------------------|

| COM and AUX driver output current limitation    | COM_PARAM,<br>AUX_PARAM             | 2<br>4       | 4:2           | 0b000:<br>0b010:<br>0b100:<br>0b110:<br>0bxx1: | 50<br>100<br>200<br>250<br>limitation off <sup>2)</sup>  | mA<br>mA<br>mA | IC in Device mode: both drivers work independently                                                                  |

| Combined driver output current limitation       | COM_PARAM,<br>AUX_PARAM             | 2<br>4       | 4:2           | 0b000:<br>0b010:<br>0b100:<br>0b110:<br>0bxx1: | 100<br>200<br>400<br>500<br>limitation off <sup>2)</sup> | mA<br>mA<br>mA | IC in Master mode: both<br>drivers work in parallel<br>Both drivers shall be set to<br>identical driver capability. |

| Slew Rate Control                               | COM_CTRL,<br>AUX_CTRL               | 1<br>3       | 4:3           | 0b00:<br>0b10:<br>0b01:<br>0b11:               | 10<br>60<br>slow<br>control off<br>fast<br>control off   | V/μs<br>V/μs   | Limitation of maximal edge<br>steepness.<br>Limitation turned off!<br>Limitation turned off!                        |

| Output characteristic                           | COM_CTRL,<br>AUX_CTRL               | 1<br>3       | 1:0           | 0b00:<br>0b01:<br>0b10:<br>0b11:               | off<br>pull<br>push<br>push+pull                         |                |                                                                                                                     |

| Overload time base –<br>COM, AUX                | COM_MON_CTRL,<br>AUX_MON_CTRL       | 11<br>13     | 6:5           | 0b00:<br>0b01:<br>0b10:<br>0b11:               | 0.2<br>1000<br>8000<br>16000                             | μs             | Defines the clock<br>frequency for COM/AUX<br>overload counters                                                     |

| Overload counter<br>compare value – COM,<br>AUX | COM_ASSERT_TIME,<br>AUX_ASSERT_TIME | 10<br>12     | 7:0           |                                                | Byte                                                     |                | If overload counter value equals compare value an overload will be asserted                                         |

| Pull up/down enable – COM, AUX                  | COM_PARAM,<br>AUX_PARAM             | 2<br>4       | 6:5           | Bit 6:<br>Bit 5:                               | pull-up<br>pull-down                                     |                | Enables resistor of typical 150kOhms                                                                                |

<sup>&</sup>lt;sup>1)</sup> For a summary of all configuration registers, please refer to Table 3.7.

#### 3.2.3. Receiver

#### 3.2.3.1. General Functionality

In principle, the ZIOL2xxx IC family has two<sup>1</sup> identical input channels with a configurable feature set. The input threshold levels can be set ratiometric or absolute. The absolute values are compatible with definition of Type 1 digital inputs in IEC61131-2 and conform to the IO-Link specification. The ratiometric levels<sup>2</sup> are proportional to the HV power supply voltage. The ratiometric level configuration allows the input channels to function down to a

-

<sup>2)</sup> Not recommended due to chance of overheating

<sup>&</sup>lt;sup>1</sup> Note: The IC versions ZIOL22xx/21xx have only one receiver.

<sup>&</sup>lt;sup>2</sup> Note: Ripple on the supply voltage may have influence to the trip-point of the input stage. Another influence to be considered is that an enabled analog input filter is reducing the ripple on the on the received signal.

supply voltage of 8V. For each input channel an analog and a digital filter are implemented, which can separately be enabled.

### 3.2.3.2. Configuration

The following table gives an overview of the possible configurations for the COM and AUX input channels.

Table 3.3 Receiver configurations

| Parameter                         | Config<br>Register      | Reg<br>Addr. | Bit-<br>Field | Setting / Range                  |                                          | Unit | Remarks <sup>1)</sup>                                                                       |

|-----------------------------------|-------------------------|--------------|---------------|----------------------------------|------------------------------------------|------|---------------------------------------------------------------------------------------------|

| Threshold level for COM and AUX   | COM_CTRL,<br>AUX_CTRL   | 1<br>3       | 5             | 0b0:<br>0b1:                     | absolute ratiometric                     |      | Absolute = IO-Link compliant thresholds                                                     |

| Analogue filter                   | COM_CTRL,<br>AUX_CTRL   | 1<br>3       | 2             | 0b0:<br>0b1:                     | disabled<br>enabled                      |      |                                                                                             |

| Digital filter                    | COM_CTRL,<br>AUX_CTRL   | 1<br>3       | 7             | 0b0:<br>0b1:                     | disabled<br>enabled                      |      |                                                                                             |

| I <sub>sink</sub> , sink strength | COM_PARAM,<br>AUX_PARAM | 2<br>4       | 7             | 0b0:<br>0b1:                     | 2 – 3<br>5 – 7                           | mA   |                                                                                             |

| Sink mode                         | COM_PARAM,<br>AUX_PARAM | 2<br>4       | 1:0           | 0b00:<br>0b01:<br>0b10:<br>0b11: | off<br>IO-Link<br>follow<br>driver<br>on |      | Following driver: if driver is enabled then sink = off if driver is disabled then sink = on |

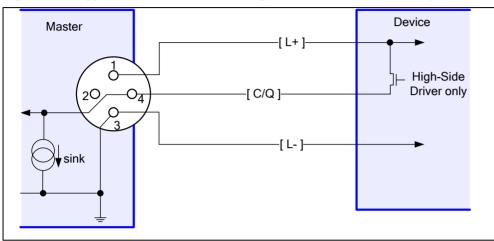

#### 3.2.3.3. Sink Modes

The IO-Link standard defines a possible configuration option, in which the device drives the signal line only with a high side driver thus the logic low level will be generated with a current sink on the master side (Figure 3.6). The ZIOL2xxx supports the current sinks in different modes on master side (for details refer to Table 3.4).

Figure 3.6 Typical IO-Link Device Configuration with HS driver only

Table 3.4 Sink Mode Configuration in Detail

| Register[2][1:0]<br>Register[4][1:0]                                             | Mode                         | Sink enabling                                                   | Remark                                                                                                                                             |  |  |  |

|----------------------------------------------------------------------------------|------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 00                                                                               | n.a.                         | Sink steady disabled                                            | OFF                                                                                                                                                |  |  |  |

| 01                                                                               | Device<br>Mode <sup>1)</sup> | Sink steady disabled                                            | Typical application mode for the IO-Link channel:  device: no sink                                                                                 |  |  |  |

|                                                                                  | Master<br>Mode <sup>2)</sup> | Sink enabled if:  TX_EN/SPI_CLK = low (COM) AUX_EN = low (AUX)  | master: sink enabled contrary to the corresponding driver enable signal                                                                            |  |  |  |

| 10                                                                               | n.a.                         | Sink enabled if:  TX_EN/SPI_CLK = low (COM)  AUX_EN = low (AUX) | Enabling contrary to the driver enable signal; sink is only enabled while the driver is disabled. (helps to reduce the system's power dissipation) |  |  |  |

| 11                                                                               | n.a.                         | steady enabled                                                  | ON                                                                                                                                                 |  |  |  |

| 1) MASTER_MODE flag (configuration register MASTER_SENS_CTRL[7] is cleared (=0). |                              |                                                                 |                                                                                                                                                    |  |  |  |

MASTER\_MODE flag (configuration register MASTER\_SENS\_CTRL[7] is set (=1).

#### 3.3. **System Control**

#### 3.3.1. General

The system control provides device configuration, status signaling and SPI data transfer functionality. Implemented are several register areas which contain configuration data and which provide status information. In order to gain read/write access to these register areas, the standard serial peripheral interface (SPI) is implemented. Since the pin count of the package is limited to 24 pins, the SPI specific pins (CLK, MOSI, and MISO) are multiplexed with IO-pins of the COM driver. A dedicated pin SPI\_EN\_L is used to switch between SPI

(logic low) and COM transceiver functionality (logic high). The low voltage (LV) interface works with 3.3V supply voltage (refer to Figure 3.1). The LV outputs drive 3.3V as high level, the inputs are 5V tolerant.

If the SPI communication channel of the ZIOL2xxx Ics is active (SPI\_EN\_L = low), the status of the COM channel drivers is kept. This means while SPI\_EN\_L = low the output driver status (driving low, driving high, or high-z) is the same as defined by the pins TX\_EN/SPI\_CLK and TX/MOSI at the point of time of the SPI\_EN\_L high-low transition. The AUX channel is not affected by the activity of the SPI communication. For more information, please refer to chapter 3.3.8 and Figure 3.10.

### 3.3.2. IO-Link Master<sup>1</sup> and Device Mode

The IC architecture is suitable for both IO-Link application cases, the physical layer transceiver at an IO-Link master port and at an IO-Link device port. In the first case the IC shall operate in its "master mode" which is the case if configuration register [7] bit 7 is set (=1). If the IC shall operate in "device mode", configuration register [7] bit 7 shall be cleared (=0). Details regarding the control of both driver channels are described in chapter 3.2.1, 3.2.2.2 and 3.2.3.3.

The IO-Link specific WURQ detection (detection of an IO-Link master's wake-up request, refer to IO-Link Communication Specification – chapter 8, [2]) works only in device mode.

### 3.3.3. Internal Exceptions

Depending on the IC configuration the ZIOL2xxx can detect several critical situations and rise internal exceptions accordingly. Also depending on the IC configuration an occurred internal exception can be indicated externally by changing the logic level of the INT-L pin to "low". The situations that cause an internal exception are channel locks (channel driver protection), detected IO-Link specific Wake-Up pulses and several issues concerning the internal EEPROM as described in chapter 3.3.10.

## 3.3.4. IO-Link specific Wake-Up (WURQ)

In device mode the IC can detect the IO-Link specific wake-up request (WURQ) of the IO-Link master and can therefore help to save resources in the microcontroller of IO-Link device. As regards the IO-Link specific "Wake-Up (WURQ)" specification, please refer to the IO-Link Communication Specification issued by the IO-Link consortium (refer to chapter 8, [2]).

The WURQ can be detected on the COM or on the AUX channel. The chosen channel is defined in a configuration register (IRQ WURQ CTRL, refer to chapter 3.3.9).

In order to establish an IO-Link specific communication, the master will generate the WURQ event. In this case the master overdrives the devices output level for a determined period. The ZIOL2xxx can detect that event which physically occurs in two ways:

- · A current overload in the drivers output for a certain period

- A contradiction of the TX and RX lines of the device for a certain period

The IC configuration register (IRQ\_WURQ\_CTRL, refer to chapter 3.3.9) defines if the "overload" or the "contradiction" or both events shall be chosen for the WURQ detection. Both ways of detection can be enabled

<sup>&</sup>lt;sup>1</sup> Not applicable for the IC versions ZIOL22xx/21xx.

independently. If at least one of both events appears for a specific time, the incident will be regarded as WURQ request from master side and the IC will generate an internal exception (issue an interrupt) in order to signal this to the interconnected  $\mu$ C. Besides the configurable signaling on the INT\_L pin (refer to chapter 3.3.10.1) this special exception will be displayed on the therefore dedicated WURQ\_L pin. Details of the signaling via the WURQ\_L and/or the INT\_L pin and the pin driver configuration of the WURQ\_L pin can be defined in the configuration registers which are described in detail in chapter 3.3.9.

The logic level of the WURQ\_L pin (a wake-up causes logic low) or the stored WURQ event will be reset as soon as the drivers direction is set to input (TX\_EN=0), which equals the WURQ acknowledge from the IO-Link device side.

The on logic level based WURQ detection works only for level-changes which are driven by the master. That means a WURQ will not be detected if a level change has been initiated by the device itself, even if the signal timing is equivalent to a WURQ event. This prevents the in SIO mode operating IO-Link device to misinterpret the situation caused for instance by capacitive loads.

If the ZIOL2xxx operates in master mode (physical interface for IO-Link master port) and a Wake-Up pulse (WURQ) shall be issued, the  $\mu$ C has to control the required driver strength by activating both channels (via COM\_EN and AUX\_EN, refer to Figure 3.5) and has to provide the correct timing.

Figure 3.7 Wake-Up Signal Recognition

The WURQ pulse recognition of the ZIOL2xxx in device mode is – in contrast to that – based on a time base derived from the internal oscillator (OSC). Therefore the as WURQ recognized pulse width range of an received Wake-Up signal is dependent on the frequency tolerance of the internal oscillator as illustrated in Figure 3.7. A Wake-Up signal (pulse width according to the IO-Link Communication Specification, refer to chapter 8, [2]) shall have a pulse width between 75 $\mu$ s and 85 $\mu$ s (variation 10 $\mu$ s). The ZIOL2xxx Wake-Up signal detection will always recognize such a signal securely considering a frequency tolerance of the internal oscillator of ±10% (refer to parameter  $f_{osc}$  in Table 2.3).

#### 3.3.5. IC Self-Protection – Lock Mode

In order to prevent serious IC damage due to overloaded or overheated driver transistors, the IC has a build-in protection mechanism. If a critical situation occurs for a certain configurable time, the IC can protect itself in transferring its control in a special mode, called lock mode, in which the driver of the related channel is turned-off in case of over-current, or in case of over-temperature the drivers of both channels are turned-off, respectively.

Figure 3.8 shows the basic scheme of the IC self protection. In principle, this scheme is five times implemented in order to tread:

- Over-current situations separately at the high side and at the low side switch of the COM channel as described in Figure 3.15

- Over-current situations separately at the high side and at the low side switch of the AUX channel as described in Figure 3.16

- Over-temperature situations of the silicon die as described in Figure 3.17

In case of an over-current or over-temperature situation occurs (in the following called overload) the related over-current/over-temperature counter (overload counter) will count up. Since the overload counter counts down to zero in case of no overload is existent, the circuit performs an integrator function. This integrator function makes sure that overloads which temporarily occur are not accumulated thus will not lead to an unwanted driver locks.

If the overload counter has reached the (in the related configuration register) defined maximum value, the IC will generate an internal exception. This exception will lock the associated channel or both channels in case of an over-temperature situation. The "assert Time" (refer to Figure 3.8) which is the elapsed time in until reaching the configured maximum of the overload counter depends on the used clock period for the overload counter. This clock period can be defined separately for the lock control circuit of each channel (Figure 3.15, Figure 3.16) and the temperature lock control circuit (Figure 3.17) in the associated configuration register.

To each overload counter is a peak register associated. The value of the overload counters can not be retrieved via the SPI port. However, the value of the overload counter will be copied in the related peak register if the value of the overload counter is greater than the value of the peak register. The peak registers can be read via the SPI port. The content of the peak register will be cleared after each read access. However, within the next cycle of the IC control circuit the peak register will be set to the overload counter value again if this value is greater than zero.

The above described peak register update is only performed if an overload situation is present. In case of overload situation the peak register is an important instrument to perform an IC diagnostic. For more information about techniques to operate the peak, please refer to Appendix A.

A due to an overload raised internal exception will cause in case of over-current a lock of the related channel or a lock of both channels in case of a over-temperature situation. There are three signals (displayed in status register[20] which indicate the lock activator. The other five bits of this status register indicate what IC sensor has detected an over-current or if the configured maximum of the die temperature has been exceeded.