Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# ZL30252, ZL30253

# 3-Input, 3-Output Any-to-Any Clock Multiplier and Jitter Attenuator ICs

**Data Sheet**

July 2016

#### **Features**

# Input Clocks

- Three inputs: two differential/CMOS, one CMOS

- Any input frequency from 1kHz to 1250MHz (1kHz to 300MHz for CMOS)

- Inputs continually monitored for activity and frequency accuracy

- Automatic or manual reference switching

#### Low-Bandwidth DPLL

- Programmable bandwidth, 14Hz to 500Hz

- Attenuates jitter up to several UI

- Freerun or digital hold on loss of all inputs

- · Digitally controlled phase adjustment

# Low-Jitter Fractional-N APLL and 3 Outputs

- Any output frequency from <1Hz to 1035MHz</li>

- High-resolution fractional frequency conversion with 0ppm error

- Easy-to-configure, encapsulated design requires no external VCXO or loop filter components

- Each output has independent dividers

- Output jitter is typically 0.16 to 0.28ps RMS (12kHz-20MHz integration band)

- Outputs are CML or 2xCMOS, can interface to LVDS, LVPECL, HSTL, SSTL and HCSL

- In 2xCMOS mode, the P and N pins can be different frequencies (e.g. 125MHz and 25MHz)

#### **Ordering Information**

ZL30252LDG1 32 Pin QFN Trays

ZL30252LDF1 32 Pin QFN Tape and Reel

ZL30253LDG1 32 Pin QFN Trays

ZL30253LDF1 32 Pin QFN Tape and Reel

Matte Tin

Package size: 5 x 5 mm

-40°C to +85°C

- Per-output supply pin with CMOS output voltages from 1.5V to 3.3V

- Precise output alignment circuitry and peroutput phase adjustment

- Per-output enable/disable and glitchless start/stop (stop high or low)

#### General Features

- Automatic self-configuration at power-up from external (ZL30252) or internal (ZL30253) EEPROM; up to four configs pin-selectable

- Numerically controlled oscillator mode

- Spread-spectrum modulation mode

- Zero-delay mode with external feedback

- SPI or I<sup>2</sup>C processor Interface

- Easy-to-use evaluation software

# **Applications**

Frequency conversion, jitter attenuation and frequency synthesis in a wide variety of equipment types

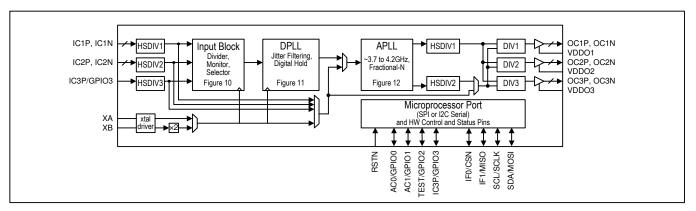

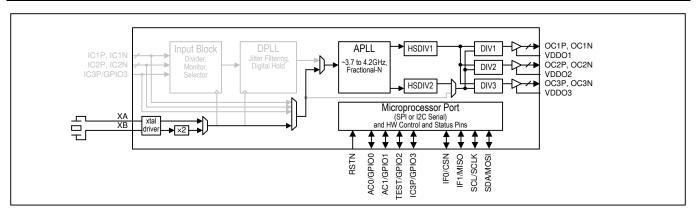

Figure 1 - Functional Block Diagram

# Table of Contents

| 1.  | APP    | LICATION EXAMPLES                                          | . 6 |

|-----|--------|------------------------------------------------------------|-----|

| 2.  | DET    | AILED FEATURES                                             | . 6 |

| 2.1 | l INE  | PUT BLOCK FEATURES                                         | 6   |

| 2.2 |        | LL FEATURES                                                |     |

| 2.3 |        | LL FEATURES                                                |     |

| 2.4 |        | TPUT CLOCK FEATURES                                        |     |

| 2.5 |        |                                                            |     |

|     |        | NERAL FEATURES                                             |     |

| 2.6 |        | ALUATION SOFTWARE                                          |     |

| 3.  | PIN I  | DIAGRAM                                                    | . 8 |

| 4.  | PIN I  | DESCRIPTIONS                                               | . 9 |

| 5.  | FUN    | CTIONAL DESCRIPTION                                        | 11  |

| 5.1 | l De   | VICE IDENTIFICATION                                        | 11  |

| 5.2 |        | P-LEVEL CONFIGURATION                                      |     |

|     | 5.2.1  | APLL-Only Mode                                             |     |

|     | 5.2.2  | DPLL+APLL Mode                                             |     |

|     | 5.2.3  | Evaluation Software for Device Configuration               |     |

| 5.3 |        | I-CONTROLLED AUTOMATIC CONFIGURATION AT RESET              |     |

|     | 5.3.1  | ZL30252—External EEPROM or No EEPROM                       |     |

|     | 5.3.2  | ZL30253—Internal EEPROM.                                   |     |

|     |        | CAL OSCILLATOR OR CRYSTAL                                  |     |

|     | 5.4.1  | External Oscillator                                        |     |

| į   | 5.4.2  | External Crystal and On-Chip Driver Circuit                |     |

|     | 5.4.3  | Clock Doubler                                              |     |

|     | 5.4.4  | Ring Oscillator (for System Start-Up)                      | 16  |

| 5.5 | 5 INF  | PUT SIGNAL FORMAT CONFIGURATION                            | 17  |

| 5.6 | S INF  | PUT BLOCK: INPUT DIVIDER, MONITOR AND SELECTOR             | 17  |

|     | 5.6.1  | Input Clock Inversion and High-Speed Dividers              |     |

| 4   | 5.6.2  | Input Clock Monitoring                                     |     |

|     | 5.6.2. |                                                            | 18  |

|     | 5.6.2. | 2 Monitor Priority and Validation Timer                    | 18  |

|     | 5.6.2. |                                                            |     |

|     | 5.6.3  | Input Clock Priority, Selection and Switching for the DPLL |     |

|     | 5.6.3. | - · · · · · · · · · · · · · · · · · · ·                    |     |

|     | 5.6.3. |                                                            |     |

|     | 5.6.3. |                                                            |     |

|     | 5.6.3. |                                                            |     |

| 5.7 |        | LL ARCHITECTURE AND CONFIGURATION                          |     |

|     | 5.7.1  | DPLL Configuration                                         |     |

|     | 5.7.2  | DPLL States                                                |     |

|     | 5.7.3  | DPLL Capabilities                                          |     |

|     | 5.7.4  | Input Wander and Jitter Tolerance                          |     |

|     | 5.7.5  | Jitter and Wander Transfer                                 |     |

|     | 5.7.6  | Output Jitter and Wander                                   |     |

|     | 5.7.7  | Numerically Controlled Oscillator (NCO) Mode               |     |

|     | 5.7.8  | Spread-Spectrum Modulation Mode                            |     |

| 5.8 |        | LL CONFIGURATION                                           |     |

|     | 5.8.1  | APLL Input Selection and Frequency                         |     |

|     | 5.8.1. | 1 APLL-Only Mode                                           | 23  |

|            | 5.8.1.2 DPLL+APLL Mode                                          |       |

|------------|-----------------------------------------------------------------|-------|

|            | 5.8.2 APLL Output Frequency                                     |       |

|            | 5.8.3 APLL Phase Adjustment                                     |       |

|            | OUTPUT CLOCK CONFIGURATION                                      | 25    |

|            | 5.9.1 Output Enable, Signal Format, Voltage and Interfacing     | 25    |

| <i>5</i> . | 5.9.2 Output Frequency Configuration                            | 26    |

| <i>5</i> . | 5.9.3 Output Duty Cycle Adjustment                              |       |

| <i>5</i> . | 5.9.4 Output Phase Adjustment and Phase Alignment               |       |

|            | 5.9.4.1 Phase Adjustment                                        |       |

|            | 5.9.4.2 Phase Alignment, Output-to-Output                       |       |

|            | 5.9.4.3 Phase Alignment, Input-to-Output                        |       |

|            | 5.9.5 Output Clock Start and Stop                               |       |

|            | 5.9.6 A-to-B Phase Offset Measurement                           |       |

| 5.10       |                                                                 |       |

|            | 5.10.1 SPI Slave                                                |       |

|            | 5.10.2 SPI Master (ZL30252 Only)                                |       |

|            | 5.10.3                                                          |       |

| 5.1        |                                                                 |       |

| 5.12       |                                                                 |       |

| 5.13       | 3 POWER-SUPPLY CONSIDERATIONS                                   | 39    |

| 5.14       | 4 AUTO-CONFIGURATION FROM EEPROM                                | 39    |

| <i>5</i> . | 5.14.1 Generating Device Configurations                         | 39    |

|            | 5.14.2 Direct EEPROM Write Mode (ZL30253 Only)                  |       |

| <i>5</i> . | 5.14.3 Holding Other Devices in Reset During Auto-Configuration | 40    |

| 5.1        |                                                                 |       |

| 6.         | REGISTER DESCRIPTIONS                                           | 40    |

|            |                                                                 |       |

| 6.1        |                                                                 |       |

|            | S.1.1 Status Bits                                               |       |

|            | 5.1.2 Configuration Fields                                      |       |

|            | 5.1.3 Multiregister Fields                                      |       |

|            | 5.1.4 Bank-Switched Registers (ZL30253 Only)                    |       |

|            | S.1.5 DPLL Registers                                            |       |

| 6.2        |                                                                 |       |

| 6.3        |                                                                 |       |

|            | 5.3.1 Global Configuration Registers                            |       |

|            | 5.3.2 Status Registers                                          |       |

|            | 5.3.3 APLL Configuration Registers                              |       |

|            | S.3.4 Output Clock Configuration Registers                      |       |

|            | 5.3.6 DPLL Configuration Registers                              |       |

|            | 3                                                               |       |

| <b>7.</b>  | ELECTRICAL CHARACTERISTICS                                      | 89    |

| 8.         | PACKAGE AND THERMAL INFORMATION                                 | 100   |

| 8.1        |                                                                 |       |

| 8.2        |                                                                 |       |

| _          |                                                                 |       |

| 9.         | MECHANICAL DRAWING                                              | 102   |

| 10.        | ACRONYMS AND ABBREVIATIONS                                      | 103   |

| 11         | DATA SHEET REVISION HISTORY                                     | 104   |

|            | 11010 30CC   BCVI3IIIV DI311BY                                  | 111/1 |

# List of Figures

| Figure 1 - Functional Block Diagram                                                          | 1  |

|----------------------------------------------------------------------------------------------|----|

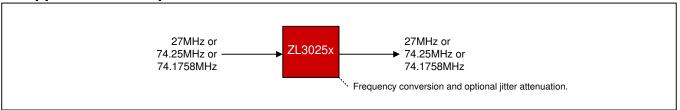

| Figure 2 – Broadcast Video Frequency Conversion Application                                  | 6  |

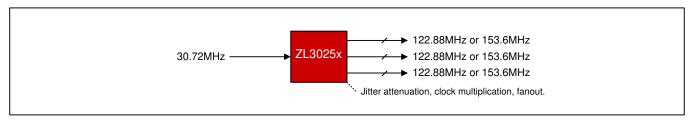

| Figure 3 – Wireless Base Station Jitter Filtering and Frequency Conversion Application       | 6  |

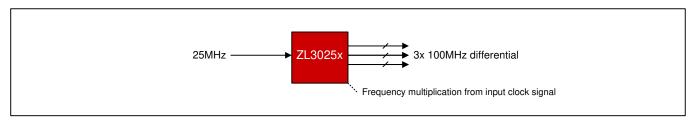

| Figure 4 - PCI Express Frequency Multiplication Application                                  |    |

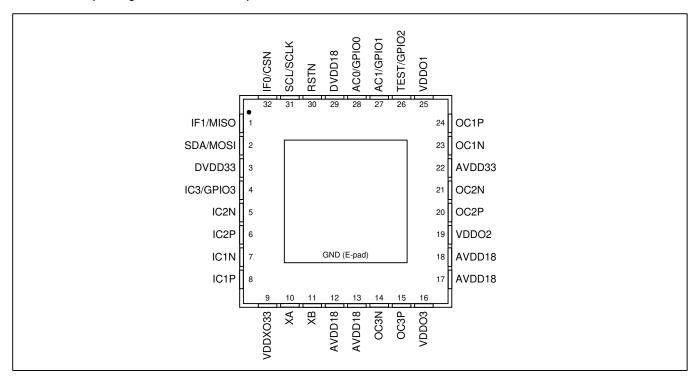

| Figure 5 - Pin Diagram                                                                       |    |

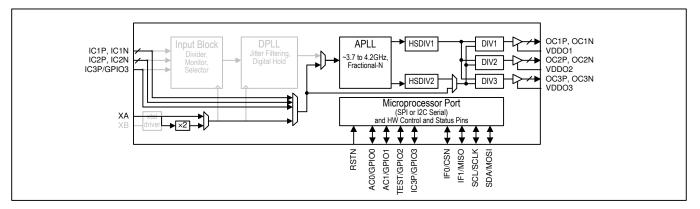

| Figure 6 - APLL-Only Mode: Clock Synthesis from a Crystal                                    | 12 |

| Figure 7 - APLL-Only Mode: Frequency Conversion from One of Four Input Clocks                | 12 |

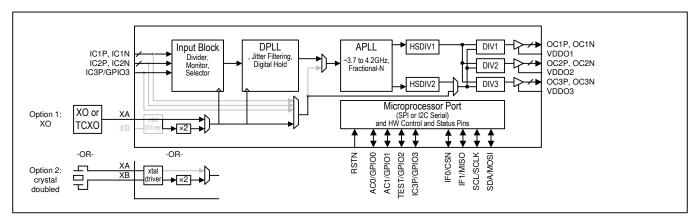

| Figure 8 - DPLL+APLL Mode: Locked to One of Three Inputs, Master Clock from XO or Crystal    | 13 |

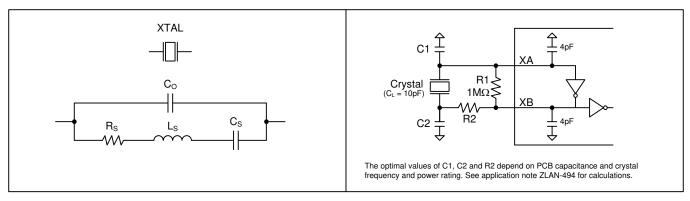

| Figure 9 - Crystal Equivalent Circuit / Recommended Crystal Circuit                          | 16 |

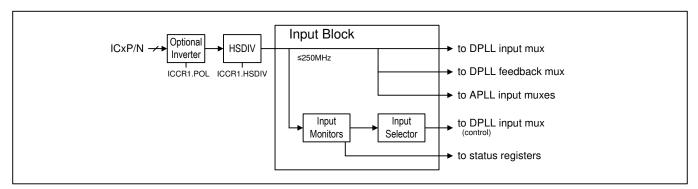

| Figure 10 - Input Block Diagram                                                              | 17 |

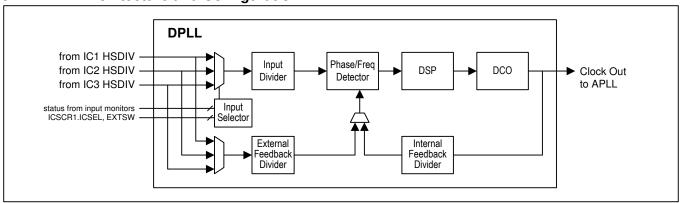

| Figure 11 - DPLL Block Diagram                                                               | 20 |

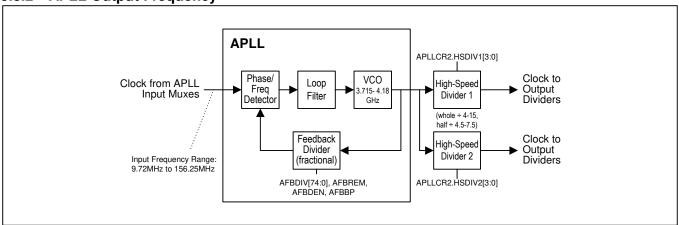

| Figure 12 - APLL Block Diagram                                                               | 24 |

| Figure 13 - SPI Read Transaction Functional Timing                                           | 34 |

| Figure 14 - SPI Write Enable Transaction Functional Timing (ZL30253 Only)                    | 34 |

| Figure 15 - SPI Write Transaction Functional Timing                                          | 35 |

| Figure 16 – I <sup>2</sup> C Read Transaction Functional Timing                              |    |

| Figure 17 – I <sup>2</sup> C Register Write Transaction Functional Timing                    | 37 |

| Figure 18 – I <sup>2</sup> C EEPROM Write Transaction Functional Timing (ZL30253 Only)       |    |

| Figure 19 – I <sup>2</sup> C EEPROM Read Status Transaction Functional Timing (ZL30253 Only) | 37 |

| Figure 20 – Interrupt Structure                                                              | 38 |

| Figure 21 - Electrical Characteristics: Clock Inputs                                         |    |

| Figure 22 - Example External Components for Differential Input Signals                       | 92 |

| Figure 23 - Electrical Characteristics: CML Clock Outputs                                    | 93 |

| Figure 24 – Example External Components for CML Output Signals                               | 93 |

| Figure 25 – Example External Components for HCSL Output Signals                              | 94 |

| Figure 26 - SPI Interface Timing                                                             |    |

| Figure 27 - SPI Master Interface Timing                                                      | 98 |

| Figure 28 - I <sup>2</sup> C Slave Interface Timing                                          |    |

| Figure 27 - Non-customized Device Top Mark                                                   |    |

| Figure 28 - Custom Factory Programmed Device Top Mark                                        |    |

|                                                                                               | List of Tables |

|-----------------------------------------------------------------------------------------------|----------------|

| Table 1 - Pin Descriptions                                                                    | 9              |

| Table 2 - Crystal Selection Parameters                                                        | 16             |

| Table 3 - Default Input Clock Priorities                                                      | 19             |

| Table 4 – SPI Commands                                                                        | 33             |

| Table 5 - Register Map                                                                        | 41             |

| Table 6 - Recommended DC Operating Conditions                                                 | 89             |

| Table 7 - Electrical Characteristics: Supply Currents                                         | 89             |

| Table 8 - Electrical Characteristics: Non-clock CMOS Pins                                     | 90             |

| Table 9 - Electrical Characteristics: XA Clock Input                                          | 90             |

| Table 10 - Electrical Characteristics: Clock Inputs, ICxP/N                                   |                |

| Table 11 - Electrical Characteristics: CML Clock Outputs                                      | 92             |

| Table 12 - Electrical Characteristics: CMOS and HSTL (Class I) Clock Outputs                  | 94             |

| Table 13 - Electrical Characteristics: APLL Frequencies                                       | 94             |

| Table 14 - Electrical Characteristics: Jitter Specifications                                  |                |

| Table 15 - Electrical Characteristics: Typical Output Jitter Performance, APLL Only           | 95             |

| Table 16 - Electrical Characteristics: Typical Output Jitter Performance, DPLL+APLL           | 95             |

| Table 17 - Electrical Characteristics: Typical Input-to-Output Clock Delay                    | 96             |

| Table 18 - Electrical Characteristics: Typical Output-to-Output Clock Delay                   | 96             |

| Table 19 - Electrical Characteristics: SPI Slave Interface Timing, Device Registers           |                |

| Table 20 - Electrical Characteristics: SPI Slave Interface Timing, Internal EEPROM (ZL30253 C | Only) 97       |

| Table 21 - Electrical Characteristics: SPI Master Interface Timing (ZL30252 Only)             | 98             |

| Table 22 - Electrical Characteristics: I <sup>2</sup> C Slave Interface Timing                | 99             |

| Table 22 – Package Top Mark Legend                                                            |                |

| Table 23 - 5x5mm QFN Package Thermal Properties                                               | 101            |

# 1. Application Examples

Figure 2 - Broadcast Video Frequency Conversion Application

Figure 3 - Wireless Base Station Jitter Filtering and Frequency Conversion Application

Figure 4 - PCI Express Frequency Multiplication Application

# 2. Detailed Features

## 2.1 Input Block Features

- Three input clocks, two differential or single-ended, one single-ended

- Input clocks can be any frequency from 1kHz up to 1250MHz (differential) or 300MHz (single-ended)

- Inputs constantly monitored by programmable activity monitors and frequency monitors

- · Fast activity monitor can disqualify the selected reference after a few missing clock cycles

- Frequency measurement and monitoring with 1% resolution

- Optional input clock invalidation on GPIO assertion to react to LOS signals from PHYs

# 2.2 DPLL Features

- Very high-resolution DPLL architecture

- State machine automatically transitions between tracking and freerun/digital-hold states

- Revertive or nonrevertive reference selection algorithm

- Programmable bandwidth from 14Hz to 500Hz

- Programmable tracking range (i.e. hold-in range)

- Output phase adjustment in 10ps steps

- High-resolution frequency and phase measurement

- Fast detection of input clock failure and transition to digital hold

#### 2.3 APLL Features

- Very high-resolution fractional scaling (i.e. non-integer multiplication)

- Any-to-any frequency conversion with 0ppm error

- Two high-speed dividers (integers 4 to 15, half divides 4.5 to 7.5)

- Easy-to-configure, completely encapsulated design requires no external VCXO or loop filter components

- Bypass mode supports system testing

## 2.4 Output Clock Features

- Three low-jitter output clocks

- Each output can be one differential output or two CMOS outputs

- Output clocks can be any frequency from 1Hz to 1035MHz (250MHz max for CMOS and HSTL outputs)

- Output jitter is typically 0.16 to 0.28ps RMS (12kHz to 20MHz)

- In CMOS mode, an additional divider allows the OCxN pin to be an integer divisor of the OCxP pin (example: OC3P 125MHz, OC3N 25MHz)

- Outputs easily interface with CML, LVDS, LVPECL, HSTL, SSTL, HCSL and CMOS components

- Supported telecom frequencies include PDH, SDH, Synchronous Ethernet, OTN

- Can produce clock frequencies for microprocessors, ASICs, FPGAs and other components

- Can produce PCIe clocks (PCIe gen. 1, 2 and 3)

- Sophisticated output-to-output phase alignment

- · Per-output phase adjustment with high resolution and unlimited range

- Per-output enable/disable

- Per-output glitchless start/stop (stop high or low)

# 2.5 General Features

- SPI or I<sup>2</sup>C serial microprocessor interface

- Automatic self-configuration at power-up from external (ZL30252) or internal (ZL30253) EEPROM memory; pin control to specify one of four stored configurations

- Numerically controlled oscillator (NCO) mode allows system software to steer DPLL frequency with resolution better than 0.01ppb

- Spread-spectrum modulation mode (meets PCI Express requirements)

- Zero-delay buffer configuration using an external feedback path

- Four general-purpose I/O pins each with many possible status and control options

- Can operate as DPLL+APLL for jitter filtering and low bandwidth or as APLL only

- Local oscillator can be fundamental-mode crystal or low-cost XO

- Internal compensation for local oscillator frequency error

# 2.6 Evaluation Software

- Simple, intuitive Windows-based graphical user interface

- Supports all device features and register fields

- Makes lab evaluation of the ZL30252 or ZL30253 guick and easy

- Generates configuration scripts to be stored in external (ZL30252) or internal (ZL30253) EEPROM

- Generates full or partial configuration scripts to be run on a system processor

- Works with or without a ZL30252 or ZL30253 evaluation board

# 3. Pin Diagram

The device is packaged in a 5x5mm 32-pin QFN.

Figure 5 - Pin Diagram

# 4. Pin Descriptions

All device inputs and outputs are LVCMOS unless described otherwise. The Type column uses the following symbols: I – input,  $I_{PU}$  – input with  $50k\Omega$  internal pullup resistor, O – output, A – analog, P – power supply pin. All GPIO and SPI/I<sup>2</sup>C interface pins have Schmitt-trigger inputs and have output drivers that can be disabled (high impedance).

**Table 1 - Pin Descriptions**

| Pin#                             | Name                                         | Туре                                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------------------|----------------------------------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8<br>7<br>6<br>5<br>4            | IC1P<br>IC1N<br>IC2P<br>IC2N<br>IC3P/GPIO3   | <u>-</u> <u>-</u> <u>-</u> <u>-</u> <u>-</u> | <ul> <li>Input Clock Pins         Differential or Single-ended signal format. Programmable frequency.     </li> <li>Differential: See Table 10 for electrical specifications, and see Figure 22 for recommended external circuitry for interfacing these differential inputs to LVDS, LVPECL, CML or HSCL output pins on neighboring devices.     </li> <li>Single-ended: For input signal amplitude &gt;2.5V, connect the signal directly to ICxP pin. For input signal amplitude ≤2.5V, AC-coupling the signal to ICxP is recommended. Connect the N pin to a capacitor (0.1μF or 0.01μF) to VSS. As shown in Figure 22, the ICxP and ICxN pins are internally biased to approximately 1.3V. Treat the ICxN pin as a sensitive node; minimize stubs; do not connect to anything else including other ICxN pins.</li> <li>Unused: Set ICEN.ICxEN=0. The ICxP and ICxN pins can be left floating.</li> <li>Note that the IC3N pin is not bonded out. A differential signal can be connected to IC3P by AC-coupling the POS trace to IC3P and terminating the signal on the driver side of the coupling cap. If not needed as an input clock pin, IC3P can behave as general-purpose I/O pin GPIO3, which is configured by GPIOCR2. Its state is indicated in GPIOSR.</li> </ul> |

| 10<br>11                         | XA<br>XB                                     | A/I                                          | Crystal or Master Clock Pins  Crystal: MCR1.XAB=01. An on-chip crystal driver circuit is designed to work with an external crystal connected to the XA and XB pins. See section 5.4.2 for crystal characteristics and recommended external components.  Master Clock: MCR1.XAB=10. An external local oscillator or clock signal (95-125MHz) can be connected to the XA pin. The XB pin must be left unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 24<br>23<br>20<br>21<br>15<br>14 | OC1P<br>OC1N<br>OC2P<br>OC2N<br>OC3P<br>OC3N | 0                                            | Output Clock Pins CML, HSTL or 1 or 2 CMOS. Programmable frequency and drive strength. See Table 11 and Figure 24 for electrical specifications and recommended external circuitry for interfacing to LVDS, LVPECL or CML input pins on neighboring devices. See Table 12 for electrical specifications for interfacing to CMOS and HSTL inputs on neighboring devices. See Figure 25 for recommended external circuitry for interfacing to HCSL inputs on neighboring devices.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 30                               | RSTN                                         | <b>I</b> <sub>PU</sub>                       | <b>Reset (Active Low).</b> When this global asynchronous reset is pulled low, all internal circuitry is reset to default values. The device is held in reset as long as RSTN is low. See section 5.12.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Table 1 - | e 1 - Pin Descriptions (continued) |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|-----------|------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin#      | Name                               | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| 28<br>27  | AC0/GPIO0<br>AC1/GPIO1             | I/O  | Auto-Configure [1:0] / General Purpose I/O 0 and 1  Auto Configure: On the rising edge of RSTN these pins behave as AC[1:0] and specify one of the configurations stored in EEPROM. See section 5.3.  General-Purpose I/O: After reset these pins are GPIO0 and GPIO1. GPIOCR1 configures the pins. Their states are indicated in GPIOSR.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| 26        | TEST/GPIO2                         | I/O  | Factory Test / General Purpose I/O 2  Factory Test: On the rising edge of RSTN the pin behaves as TEST. Factory test mode is enabled when TEST is high. For normal operation TEST must be low on the rising edge of RSTN.  General-Purpose I/O: After reset this pin is GPIO2. GPIOCR2 configures the pin. It state is indicated in GPIOSR.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| 32        | IF0/CSN                            | I/O  | Interface Mode 0 / SPI Chip Select (Active Low)  Interface Mode: On the rising edge of RSTN the pin behaves as IF0 and, together with IF1, specifies the interface mode for the device. See section 5.3.  SPI Chip Select: After reset this pin is CSN. When the device is configured as a SPI slave, an external SPI master must assert (low) CSN to access device registers. When the device is configured as a SPI master (ZL30252 only), the device asserts CSN to access an external SPI EEPROM during autoconfiguration.                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 31        | SCL/SCLK                           | I/O  | I <sup>2</sup> C Clock / SPI Clock  f <sup>2</sup> C Clock: When the device is configured as an I <sup>2</sup> C slave, an external I <sup>2</sup> C master must provide the I <sup>2</sup> C clock signal on the SCL pin.  SPI Clock: When the device is configured as a SPI slave, an external SPI master must provide the SPI clock signal on SCLK. When the device is configured as a SPI master (ZL30252 only), the device drives SCLK as an output to clock accesses to an external SPI EEPROM during autoconfiguration.                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 1         | IF1/MISO                           | I/O  | Interface Mode 1 / SPI Master-In-Slave-Out  Interface Mode: On the rising edge of RSTN the pin behaves as IF1 and, together with IF0, specifies the interface mode for the device. See section 5.3.  SPI MISO: After reset this pin is MISO. When the device is configured as a SPI slave, the device outputs data to an external SPI master on MISO during SPI read transactions. When the device is configured as a SPI master (ZL30252 only), the device receives data on MISO from an external SPI EEPROM during auto-configuration.  Note: On rev A parts, in I <sup>2</sup> C interface mode this pin toggles between driving low and high-impedance during register accesses. Therefore in I <sup>2</sup> C mode this pin must not be wired directly to VDD. To implement a static high value on IF1/MISO, wire it to VDD through a resistor (approximately 10kΩ recommended). |  |  |  |

| 2         | SDA/MOSI                           | I/O  | I'C Data / SPI Master-Out-Slave-In  I'C Data: When the device is configured as an I'C slave, SDA is the bidirectional data line between the device and an external I'C master.  SPI MOSI: When the device is configured as a SPI slave, an external SPI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| Pin# | Name | Туре | Description                                                                                                                                                                                                                               |

|------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |      |      | master sends commands, addresses and data to the device on MOSI. When the device is configured as a SPI master (ZL30252 only), the device sends commands, addresses and data on MOSI to an external SPI EEPROM during auto-configuration. |

Table 1 - Pin Descriptions (continued)

| 12<br>13<br>17<br>18 | AVDD18  | Р | Analog Power Supply. 1.8V ±5%.                              |

|----------------------|---------|---|-------------------------------------------------------------|

| 22                   | AVDD33  | Р | Analog Power Supply. 3.3V ±5%.                              |

| 29                   | DVDD18  | Р | Digital Power Supply. 1.8V ±5%.                             |

| 3                    | DVDD33  | Р | Digital Power Supply. 3.3V ±5%.                             |

| 25                   | VDDO1   | Р | Output OC1 Power Supply. 1.5V to 3.3V ±5%.                  |

| 19                   | VDDO2   | Р | Output OC2 Power Supply. 1.5V to 3.3V ±5%.                  |

| 16                   | VDDO3   | Р | Output OC3 Power Supply. 1.5V to 3.3V ±5%.                  |

| 9                    | VDDXO33 | Р | Analog Power Supply for Crystal Driver Circuitry. 3.3V ±5%. |

| E-pad                | VSS     | Р | Ground. 0 Volts.                                            |

# 5. Functional Description

#### 5.1 Device Identification

The 12-bit read-only ID field and the 4-bit revision field are found in the ID1 and ID2 registers. Contact the factory to interpret the revision value and determine the latest revision.

# 5.2 Top-Level Configuration

The device has two fundamental modes of operation: APLL-only and DPLL+APLL.

## 5.2.1 APLL-Only Mode

In APLL-only mode, the input block and the DPLL are powered down (PLLEN.DPLLEN=0), and the device operates as a high-resolution fractional-N APLL. This reduces chip power consumption as shown in Table 7.

The bandwidth of the APLL is approximately 600kHz and therefore in APLL-only mode the device does not behave as a jitter filter. This means that, in applications where output signals must have sub-ps jitter, the APLL input signal must have sub-ps jitter. In addition, features of the input block and the DPLL including activity monitoring, frequency monitoring and jitter filtering are not available. APLL-only mode is enabled when the APLL input mux is set to select an input other than the DPLL output (i.e. APLLCR3.APLLMUX=0xx).

APLL-only mode has two usage cases. First, the APLL can be locked to an external crystal as shown in Figure 6 for frequency synthesis applications. Second, the APLL can be locked to any of the four input clock signals, as shown in Figure 7 for frequency conversion applications.

Figure 6 - APLL-Only Mode: Clock Synthesis from a Crystal

Figure 7 - APLL-Only Mode: Frequency Conversion from One of Four Input Clocks

#### 5.2.2 DPLL+APLL Mode

In DPLL+APLL mode, the input block and DPLL are enabled and used. In this mode all input block features are available including activity monitoring, frequency monitoring and automatic reference switching. In addition, all DPLL features are available as well, including bandwidths low enough to filter jitter on the input clock signals. Device power consumption is slightly higher than APLL-only mode.

DPLL+APLL mode is enabled when the APLL input mux is set to select the DPLL output (i.e. APLLCR3.APLLMUX=11x) and the input block and DPLL are enabled (PLLEN.DPLLEN=1).

DPLL+APLL mode includes the following three operating modes:

- Jitter Attenuation mode: The DPLL locks to a jittery input clock signal on IC1, IC2 or IC3 and attenuates (filters) the jitter. The device outputs low-jitter clocks on its OCx outputs.

- Numerically Controlled Oscillator (NCO) mode: The input block and most of the DPLL are shut down, and system software controls the DPLL's output frequency through register writes.

- Spread-Spectrum mode: The input block and most of the DPLL are shut down, and a spread-spectrum

hardware block modulates the DPLL's output frequency at a specified modulation rate over a specified

frequency range. This is typically used for as an EMI reduction strategy.

In DPLL+APLL mode the input block and the DPLL must operate from a master clock signal that is approximately 100MHz, 114.285MHz or 125MHz (see MCR2.MCLK for exact frequency ranges). DPLL+APLL mode has two usage cases. First, the master clock can be a clock signal on the XA pin, optionally doubled by the clock doubler, as shown in Option 1 in Figure 8. Second, the master clock can come from an external crystal, the internal crystal

driver circuit, and the clock doubler as shown in Option 2 in Figure 8. This second use case requires a crystal frequency between 46.5MHz and 60MHz and the clock doubler in order to get a valid master clock frequency.

Note that the clock doubler can be used with an external XO in NCO and spread-spectrum modes, but the clock doubler generally should not be used with an external XO in jitter attenuation mode. See section 5.4.3 for more details.

Figure 8 - DPLL+APLL Mode: Locked to One of Three Inputs, Master Clock from XO or Crystal

# 5.2.3 Evaluation Software for Device Configuration

Microsemi provides evaluation software that gives the user a simple, intuitive graphical user interface in which to generate complete device configurations. Often customers can generate base device configurations with the evaluation software without learning the device register set in detail. This saves time and money during system development. When the device is used in APLL-only mode, the use of the evaluation software is optional, but recommended to minimize engineering effort. When the device is used in DPLL+APLL mode, the use of the evaluation software is required as explained in sections 5.7.1 and 5.6.2.3.

## 5.3 Pin-Controlled Automatic Configuration at Reset

The device configuration is determined at reset (i.e. on the rising edge of RSTN) by the signal levels on five device pins: TEST/GPIO2, AC1/GPIO1, AC0/GPIO0, IF1/MISO and IF0/CSN. For each of these pins, the first name (TEST, AC1, AC0, IF1, IF0) indicates their function when they are sampled by the rising edge of the RSTN pin. The second name refers to their function after reset. The values of these pins are latched into the CFGSR register when RSTN goes high. To ensure the device properly samples the reset values of these pins, the following guidelines should be followed:

- Any pullup or pulldown resistors used to set the value of these pins at reset should be 1kΩ.

- 2. RSTN must be asserted at least as long as specified in section 5.12.

The hardware configuration pins are grouped into three sets:

- 1. TEST Manufacturing test mode

- 2. IF[1:0] Microprocessor interface mode and I<sup>2</sup>C address

- 3. AC[1:0] Auto-configuration from EEPROM

The TEST pin selects manufacturing test modes when TEST=1 (the AC[1:0] pins specify the test mode). For ZL30253, TEST=1 and AC[1:0]=00 configures the part so that production SPI EEPROM programmers can program the internal EEPROM (see section 5.14.2). For more information about auto-configuration from EEPROM see section 5.14.1.

#### 5.3.1 ZL30252—External EEPROM or No EEPROM

For the ZL30252 the IF[1:0] pins specify the processor interface mode and the I<sup>2</sup>C slave address. When IF[1:0]=11 (SPI) two options are available:

If AC[1:0]=00 the device sets up its processor interface as SPI slave through which it can be configured by software running on the SPI master. In this option the device cannot auto-configure from an external EEPROM.

If AC[1:0]=01, 10, or 11 the device first sets up its processor interface as a SPI master. It then auto-configures itself by reading the configuration number specified by AC[1:0] from an external SPI EEPROM connected to its SPI pins. After auto-configuration is complete, the device reconfigures its processor interface to be SPI slave.

These options are summarized in the following table:

| IF1 | IF0 | AC1 | AC0 | Processor Interface                                                 | External EEPROM | Auto Configuration |

|-----|-----|-----|-----|---------------------------------------------------------------------|-----------------|--------------------|

| 0   | 0   | 0   | 0   | I <sup>2</sup> C, slave address 11011 00                            | No              | n/a                |

| 0   | 1   | 0   | 0   | I <sup>2</sup> C, slave address 11011 01                            |                 |                    |

| 1   | 0   | 0   | 0   | I <sup>2</sup> C, slave address 11011 10 No                         |                 | n/a                |

| 1   | 1   | 0   | 0   | SPI Slave                                                           | No              | n/a                |

| 1   | 1   | 0   | 1   | CDI Master to external EEDDOM for                                   | Yes             | Configuration 1    |

| 1   | 1   | 1   | 0   | SPI Master to external EEPROM for auto-configuration then SPI Slave | Yes             | Configuration 2    |

| 1   | 1   | 1   | 1   | auto-configuration then SPI Slave                                   | Yes             | Configuration 3    |

Notes about the device auto-configuring from external EEPROM:

- 1. The device's CSN pin must have a pull-up resistor to VDD to ensure its processor interface is inactive after auto-configuration is complete. The SCLK, MISO and MOSI pins should also have pull-up resistors to VDD to keep them from floating.

- 2. If a processor or similar device will access device registers after the device has auto-configured from external EEPROM, the SPI SCLK, MOSI and MISO wires can be connected directly to the processor, the device and the external EEPROM. The processor and device CSN pins can be wired together also. The EEPROM CSN signal must be controlled by the device's CSN pin during device auto-configuration and then held inactive when the processor accesses device registers.

#### 5.3.2 ZL30253—Internal EEPROM

For the ZL30253 the IF[1:0] pins specify the processor interface mode and the I<sup>2</sup>C slave address.

| IF1 | IF0 | Processor Interface                      |

|-----|-----|------------------------------------------|

| 0   | 0   | I <sup>2</sup> C, slave address 11011 00 |

| 0   | 1   | I <sup>2</sup> C, slave address 11011 01 |

| 1   | 0   | I <sup>2</sup> C, slave address 11011 10 |

| 1   | 1   | SPI Slave                                |

The AC[1:0] pins specify which of four device configurations in the EEPROM to execute after reset.

| AC1                 | AC0                 | Auto Configuration |  |

|---------------------|---------------------|--------------------|--|

| 0                   | 0                   | Configuration 0    |  |

| 0 1 Configuration 1 |                     |                    |  |

| 1                   | 1 0 Configuration 2 |                    |  |

| 1                   | 1                   | Configuration 3    |  |

#### 5.4 Local Oscillator or Crystal

Section 5.2 describes several device configurations that make use of either an external local oscillator (XO or TCXO) or an external crystal. Section 5.4.1 describes how to connect an external oscillator and the required characteristics of the oscillator. Section 5.4.2 describes how to connect an external crystal to the on-chip crystal driver circuit and the required characteristics of the crystal.

#### 5.4.1 External Oscillator

A signal from an external oscillator can be connected to the XA pin (XB must be left unconnected). Table 9 specifies the range of possible frequencies for the XA input. Several vendors including Vectron, Rakon and TXC offer low-cost, low-jitter XOs with output frequencies in this range. In DPLL+APLL jitter attenuation mode the frequency of the external oscillator must be specified in the MCR2.MCLK field. To minimize jitter, the signal must be properly terminated and must have very short trace length. A poorly terminated single-ended signal can greatly increase output jitter, and long single-ended trace lengths are more susceptible to noise. When MCR1.XAB=10, XA is enabled as a single-ended input.

In DPLL+APLL mode, the stability of the DPLL in freerun or digital hold is equivalent to the stability of the external oscillator. While many applications can make use of a simple XO component, some applications may require the stability of a TCXO. Contact Microsemi timing products technical support for recommended oscillator components.

While the stability of the external oscillator can be important, its absolute frequency accuracy is less important because any known frequency inaccuracy of the oscillator can be compensated. When the device is configured for DPLL+APLL mode, the DPLL's DFREQZ parameter can be used to compensate for oscillator frequency error. When the device is configured for APLL-only mode, the APLL's fractional feedback divider value (AFBDIV) can be adjusted by ppb or ppm to compensate for oscillator frequency error.

The jitter on output clock signals depends on the phase noise and frequency of the external oscillator. For the device to operate with the lowest possible output jitter, the external oscillator should have the following characteristics:

- Phase Jitter: less than 0.1ps RMS over the 12kHz to 5MHz integration band

- Frequency: The higher the better, all else being equal

# 5.4.2 External Crystal and On-Chip Driver Circuit

The on-chip crystal driver circuit is designed to work with a <u>fundamental mode, AT-cut</u> crystal resonator. See <u>Table 2</u> for recommended crystal specifications. To enable the crystal driver, set <u>MCR1.XAB=01</u>.

See Figure 9 for the crystal equivalent circuit and the recommended external capacitor connections. To achieve a crystal load ( $C_L$ ) of 10pF, an external 16pF is placed in parallel with the 4pF internal capacitance of the XA pin, and an external 16pF is placed in parallel with the 4pF internal capacitance of the XB pin. The crystal then sees a load of 20pF in series with 20pF, which is 10pF total load. Note that the 16pF capacitance values in Figure 9 include all capacitance on those nodes. If, for example, PCB trace capacitance between crystal pin and IC pin is 2pF then 14pF capacitors should be used to make 16pF total.

The crystal, traces, and two external capacitors should be placed on the board as close as possible to the XA and XB pins to reduce crosstalk of active signals into the oscillator. Also no active signals should be routed under the crystal circuitry.

Note: Crystals have temperature sensitivies that can cause frequency changes in response to ambient temperature changes. In applications where significant temperature changes are expected near the crystal, it is recommended that the crystal be covered with a thermal cap, or an external XO or TCXO should be used instead.

Figure 9 - Crystal Equivalent Circuit / Recommended Crystal Circuit

**Table 2 - Crystal Selection Parameters**

| Parameter                                             | Symbol           | Min.  | Тур. | Max. | Units |    |

|-------------------------------------------------------|------------------|-------|------|------|-------|----|

| Crystal oscillation frequency                         | f <sub>osc</sub> | 25    |      | 60   | MHz   |    |

| Shunt capacitance                                     | Co               |       | 2    | 5    | pF    |    |

| Load capacitance                                      | Load capacitance |       |      | 10   |       | pF |

| Equivalent series resistance f <sub>OSC</sub> < 40MHz |                  | $R_s$ |      |      | 60    | Ω  |

| $(ESR)^2$ $f_{OSC} > 40MHz$                           |                  | $R_S$ |      |      | 50    | Ω  |

| Maximum crystal drive level                           |                  | 100   |      |      | μW    |    |

Note 1: Higher frequencies give lower output jitter, all else being equal.

Note 2: These ESR limits are chosen to constrain crystal drive level to less than  $100\mu W$ . If the crystal can tolerate a drive level greater than  $100\mu W$  then proportionally higher ESR is acceptable.

| Parameter                                    | Symbol    | Min. | Тур. | Max. | Units                   |

|----------------------------------------------|-----------|------|------|------|-------------------------|

| Crystal Frequency Stability vs. Power Supply | $f_{FVD}$ |      | 0.2  | 0.5  | ppm per 10%<br>∆ in VDD |

Any known frequency inaccuracy of the crystal can be compensated in the DPLL or in the APLL. When the device is configured for DPLL+APLL mode, the DPLL's DFREQZ field can be used to compensate for crystal frequency error. When the device is configured for APLL-only mode, the APLL's fractional feedback divider value (AFBDIV) can be adjusted by ppb or ppm to compensate for crystal frequency error.

#### 5.4.3 Clock Doubler

Figure 1 shows an optional clock doubler ("x2" block) following the crystal driver block. The doubler, which is enabled by setting MCR1.DBL=1, can be used to double the frequency of the internal crystal driver circuit or a clock signal on the XA pin. The following table shows scenarios when the clock doubler can be used.

| Device Mode                    | With Crystal       | With XO or Clock Signal |

|--------------------------------|--------------------|-------------------------|

| APLL-Only, Integer Multiply    | Maybe <sup>1</sup> | Maybe <sup>1</sup>      |

| APLL-Only, Fractional Multiply | Yes                | Yes                     |

| DPLL+APLL Jitter Attenuation   | Yes                | Not Recommended         |

| DPLL+APLL NCO                  | Yes                | Yes                     |

| DPLL+APLL Spread-Spectrum      | Yes                | Yes                     |

Note 1: For APLL integer multiplication, use of the doubler is application-dependent. On the positive side, use of the doubler reduces random jitter. On the negative side, the doubler causes a large spur at the XA frequency (but this spur may be outside the band of interest for the application).

# 5.4.4 Ring Oscillator (for System Start-Up)

To ensure that registers can be written immediately after system start-up, in its power-on reset state the device operates its registers and processor interface from an internal ring oscillator.

When operating the device in DPLL+APLL mode, as soon as the external oscillator connected to the XA pin has stabilized and is ready to use, the MCR1.MCSEL bit must be set to source the DPLL master clock from XA. If the ring oscillator causes undesirable spurs it can be disabled (powered down) by setting MCR1.ROSCD=1.

When operating the part in APLL-only mode, a master clock signal on the XA pin is not required, and the ring oscillator is left enabled to provide a clock for the processor interface logic and registers.

# 5.5 Input Signal Format Configuration

Input clocks IC1, IC2 and IC3 are enabled by setting the enable bits in the ICEN register. The power consumed by a differential receiver is shown in Table 7. The electrical specifications for these inputs are listed in Table 10. Each input clock can be configured to accept nearly any differential signal format by using the proper set of external components (see Figure 22). To configure these differential inputs to accept single-ended CMOS signals, connect the single-ended signal to the ICxP pin, and connect the ICxN pin to a capacitor  $(0.1\mu F)$  or  $0.01\mu F$  to VSS. Each ICxP and ICxN pin is internally biased to approximately 1.3V. If an input is not used, both ICxP and ICxN pins can be left floating. Note that the IC3N pin is not present. A differential signal can be connected to IC3P by AC-coupling the POS trace to IC3P and terminating the signal on the driver side of the coupling cap. If not needed as an input clock pin, IC3P can behave as general-purpose I/O pin GPIO3.

# 5.6 Input Block: Input Divider, Monitor and Selector

The input block performs the following functions:

- Frequency division to a frequency suitable for DPLL locking

- Activity monitoring

- Frequency monitoring

- DPLL input clock selection (automatic or manual)

Figure 10 is a block diagram of the input block. This block requires a master clock as described in section 5.2.2.

Figure 10 - Input Block Diagram

#### 5.6.1 Input Clock Inversion and High-Speed Dividers

The input block tolerates a wide range of duty cycles out to a minimum high time or minimum low time of 3ns or 30% of the clock period, whichever is smaller.

Any frequency in the 1kHz to 250MHz range can be accepted by the input block. Important notes about the input block:

- ICxCR1.POL specifies the edge to which the DPLL will lock (by default, the rising edge).

- ICxCR1.HSDIV must be set correctly to reduce the clock frequency below 250MHz.

- In DPLL+APLL mode, the frequencies of all enabled ICx input clocks must divide by integers to a common DPLL phase-frequency detector (PFD) frequency ≥ 1kHz. In addition, the common PFD frequency must be ≥ 20 times the DPLL bandwidth.

# 5.6.2 Input Clock Monitoring

Each ICx input clock is continuously monitored for activity and frequency accuracy.

The activity monitor counts the number of input clock cycles that occur during a configurable interval. This provides the fastest detection when the input clock is stopped or far off frequency. Register bit ICxSR.ACVAL indicates the real-time status of this monitor. The ACVAL bit stays low when the input clock is not toggling or its frequency is grossly too high; ACVAL flickers (i.e. rapidly changes states) when the input clock is toggling but its frequency is grossly too low.

Frequency monitoring is handled by a percent frequency monitor (1% to 20% in 1% steps). Register bit ICxSR.PCVAL indicates the real-time status of the percent monitor.

Any input clock that fails activity monitoring or frequency monitoring is declared invalid. The valid/invalid state of each input clock is reported in the corresponding real-time status bit in the VALSR registers. When the valid/invalid state of a clock changes, the corresponding latched status bit is set in the VALSR registers. Input clocks manually marked invalid in the DPLL's VALCR1 register cannot be automatically selected as the reference for the DPLL.

The activity monitor and frequency monitor can be enabled and disabled using the ACEN and PCEN bits, respectively in the MONxCR2 register.

In addition to the monitors in the input block, the DPLL can also invalidate an input. If the input is the DPLL's selected reference and the DPLL cannot lock within the time specified by the PHLKTO register, the DPLL invalidates the input by setting the ICxSR.LKTO bit.

**Note 1:** For rev A parts only, when ACEN=PCEN=PPEN=0 for an input (which is the power-on default state of the device), that input is declared <u>valid</u> by the input monitoring logic, even when the input receiver is disabled by setting ICEN.ICxEN=0. To avoid this, set at least one of the ACEN and PCEN bits to 1.

**Note 2:** The percent monitor cannot be used with a 1kHz input clock and has a narrower range of settings for input frequencies below 2kHz. See the evaluation software for the exact range of settings available for a particular device configuration.

## 5.6.2.1 External Monitoring

Some clock signals come from external components that can monitor the quality of a clock signal or the quality of a signal from which the clock signal is derived. One example is a BITS receiver in telecom equipment. This component receives a DS1, E1 or 2048kHz synchronization signal and recovers a clock from that signal. The BITS receiver monitors the incoming signal and can declare loss of signal (LOS), loss of frame alignment (LOF) and other defects in the incoming signal. Another example is a Synchronous Ethernet PHY, which receives an Ethernet signal and recovers a clock from that signal. This PHY can declare loss of lock, loss of codeword alignment and other defects.

When a neighboring component can detect that the incoming signal or the clock recovered from the signal is somehow out of specification, a loss-of-signal indication from that component can be connected to a GPIO pin on the device to instantly invalidate the input clock. Any GPIO pin can be used as a loss-of-signal indicator for any of the IC1, IC2 or IC3 input clocks. ICxSR.LOS indicates the real-time LOS status from the GPIO pin.

**Example**: Configure GPIO1 to be the active-low LOS signal for IC1:

GPIOCR1.GPIO1C=0001 (Configure GPIO1 to be an input with inversion)

MON1CR2.LOSSS=010 (Configure the IC1 monitor's LOS source to be GPIO1)

## 5.6.2.2 Monitor Priority and Validation Timer

All enabled input monitors must declare an input valid for a configurable duration (which can be zero) before the input clock is validated and considered eligible for selection as the DPLL's selected reference. The monitors have a priority hierarchy in which an invalid declaration by a higher-priority monitor forces an invalid declaration in all

lower-priority monitors. When a valid higher-priority monitor declares the input valid, the next lower priority monitor can then initiate its validation process. The monitor hierarchy is as follows:

- Input LOS from a GPIO pin forces all other monitors (activity and frequency) to declare the input invalid.

- When the activity monitor declares invalid, it forces the frequency monitor to declare invalid.

When a monitor is not enabled, it continually declares the input clock valid.

After all monitors declare an input clock valid (ICxSR.VAL=1) the validation timer requires all the monitors to continue to indicate the clock is valid for a configurable validation time before the input is declared valid for use as a DPLL input (ICxSR.VALT=1).

# **5.6.2.3 Input Monitor Configuration**

The device's input monitors are very sophisticated, but the configuration registers for these monitors are, generally speaking, low-level coefficients rather than user concepts such as percentage frequency error. As a result most input monitor registers are not documented in this data sheet. Instead, Microsemi provides evaluation software that gives the user a simple, intuitive graphical user interface in which to generate complete device configurations, including all aspects of input monitor behavior. Configuration files from the evaluation software can be stored in device EEPROM to allow the device to self-configure at reset. Alternately, system software can perform the register writes listed in the configuration files as needed to configure/reconfigure the device.

# 5.6.3 Input Clock Priority, Selection and Switching for the DPLL

# **5.6.3.1 Priority Configuration**

During normal operation, the selected reference for the DPLL is chosen automatically based on the priority rankings assigned to the input clocks in the input priority registers (IPR1 and IPR2). The default input clock priorities are shown in Table 3.

Any unused input clock should be given the priority value 0, which disables the clock and marks it as unavailable for selection. Priority 1 is highest.

**Table 3 - Default Input Clock Priorities**

| INPUT CLOCK | DPLL<br>DEFAULT<br>PRIORITY |

|-------------|-----------------------------|

| IC1         | 1                           |

| IC2         | 2                           |

| IC3         | 3                           |

# 5.6.3.2 Automatic Selection

When ICSCR1.EXTSW=0, automatic input clock reference selection is used for the DPLL. The input reference selection algorithm chooses the <a href="highest-priority valid input clock">highest-priority valid input clock</a> to be the selected reference. The real-time valid/invalid state of each input clock is maintained in the VALSR registers (see section 5.6.2). The priority of each input clock is set as described in section 5.6.3.1. To select the DPLL input clock based on these criteria, the selection algorithm maintains a priority table of valid inputs. The top entry in this priority table and the selected reference are indicated in the PTAB1 register. The second- and third-priority inputs are indicated in the PTAB2 register.

If two or more input clocks are given the same priority number then those inputs are prioritized among themselves using a fixed circular list. If one equal-priority clock is the selected reference but becomes invalid then the next equal-priority clock in the list becomes the selected reference. If an equal-priority clock that is not the selected reference becomes invalid, it is simply skipped over in the circular list. The selection among equal-priority inputs is inherently nonrevertive, and revertive switching mode (see next paragraph) has no effect in the case where multiple equal-priority inputs have the highest priority.

An important input to the selection algorithm is the REVERT bit in the ICSCR1 register. In revertive mode (REVERT=1), if an input clock with a higher priority than the selected reference becomes valid, the higher priority reference immediately becomes the selected reference. In nonrevertive mode (REVERT=0), the higher priority reference does not immediately become the selected reference but does become the highest priority reference in the priority table (PTAB1.REF1). (The selection algorithm always switches to the highest-priority valid input when the selected reference goes invalid, regardless of the state of the REVERT bit.) For many applications, nonrevertive mode is preferred because it minimizes disturbances on the output clocks due to reference switching.

In nonrevertive mode, planned switchover to a newly-valid higher priority input clock can be done manually under software control. The validation of the new higher priority clock sets the corresponding latched status bit in the VALSR registers, which can drive an interrupt request if needed. System software can then respond to this change of state by briefly enabling revertive mode (toggling REVERT high then back low) to force the switchover to the higher priority clock.

#### 5.6.3.3 Manual Selection

The bits of the VALCR1 register can be used to perform manual selection of an input clock. When all input clocks have non-zero priorities in the IPR registers, an input clock can be manually selected by setting the VALCR1 bit for that input clock to 1 and the VALCR1 bits for the other input clocks to 0.

# 5.6.3.4 External Reference Switching Mode

In this mode a GPIO pin controls reference switching between two input clocks. This mode is enabled by setting the ICSCR1.EXTSW=1. In this mode, if the GPIO pin is high, the DPLL is forced to lock to input IC1 (if the priority of IC1 is nonzero in IPR1) or IC3 (if the priority of IC1 is zero) whether or not the selected input has a valid reference signal. If the GPIO pin is low the DPLL is forced to lock to input IC2 whether or not IC2 has a valid reference signal. The GPIO pin is selected by MCR2.EXTSS.

In external reference switching mode the input selector logic behaves as a simple 2:1 mux, and the DPLL is forced to try to lock to the selected reference whether it is valid or not. This mode controls the PTAB1.SELREF field directly and, therefore, is not affected by the state of the ICSCR1.REVERT bit. During external reference switching mode, only PTAB1.SELREF is affected; the PTAB1.REF1 field continues to indicate the highest-priority valid input chosen by the automatic selection logic. The priorities of IC1, IC2 and IC3 in the IPR registers must be non-zero for proper behavior in external reference switching mode.

## 5.7 DPLL Architecture and Configuration

Figure 11 - DPLL Block Diagram

Digital PLLs have two key benefits: (1) stable, repeatable performance that is insensitive to process variations, temperature, and voltage; and (2) flexible behavior that is easily configured and reprogrammed. DPLLs use a digitally controlled oscillator (DCO) to generate the DPLL output clock. The DPLL output clock is then provided to an APLL for clock multiplication/frequency conversion.

The DPLL in the device is configurable for many PLL parameters including bandwidth, input frequency, pull-in/hold-in range, input-to-output phase offset, and more. No knowledge of loop equations or gain parameters is required to configure and operate the device. No external components are required for the DPLL except a local oscillator connected to the XA pin to provide the DPLL's master clock (see section 5.2.2).

# 5.7.1 **DPLL Configuration**

The device's DPLL is very sophisticated, but the configuration registers for the DPLL are, generally speaking, very low-level coefficients rather than user concepts such as bandwidth and pull-in range. As a result most DPLL registers are not documented in this data sheet. Instead, Microsemi provides evaluation software that gives the user a simple, intuitive graphical user interface in which to generate complete device configurations, including all aspects of DPLL behavior. Configuration files from the evaluation software can be stored in device EEPROM to allow the device to self-configure at reset. Alternately, system software can perform the register writes listed in the configuration files as needed to configure/reconfigure the device. The most frequently used DPLL status register fields and real-time control register fields are documented in section 6.3.6 and discussed in the DPLL sections below.

#### 5.7.2 DPLL States

**Tracking (Locked and Unlocked).** When a valid input clock is available, the DPLL is in the tracking state (DSRR1.TRK=1) and is either locked to an input clock (DSRR1.LOL=0) or unlocked (DSRR1.LOL=1).

**Freerun/Digital-Hold.** When all input clocks become invalid, the DPLL enters the freerun/digital-hold state (DSRR1. TRK=0) in which it operates open-loop. In this mode the DPLL can be in freeun (DSRR1.HO=0) in which its output frequency has the same fractional frequency offset as the master clock signal. Or the DPLL can be in digital hold (DSRR1.HO=1) in which the output frequency has the same fractional frequency offset it had previously when the DPLL was locked to an input clock. The DPLL can automatically transition from the freerun/digital-hold state to the tracking state when an input clock is declared valid. The DPLLCR1.HOMODE field controls DPLL freerun/digital-hold behavior.

System software can manually force the DPLL into the freerun/digital-hold state as needed using the DPLLCR1.MODE field.

# 5.7.3 **DPLL Capabilities**

Bandwidth. The DPLL can be configured for any bandwidth from 14Hz to 500Hz...

**Pull-In/Hold-In Range.** The DPLL tracking range is configurable from ±1ppm to ±1000ppm. The DPLL reports when it has reached the limit of the range in the DSRR2.FLIM register bit. The DPLL's hold-in range is the same as its tracking range. The DPLL's pull-in range should be considered to be half the size of the tracking range for reasonable pull-in time. For example, when tracking range is ±1000ppm, pull-in range should be considered to be ±500ppm.

**Programmable Lock Criteria.** The DPLL has configurable criteria for defining when it declares lock. In addition to phase, the DPLL can also be configured to declare loss of lock when its fractional frequency offset exceeds the pull-in/hold-in limit.

**Programmable Phase Lock Timeout.** When the DPLL fails to lock to the selected input clock within the timeout duration specified by the PHLKTO register, the input is declared invalid by the input block, which sets the ICxSR.LKTO bit.

**Frequency and Phase Reporting.** The DPLL reports in real-time its frequency (i.e. fractional frequency offet in ppb/ppm vs. its nominal frequency) and its phase vs. the input clock signal. DPLL frequency resolution is better than 0.005ppb. DPLL frequency offset is reported in the DFREQ registers. DPLL phase is reported in the DPHASE registers.

**Numerically Controlled Oscillator (NCO) Mode.** In this mode most of the DPLL is shut down and system software controls the DPLL's output frequency using the 40-bit FREQZ field in the the DFREQZ registers. The resolution of frequency control is better than 0.01ppb. See section 5.7.7 for more details.

**Spread-Spectrum Modulation Mode.** For EMI-sensitive applications such as PCI Express, the device can perform spread spectrum modulation (SSM). In SSM the frequency of the output clock is continually varied over a narrow frequency range to spread the energy of the signal and thereby reduce EMI. See section 5.7.8 for more details.

#### 5.7.4 Input Wander and Jitter Tolerance

Wander is tolerated up to the point where wander causes an apparent long-term frequency offset larger than the frequency threshold set in the input monitor. In such a situation the input clock would be declared invalid. Jitter can be tolerated up to the point of eye closure. The high-jitter input clock signal should be divided down to a lower frequency by the DPLL's input divider for high jitter tolerance.

#### 5.7.5 Jitter and Wander Transfer

The transfer of jitter and wander from the selected reference to the output clocks has a programmable transfer function that is determined by the DPLL bandwidth. The 3dB corner frequency of the jitter transfer function can be set to any value from 14Hz to 500Hz.

During locked mode, the transfer of wander from the local oscillator clock (connected to the XA pin) to the output clocks is not significant as long as the DPLL bandwidth is set high enough to allow the DPLL to quickly compensate for oscillator frequency changes. During freerun/digital-hold, local oscillator wander has a much more significant effect. See section 5.4.1.

# 5.7.6 Output Jitter and Wander

Several factors contribute to jitter and wander on the output clocks, including: