Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## **Ten LVCMOS Output Low Additive Jitter Fanout Buffer**

#### **Features**

- 3 to 1 input Multiplexer: Two inputs accept any differential (LVPECL, HCSL, LVDS, SSTL, CML, LVCMOS) or a single ended signal and the third input accepts a crystal or a single ended signal

- Ten 1.5V/1.8V/2.5V/3.3V LVCMOS outputs

- Supports frequencies from 0 to 250MHz

- Ultra-low system level additive jitter: 17fs (12kHz to 20MHz)

- Ultra-low noise floor of -170dBc/Hz

- Supports crystals from 8MHz to 160MHz

- Supports 2.5V or 3.3V power supplies

- Output to output skew of 30ps (typical)

- · Input to output delay of 2ns (typical)

- SPI or Hardware control

#### **Ordering Information**

ZL40240LDG1 32 Pin QFN Trays ZL40240LDF1 32 pin QFN Tape and Reel

> Package size: 5 x 5 mm -40°C to +85°C

#### **Applications**

- General purpose clock distribution

- Low jitter clock trees

- Logic translation

- Clock and data signal restoration

- Wired and Wireless communications

- High performance microprocessor clock distribution

- Medical Imaging

- Test equipment

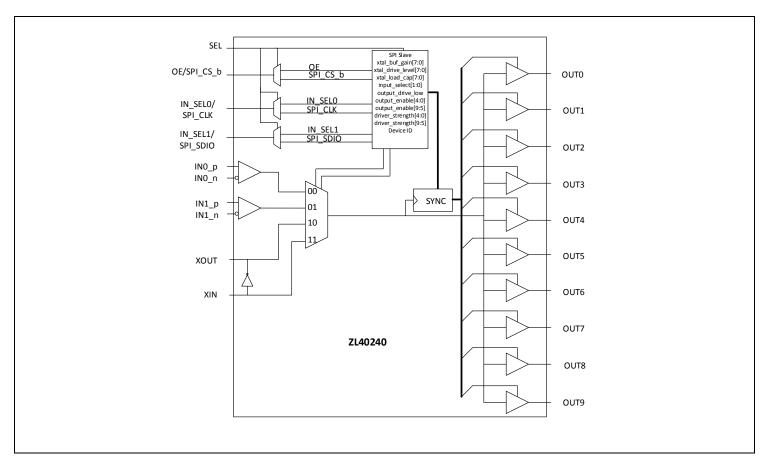

Figure 1. Functional Block Diagram

# **Table of Contents**

| Features                                 |    |

|------------------------------------------|----|

| Table of Contents                        |    |

| Pin Diagram                              |    |

| Pin Descriptions                         |    |

| Functional Description                   |    |

| Clock Inputs                             |    |

| Clock Outputs                            | 12 |

| Crystal Oscillator Input                 | 12 |

| Termination of unused inputs and outputs |    |

| Power Consumption                        | 15 |

| Power Supply Filtering                   | 17 |

| Device Control                           | 17 |

| Register Map                             |    |

| AC and DC Electrical Characteristics     |    |

| Absolute Maximum Ratings                 | 26 |

| Recommended Operating Conditions         |    |

| Package Outline                          |    |

## **List of Figures**

| Figure 1.  | Functional Block Diagram                                               | 1  |

|------------|------------------------------------------------------------------------|----|

| Figure 2.  | Pin Diagram                                                            | 5  |

| Figure 3.  | Input driven by a single ended output                                  | 9  |

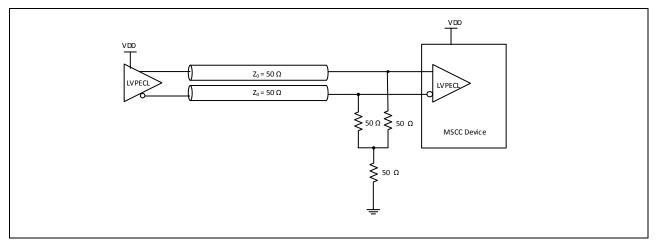

| Figure 4.  | Input driven by DC coupled LVPEVCL output                              | 9  |

| Figure 5.  | Input driven by DC coupled LVPEVCL output (alternative termination)    | 10 |

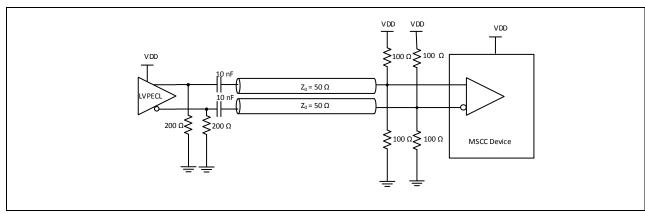

| Figure 6.  | Input driven by AC coupled LVPECL output                               | 10 |

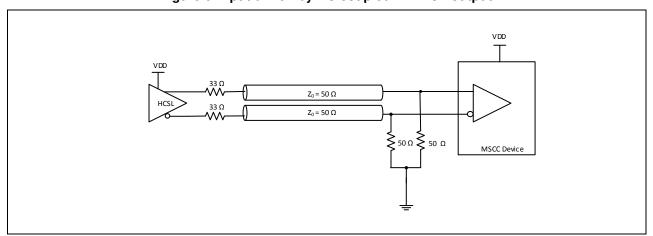

| Figure 7.  | Input driven by HCSL output                                            | 10 |

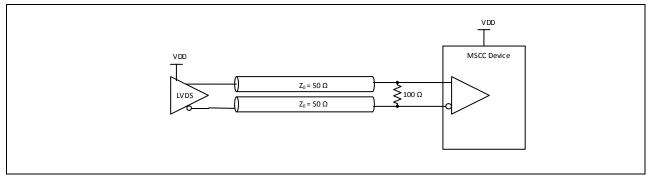

| Figure 8.  | Input driven by LVDS output                                            | 11 |

| Figure 9.  | Input driven by AC coupled LVDS                                        | 11 |

| Figure 10. | Input driven by an SSTL output                                         | 11 |

| Figure 11. | Termination for LVCMOS outputs                                         | 12 |

| Figure 12. | Crystal Oscillator Circuit in SPI Controlled Mode                      | 12 |

| Figure 13. | Crystal Oscillator Circuit in Hardware Controlled Mode                 | 13 |

| Figure 14. | Phase Noise Plot with 25MHz Crystal                                    |    |

| Figure 15. | Phase Noise Plot with 125 MHz Crystal                                  | 14 |

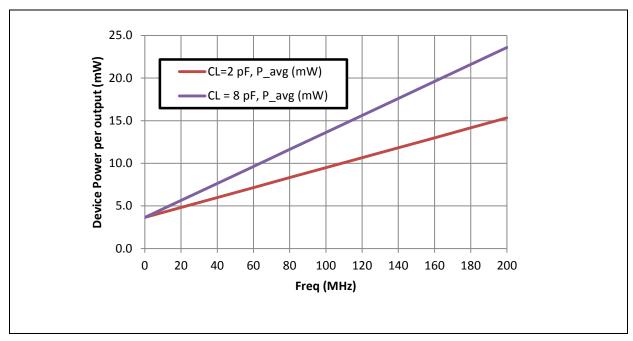

| Figure 16. | Device power consumption per output for $V_{DD} = V_{DDO} = 3.465V$    | 15 |

| Figure 17. | Device power consumption per output for $V_{DD} = V_{DDO} = 2.625V$    | 16 |

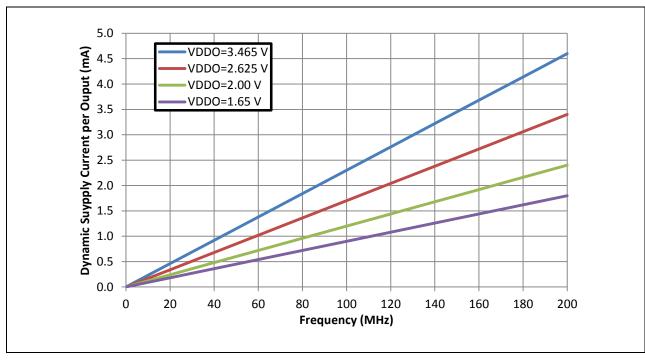

| Figure 18. | Dynamic supply current per output for different output supply voltages | 16 |

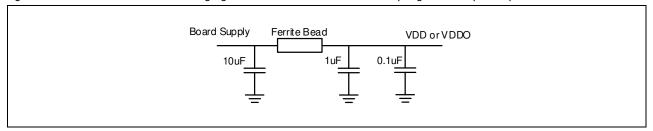

| Figure 19. | Power Supply Filtering                                                 |    |

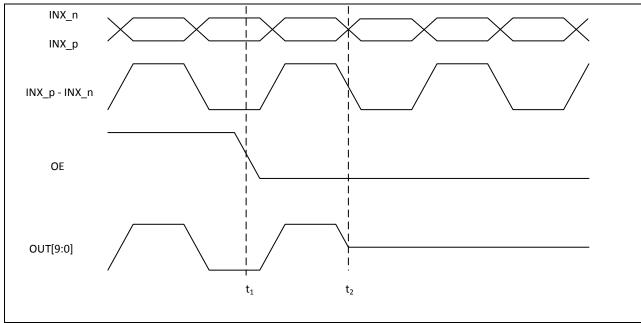

| Figure 20. | OE Output Disable                                                      | 17 |

| Figure 21. | OE Output Enable                                                       |    |

| Figure 22. | SPI slave interface                                                    | 18 |

| Figure 23. | Serial Peripheral Interface Functional Waveform – LSB First Mode       | 19 |

| Figure 24. | Serial Peripheral Interface Functional Waveform – MSB First Mode       | 19 |

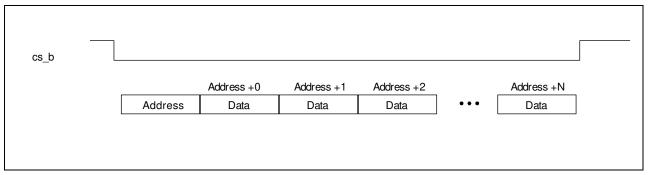

| Figure 25. | Example of the Burst Mode Operation                                    | 20 |

| Figure 26. | SPI (Serial Peripheral Interface) Timing - LSB First Mode              | 31 |

| Figure 27. | SPI (Serial Peripheral Interface) Timing - MSB First Mode              | 31 |

#### **List of Tables**

| Table 1 · Pin Descriptions                                                           | <i>6</i> |

|--------------------------------------------------------------------------------------|----------|

| Table 1 · Pin Descriptions<br>Table 2 · Register Map                                 | 21       |

| Table 3 · Absolute Maximum Ratings*                                                  |          |

| Table 4 · Recommended Operating Conditions*                                          |          |

| Table 5 · Current consumption                                                        |          |

| Table 6 · Input Characteristics*                                                     |          |

| Table 7 · Crystal Oscillator Characteristics*                                        |          |

| Table 8 · LVCMOS Output Characteristics*                                             |          |

| Table 9 · LVCMOS Output Additive Jitter and Phase Noise*                             |          |

| Table 10 · LVCMOS Output Jitter Phase Noise with 25MHz XTAL*                         |          |

| Table 11 · LVCMOS Output Jitter Phase Noise with 125MHz XTAL*                        |          |

| Table 12 · AC Electrical Characteristics* - SPI (Serial Peripheral Interface) Timing |          |

| Table 13 · 5x5mm QFN Package Thermal Properties                                      |          |

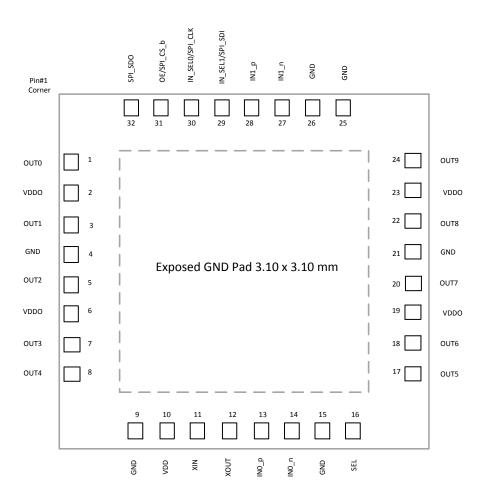

## **Pin Diagram**

The device is packaged in a 5x5mm 32-pin QFN.

Figure 2. Pin Diagram

### **Pin Descriptions**

All device inputs and outputs are LVPECL unless described otherwise. The I/O column uses the following symbols: I  $-\text{ input, } I_{PU}-\text{input with } 300 k\Omega \text{ internal pull-up resistor, } I_{PD}-\text{input with } 300 k\Omega \text{ internal pull-down resistor, } I_{APU}-\text{input with } 300 k\Omega \text{ internal pull-down resistor, } I_{APU}-\text{input with } 300 k\Omega \text{ internal pull-down resistor, } I_{APU}-\text{input with } 300 k\Omega \text{ internal pull-down resistor, } I_{APU}-\text{input with } 300 k\Omega \text{ internal pull-down resistor, } I_{APU}-\text{input with } 300 k\Omega \text{ internal pull-down resistor, } I_{APU}-\text{input with } 300 k\Omega \text{ internal pull-down resistor, } I_{APU}-\text{input with } 300 k\Omega \text{ internal pull-down resistor, } I_{APU}-\text{input with } 300 k\Omega \text{ internal pull-down resistor, } I_{APU}-\text{input with } 300 k\Omega \text{ internal pull-down resistor, } I_{APU}-\text{input with } 300 k\Omega \text{ internal pull-down resistor, } I_{APU}-\text{input with } 300 k\Omega \text{ internal pull-down resistor, } I_{APU}-\text{input with } 300 k\Omega \text{ internal pull-down resistor, } I_{APU}-\text{input with } 300 k\Omega \text{ internal pull-down resistor, } I_{APU}-\text{input with } 300 k\Omega \text{ internal pull-down resistor, } I_{APU}-\text{input with } 300 k\Omega \text{ internal pull-down resistor, } I_{APU}-\text{input with } 300 k\Omega \text{ internal pull-down resistor, } I_{APU}-\text{input with } 300 k\Omega \text{ internal pull-down resistor, } I_{APU}-\text{input with } 300 k\Omega \text{ internal pull-down resistor, } I_{APU}-\text{input with } 300 k\Omega \text{ internal pull-down resistor, } I_{APU}-\text{input with } 300 k\Omega \text{ internal pull-down resistor, } I_{APU}-\text{input with } 300 k\Omega \text{ internal pull-down resistor, } I_{APU}-\text{input with } 300 k\Omega \text{ internal pull-down resistor, } I_{APU}-\text{input with } 300 k\Omega \text{ internal pull-down resistor, } I_{APU}-\text{input with } 300 k\Omega \text{ internal pull-down resistor, } I_{APU}-\text{input with } 300 k\Omega \text{ internal pull-down resistor, } I_{APU}-\text{input with } 300 k\Omega \text{ internal pull-down resistor, } I_{APU}-\text{input with } 300 k\Omega \text{ internal pull-down resistor, } I_{APU}-\text{input with } 300 k\Omega \text{ internal pull-down resistor, } I_{APU}-\text{input with } 300 k\Omega \text{ internal pull-down resistor, } I_{APU}-\text{input with } 100 k\Omega \text{ internal pull-down$ with  $30k\Omega$  internal pull-up resistor,  $I_{APD}$  - input with  $30k\Omega$  internal pull-down resistor,  $I_{APU/APD}$  - input biased at VDD/2 with  $60k\Omega$  internal pull-up and  $60k\Omega$  pull-down resistors, O – output, I/O – Input/Output pin, P – power supply pin.

|                                                     | Table 1 · Pin Descriptions                                                   |                                                                         |                                                          |                                                      |                                                                                                                                                                                                                                                                       |  |

|-----------------------------------------------------|------------------------------------------------------------------------------|-------------------------------------------------------------------------|----------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| #                                                   | Name                                                                         | I/O                                                                     |                                                          |                                                      | Description                                                                                                                                                                                                                                                           |  |

| Input Refe                                          | nput Reference                                                               |                                                                         |                                                          |                                                      |                                                                                                                                                                                                                                                                       |  |

| 13<br>14<br>28<br>27                                | IN0_p<br>IN0_n<br>IN1_p<br>IN1_n                                             | I <sub>APD</sub> I <sub>APU/APD</sub> I <sub>APD</sub> I <sub>APD</sub> | Input frequence Non invertir Inverting input to keep inv | ency range  ng inputs (_  puts (_n) ar  rerting inpu | ingle Ended References 0 and 1 0Hz to 250MHz. p) are pulled down with internal $30k\Omega$ pull-down resistors. The biased at VDD/2 with $60k\Omega$ pull-up and pull-down resistors to voltages at VDD/2 when inverting inputs are left floating e ended reference). |  |

| Output Cl                                           | ocks                                                                         |                                                                         |                                                          |                                                      |                                                                                                                                                                                                                                                                       |  |

| 1<br>3<br>5<br>7<br>8<br>17<br>18<br>20<br>22<br>24 | OUT0<br>OUT1<br>OUT2<br>OUT3<br>OUT4<br>OUT5<br>OUT6<br>OUT7<br>OUT8<br>OUT9 | 0                                                                       |                                                          |                                                      | eter LVCMOS Outputs 0 to 9  OHz to 250MHz                                                                                                                                                                                                                             |  |

| Control                                             |                                                                              |                                                                         |                                                          |                                                      |                                                                                                                                                                                                                                                                       |  |

| 30                                                  | IN_SEL0/SPI_CLK                                                              | I <sub>PD</sub><br>or<br>I <sub>PU</sub>                                | Select 0 ha                                              | rdware cont<br>pin is high                           | for Serial Interface. When SEL pin is low this pin is Input trol input pin and it is pulled-low with 300 $k\Omega$ resistor. this pin provides clock for serial micro-port interface and it is resistor.                                                              |  |

|                                                     |                                                                              |                                                                         | IN_SEL1                                                  | IN_SEL0                                              | OUTN                                                                                                                                                                                                                                                                  |  |

|                                                     |                                                                              |                                                                         | 0                                                        | 0                                                    | Input 0 (IN0)                                                                                                                                                                                                                                                         |  |

|                                                     |                                                                              |                                                                         | 0                                                        | 1                                                    | Input 1 (IN1)                                                                                                                                                                                                                                                         |  |

|                                                     |                                                                              |                                                                         | 1                                                        | 0                                                    | Crystal Oscillator or overdrive                                                                                                                                                                                                                                       |  |

|                                                     |                                                                              |                                                                         | 1                                                        | 1                                                    | Crystal Bypass                                                                                                                                                                                                                                                        |  |

| 29           | IN_SEL1/SPI_SDI         | I <sub>PD</sub><br>or<br>I <sub>PU</sub> | Input Select 1/ Serial Interface Input. When SEL pin is low this pin is Input Select 1 hardware control pin and it is pulled down with 300 k $\Omega$ resistor. When SEL pin is high this pin is serial interface input stream and it is pulled-up with 300 k $\Omega$ resistor The serial data stream holds the access command, the address and the write data bits.  Note: this input has low threshold voltage ( $V_{IH}$ = 1.2V) so it can be driven by low output voltage device from 1.5V or higher up to VDD |

|--------------|-------------------------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32           | SPI_SDO                 | I/O                                      | Serial Interface Output. Serial interface output stream. As an output the serial stream holds the read data bits.                                                                                                                                                                                                                                                                                                                                                                                                   |

| 31           | OE/SPI_CS_b             | I <sub>PD</sub><br>or<br>I <sub>PU</sub> | Output Enable/Chip Select for Serial Interface. When SEL pin is low this pin is Output Enable hardware control input and it is pulled-down with 300 k $\Omega$ resistor. When SEL is high this pin is serial interface chip select and it is pulled-up with 300 k $\Omega$ resistorthis is an active low signal.                                                                                                                                                                                                    |

| Crystal O    | scillator               |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 11           | XIN                     | I                                        | Crystal Oscillator Input or crystal bypass mode or crystal overdrive mode                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 12           | XOUT                    | 0                                        | Crystal Oscillator Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Hardware     | e/SPI Control selection | n                                        | <u>I</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 16           | SEL                     | I <sub>PD</sub>                          | Select control.  When this pin is low, the device is controlled via hardware pins, IN_SEL0/1 and OE.  When this pin is high, the device is controlled via SPI port.  Any change of SEL pin value requires power cycle. Hence, SEL pin cannot be changed on the fly.                                                                                                                                                                                                                                                 |

| Power an     | d Ground                |                                          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 10           | VDD                     | Р                                        | <b>Positive Supply Voltage.</b> Connect to 3.3V or 2.5V supply. VDD voltage must be higher or equal to VDDO.                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2<br>6<br>19 | VDDO                    | Р                                        | Positive Supply Voltage for LVCMOS Outputs Connect 3.3V, 2.5V, 1.8V or 1.5V power supply                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 23                             |     |   |                           |

|--------------------------------|-----|---|---------------------------|

| 4<br>9<br>15<br>21<br>26<br>25 | GND | Р | Ground Connect to ground  |

| E-Pad                          | GND | Р | Ground. Connect to ground |

#### **Functional Description**

The ZL40240 is a programmable or hardware pin controlled low additive jitter, low power 3 x 10 LVCMOS fanout buffer.

Two inputs can accept signal in differential (LVPECL, SSTL, LVDS, HSTL, CML) or single ended (LVPECL or LVCMOS) format and the third input can accept a single ended signal or it can be used to build a crystal oscillator by connecting an external crystal resonator between its XIN and XOUT pins. All the other components for building crystal oscillator are built in device such as load capacitance, series and shunt resistors.

The ZL40240 has ten LVCMOS outputs which can be powered from 3.3V, 2.5V, 1.8V or 1.5V supply. Each output can be independently enabled/disabled via SPI bus. In addition, the strength of each output can be programmed.

The device operates from 2.5V+/-5% or 3.3V+/-5% supply. Its operation is guaranteed over the industrial temperature range  $-40^{\circ}$ C to  $+85^{\circ}$ C.

#### **Clock Inputs**

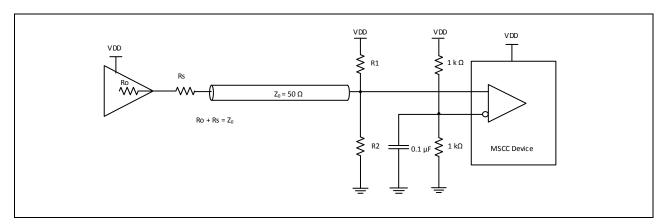

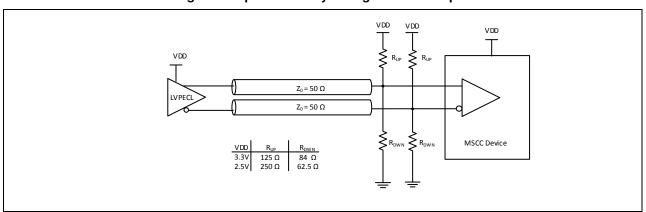

The following blocks diagram shows how to terminate different signals fed to the ZL40240 inputs.

Figure 3 shows how to terminate a single ended output such as LVCMOS. Ideally, resistors R1 and R2 should be  $100\Omega$  each so that the transmission line is terminated with matched impedance ( $50\Omega$ ). However, if the driving strength of the output driver is not sufficient resistor values should be increased

Figure 3. Input driven by a single ended output

Figure 4. Input driven by DC coupled LVPEVCL output

Figure 5. Input driven by DC coupled LVPEVCL output (alternative termination)

Figure 6. Input driven by AC coupled LVPECL output

Figure 7. Input driven by HCSL output

Figure 8. Input driven by LVDS output

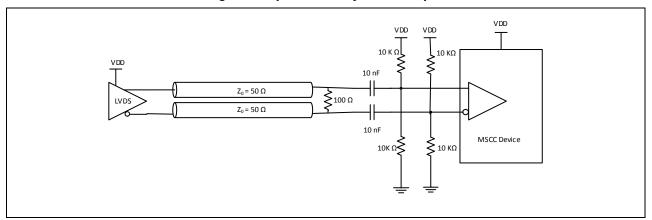

Figure 9. Input driven by AC coupled LVDS

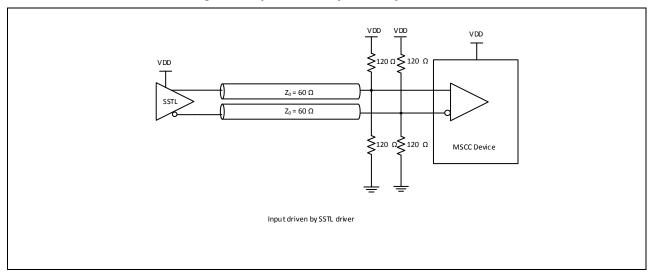

Figure 10. Input driven by an SSTL output

#### **Clock Outputs**

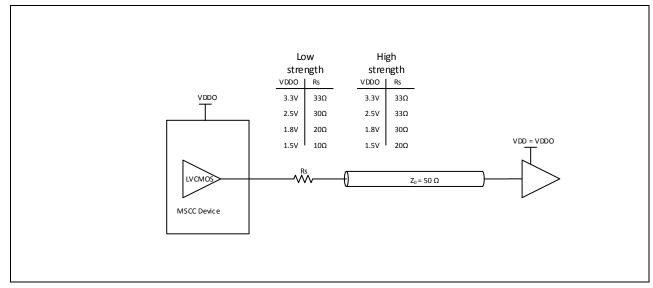

LVCMOS outputs require only series termination resistor whose value is depending on LVCMOS output voltage as shown in Figure 11. The recommended series termination depends on programmed strength of the driver (low or high) and on the output driver supply voltage.

Figure 11. Termination for LVCMOS outputs

#### **Crystal Oscillator Input**

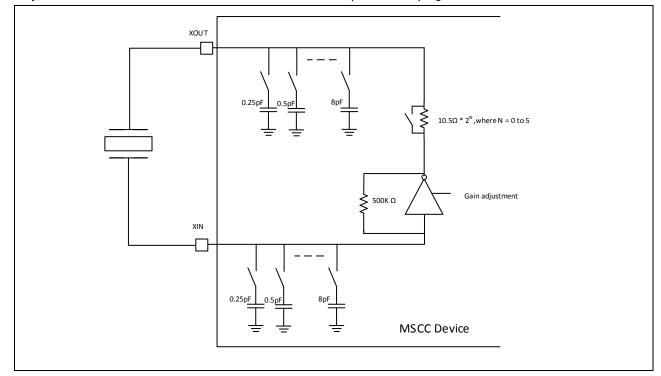

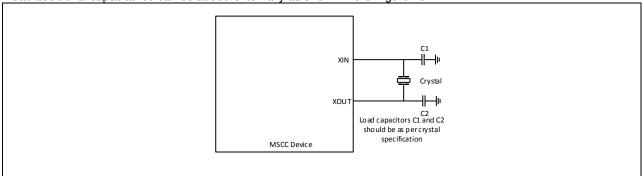

The crystal oscillator circuit can work with crystal resonators from 8MHz to 160MHz. As can be seen in the following figure only crystal resonator is required and all the other components are built-in the device. To be able support crystal resonators with different characteristics all internal components are programmable in SPI Controlled mode.

Figure 12. Crystal Oscillator Circuit in SPI Controlled Mode

Load capacitors can be programmed from 0 to 21.75 pF with resolution of 0.25pF which not only meets load requirement for most crystal resonator but also allows for fine tuning of the crystal resonator frequency. The amplifier gain can be adjusted in eight steps and the series resistor in six steps. Shunt resistor has fixed value of 500K $\Omega$ .

In Hardware Controlled mode the capacitive load is set at 8pF and cannot be changed. For Crystal requiring higher load additional capacitance can be added externally as shown in the Figure 13.

Figure 13. Crystal Oscillator Circuit in Hardware Controlled Mode

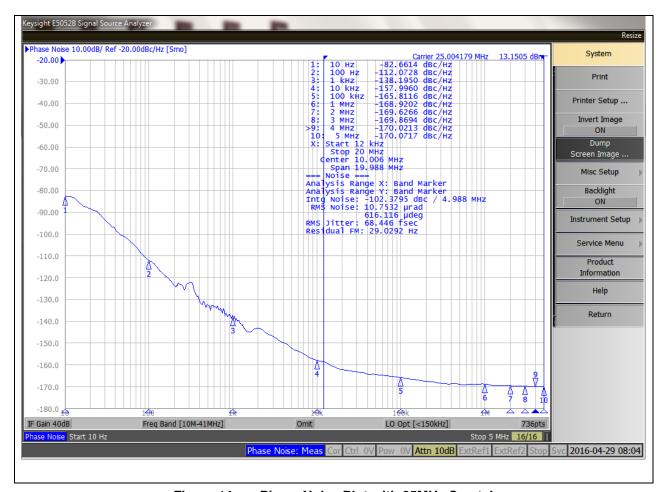

The phase noise plot for 25MHz crystal is shown in Figure 14. The phase noise floor of the device is below -170dBc/Hz as can be seen on the figure.

Figure 14. Phase Noise Plot with 25MHz Crystal

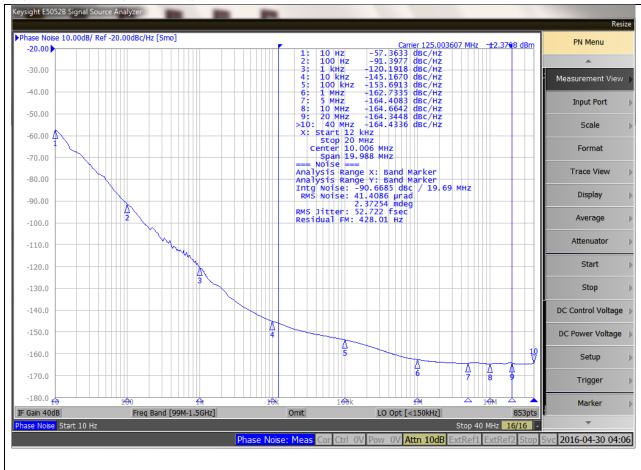

Figure 15 shows the phase noise plot with 125MHz crystal.

Figure 15. Phase Noise Plot with 125 MHz Crystal

#### Termination of unused inputs and outputs

Unused inputs can be left unconnected or alternatively IN $\_0/1$  can be pulled-down by 1K $\Omega$  resistor. Unused outputs should be left unconnected.

#### **Power Consumption**

The total device power consumption can be calculated as:

$$P_T = P_S + P_{XTAL} + P_C + P_D$$

Where

$$P_S = V_{DD} \times I_S$$

is static power consumed by input buffers. If XTAL is running this power should be set to zero. where the static current (I\_S) is specified in Table 5  $\cdot$

$$P_{XTAL} = V_{DD} \times I_{DD\_XTAL}$$

is power consumption of XTAL circuit. The current of the XTAL circuit is provided in Table  $5 \cdot$  If XTAL is not used the power consumption is equal to zero.

$$P_C = V_{DDO} \times I_{DDC}$$

Common output power shared among all ten outputs. The current (I<sub>DDC</sub> is specified in Table  $5 \cdot .$

$$P_{D} = V_{DDO} \times (I_{DD} \times n \times f / 100MHz + V_{DDO} \times C_{LOAD} \times f \times n)$$

Dynamic power where dynamic current ( $I_{DD}$ ) is specified in Table 5  $\cdot$  ,  $C_{LOAD}$  is capacitive load driven by an output, f is frequency of the output clock and n is number of active outputs.

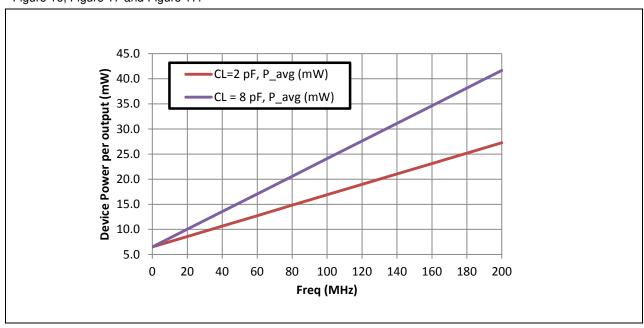

The power consumption for different clock frequencies and power supply voltages can be quickly estimated from Figure 16, Figure 17 and Figure 17.

Figure 16. Device power consumption per output for  $V_{DD} = V_{DDO} = 3.465V$

Figure 17. Device power consumption per output for  $V_{DD} = V_{DDO} = 2.625V$

Figure 18. Dynamic supply current per output for different output supply voltages

#### **Power Supply Filtering**

Each power pin (VDD and VDDO) should be decoupled with  $0.1\mu F$  capacitor with minimum equivalent series resistance (ESR) and minimum series inductance (ESL). For example 0402 X5R Ceramic Capacitors with 6.3V minimum rating could be used. These capacitors should be placed as close as possible to the power pins. To reduce the power noise from adjacent digital components on the board each power supply could be further insulted with low resistance ferrite bead with two capacitors. The ferrite bead will also insulate adjacent component from the noise generated from the device. Following figure shows recommended decoupling for each power pin.

Figure 19. Power Supply Filtering

#### **Device Control**

ZL30240 can be controlled via hardware pins (SEL pin tied low) or via SPI port (SEL pin tied high). The mode shall be selected during power up and it cannot be changed on the fly.

#### **Hardware Control Mode**

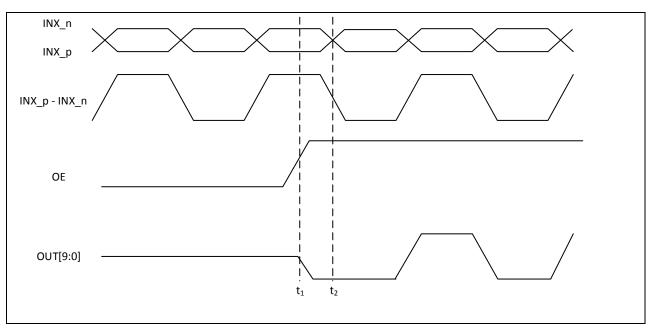

In this mode, ZL40240 is controlled via Output Enable (OE) and Input Select (SEL0/1) input pins. Output is disabled synchronously on the falling edge of the input (t<sub>2</sub>) as shown in Figure 20.

Figure 20. OE Output Disable

Outputs can be enabled by toggling OE pin high. As soon as OE pin goes high  $(t_1)$  the outputs will go from high-Z to low and will start to track the input after the first falling edge  $(t_2)$  of the input signal as shown in Figure 21.

Figure 21. OE Output Enable

#### **SPI Controlled Mode**

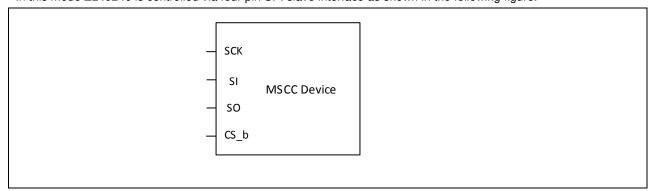

In this mode ZL40240 is controlled via four pin SPI slave interface as shown in the following figure.

Figure 22. SPI slave interface

The serial peripheral interface supports half-duplex processor mode which means that during a write cycle to the device, output data from the **SO** pin must be ignored. Similarly, the input data on the **SI** pin is ignored by the device during a read cycle.

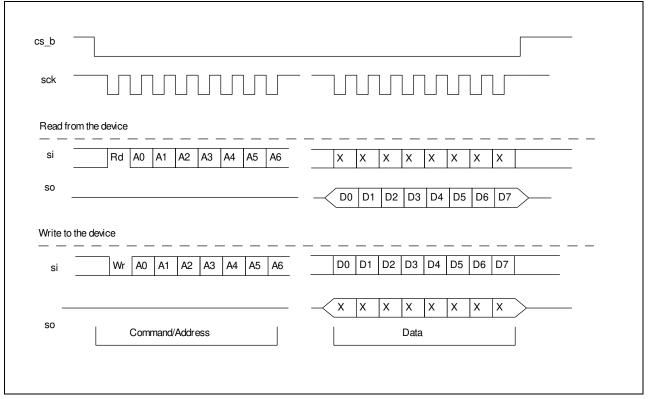

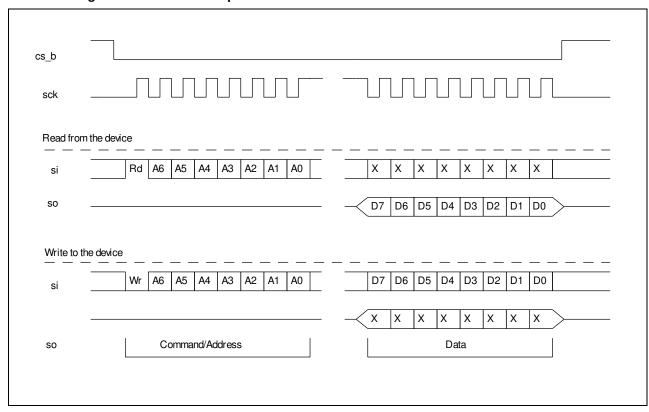

The SPI interface supports two modes of access: Most Significant bit (MSb) first transmission or Least Significant bit (LSb) first transmission. The mode is automatically selected based on the state of **SCK** pin when the **CS\_b** pin is active. If the **SCK** pin is low during **CS\_b** activation, then MSb first timing is selected. If the **SCK** pin is high during **CS\_b** activation, then LSb first timing is assumed.

The SPI port expects 1-bit to differentiate between read and write operation followed by 7-bit addressing and 8-bit data transmission. During SPI access, the **CS\_b** pin must be held low until the operation is complete. Burst read/write mode is also supported by leaving the chip select signal **CS\_b** is low after a read or a write. The address will be automatically incremented after each data byte is read or written.

Functional waveforms for the LSb and MSb first mode, and burst mode are shown in Figure 23 and Figure 24 respectively. Figure 25 shows an example of burst mode operation which allows user to read or write consecutive location in the register map.

Figure 23. Serial Peripheral Interface Functional Waveform - LSB First Mode

Figure 24. Serial Peripheral Interface Functional Waveform – MSB First Mode

Figure 25. Example of the Burst Mode Operation

## **Register Map**

The device is controlled by accessing registers through the serial interface. The following table provides a summary of the registers available for the configuration of the device.

Table 2 · Register Map

| Address<br>SPI A[6:0]<br>Hex (0x) | Name     | Data<br>D[7:0]        |

|-----------------------------------|----------|-----------------------|

| 00                                | XTALBG   | xtal_buf_gain[7:0]    |

| 01                                | XTALDL   | xtal_drive_level[7:0] |

| 02                                | XTALLC   | xtal_load_cap[7:0]    |

| 03                                | XTALNR   | xtal_normal_run       |

| 04                                | -        | Not used              |

| 05                                | INSEL    | input_select[1:0]     |

| 06                                | OUTLOW   | output_drive_low      |

| 07                                | OUTEN0   | output_enable[4:0]    |

| 08                                | OUTEN1   | output_enable[9:5]    |

| 09                                | DRVSTR0  | driver_strength[4:0]  |

| 0A                                | DRVSTR1  | driver_strength[9:5]  |

| 0B/0C/0D/0E                       | -        | Not used              |

| 0F/10                             | Reserved | Leave as default      |

| 11                                | DEVID    | Device ID             |

| 12 to 1F                          | Reserved | Leave as default      |

| Address | 0x00               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      | Hex   |

|---------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|

| XTALBG  |                    | XTAL Buffer Gain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |       |

| Bit     | Name               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Туре | Reset |

| 7:0     | xtal_buf_gain[7:0] | Programs crystal buffer (inverting amplifier) gain. Every bit pair (bits: 01, 23, 45, 67) of this register correspond to additional equal gain block which can be added (bits set) or removed (bits cleared).  Minimum gain is 0x00 (default) and 0xFF is maximum gain When reference input mode is "bypass XTAL mode" or "differential input modes" with HIGH xtal_normal_run bit, the buffer is disabled and follows "Input Selection".  When xtal_normal_run bit is LOW, XTAL buffer is in the "xtal forced run" mode and keep running.  8'b0000_0000: default crystal buffer strength. 8'b0000_011: enable additional buffer strength 8'b0011_0000: enable additional buffer strength 8'b1100_0000: enable additional buffer strength | RW   | FF    |

| Address | 0x01                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      | Hex   |

|---------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|

| XTALDL  | •                     | XTAL Drive Level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |       |

| Bit     | Name                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Туре | Reset |

| 7:0     | xtal_drive_level[7:0] | Internal damping resistance of crystal circuit to limit external crystal's drive level uW.  The value of damping resistor is determined by crystal's motion resistance of crystal's equivalent circuit.  Drive level should be lower than crystal manufacturer's specification.  Crystal's equivalent values should be requested to the manufacturer, (motion resistance and shunt capacitance).  The selected resistors are connected to XOUT.  Multiple bit combinations available by 7-bit control.  Resistors are connected in parallel. Hence, 0xFF is the smallest resistance and 0x01 is the highest resistance.  8'b0000_0000: disable all resistors 8'b0000_0001: 312 Ohm resistor 8'b0000_0100: 84 Ohm resistor 8'b0000_0100: 42 Ohm resistor 8'b0001_0000: 21 Ohm resistor 8'b0001_0000: 10.5 Ohm resistor 8'b0010_0000: 0 Ohm connection 8'b1000_0000: not used | RW   | 03    |

| Address | 0x02               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          | Hex          |

|---------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------|

| XTALLC  |                    | XTAL Load Capacitance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |              |

| Bit     | Name               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Typ<br>e | Reset        |

| 7:0     | xtal_load_cap[7:0] | Internal load capacitance of crystal circuit (0 pF to 21.75pF with the resolution of 0.25 pF).  XIN and XOUT have each capacitor connected to GND. Multiple bit combinations available between 8 capacitors.  8'b0000_0000: disable all xtal load capacitors 8'b0000_0001: enable capacitor 0.25 pF 8'b0000_0010: enable capacitor 0.5 pF 8'b0000_0100: enable capacitor 1 pF 8'b0000_1000: enable capacitor 2 pF 8'b0001_0000: enable capacitor 2 pF 8'b0010_0000: enable capacitor 4 pF 8'b0100_0000: enable capacitor 4 pF 8'b1000_0000: enable capacitor 8 pF | RW       | 80<br>(8 pF) |

| Address | 0x03            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      | Bin      |

|---------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------|

| XTALNR  |                 | XTAL Normal Run                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |          |

| Bit     | Name            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Туре | Reset    |

| 7:1     | Unused          | Unused                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R    | 11111111 |

| 0       | xtal_normal_run | When this bit is set high crystal oscillator circuit is running only if input_select[1:0] register at address 0x05 selects crystal mode (2'b10). This value is recommended because it provides best jitter performanceXO circuit is running only when it is needed.  When this bit is set low the crystal oscillator will keep running even if crystal oscillator is not selected in input_select[1:0] register at address 0x05. This mode should only be used when fast switching between input references and crystal oscillator is required. | RW   | 1        |

| Address | 0x05              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      | Bin   |

|---------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|

| INSEL   |                   | Input Select Register                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |       |

| Bit     | Name              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Туре | Reset |

| 7:2     | Unused            | Unused                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R    | 11111 |

| 1:0     | input_select[1:0] | Input reference clock selection. Proper external coupling and termination are required.  2'b00: differential input from IN0_p and IN0_n 2'b01: differential input from IN1_p and IN1_n 2'b10: 1) fundamental XTAL mode with XIN and XOUT (Use internal crystal oscillator circuits) OR 2) XTAL overdrive mode (single-ended clock signal with XIN)  2'b11: XTAL bypass mode (single-ended clock signal with XIN and disabled internal crystal buffer circuit in the analog block) | RW   | 10    |

| Address | 0x06             |                                                                                                                                                                                                                                                                                       |      | Bin     |

|---------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|

| OUTLOW  |                  | Output Drive Low                                                                                                                                                                                                                                                                      |      |         |

| Bit     | Name             | Description                                                                                                                                                                                                                                                                           | Туре | Reset   |

| 7:1     | Unused           | Unused                                                                                                                                                                                                                                                                                | R    | 1111111 |

| 0       | output_drive_low | After disabling outputs, output state is known state in logic LOW.  (This bit is used for only disabled outputs. Otherwise, enabled outputs are not impacted by this bit.)  1'b0: All LVCMOS outputs will be in high-impedance state.  1'b1: All LVCMOS outputs will drive logic LOW. | RW   | 0       |

| Address | 0x07               |                                                                                                                                                                                                                                                                          |      | Bin   |

|---------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|

| OUTEN0  |                    | Output Enable 0                                                                                                                                                                                                                                                          |      |       |

| Bit     | Name               | Description                                                                                                                                                                                                                                                              | Туре | Reset |

| 7:5     | Unused             | Unused                                                                                                                                                                                                                                                                   | R    | 111   |

| 4:0     | output_enable[4:0] | Output enable for OUT0/1/2/3/4. Disabled state is dependent on "out_drive_low" control bit. Each bit controls one output.  5'b0_0000: disable outputs 5'b0_0001: enable OUT0 5'b0_0100: enable OUT1 5'b0_0100: enable OUT2 5'b0_1000: enable OUT3 5'b1_0000: enable OUT4 |      | 11111 |

| Address | 0x08               |                                                                                                                                                                                                                                                                          |      | Hex   |

|---------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|

| OUTEN1  |                    | Output Enable 1                                                                                                                                                                                                                                                          |      |       |

| Bit     | Name               | Description                                                                                                                                                                                                                                                              | Туре | Reset |

| 7:5     | Unused             | Unused                                                                                                                                                                                                                                                                   | R    | 111   |

| 4:0     | output_enable[9:5] | Output enable for OUT5/6/7/8/9. Disabled state is dependent on "out_drive_low" control bit. Each bit controls one output.  5'b0_0000: disable outputs 5'b0_0001: enable OUT5 5'b0_0100: enable OUT6 5'b0_0100: enable OUT7 5'b0_1000: enable OUT8 5'b1_0000: enable OUT9 | RW   | 11111 |

| Address | 0x09                 |                                                                                                                                                                                                                                                                                                                                                                           |      | Hex   |

|---------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|

| DRVSTR0 |                      | Driver Strength 0                                                                                                                                                                                                                                                                                                                                                         |      |       |

| Bit     | Name                 | Description                                                                                                                                                                                                                                                                                                                                                               | Туре | Reset |

| 7:5     | Unused               | Unused                                                                                                                                                                                                                                                                                                                                                                    | R    | 111   |

| 4:0     | driver_strength[4:0] | Output driver strength for OUT0/1/2/3/4. Each bit controls one output. Low driver strength and high driver strength.  5'b0_0000: low driver strength outputs 5'b0_0001: high driver strength for OUT0 5'b0_0010: high driver strength for OUT1 5'b0_0100: high driver strength for OUT2 5'b0_1000: high driver strength for OUT3 5'b1_0000: high driver strength for OUT4 | RW   | 11111 |

| Address | 0x0A                 |                                                                                                                                                                                                                                                                                                                                                                           |      | Hex   |

|---------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|

| DRVSTR1 |                      | Driver Strength 1                                                                                                                                                                                                                                                                                                                                                         |      |       |

| Bit     | Name                 | Description                                                                                                                                                                                                                                                                                                                                                               | Туре | Reset |

| 7:5     | Unused               | Unused                                                                                                                                                                                                                                                                                                                                                                    | R    | 111   |

| 4:0     | driver_strength[9:5] | Output driver strength for OUT5/6/7/8/9. Each bit controls one output. Low driver strength and high driver strength.  5'b0_0000: low driver strength outputs 5'b0_0001: high driver strength for OUT5 5'b0_0010: high driver strength for OUT6 5'b0_0100: high driver strength for OUT7 5'b0_1000: high driver strength for OUT8 5'b1_0000: high driver strength for OUT9 | RW   | 11111 |

| Address | 0x11   |                       |      | Hex   |

|---------|--------|-----------------------|------|-------|

| DEVID   |        | Device Identification |      |       |

| Bit     | Name   | Description           | Туре | Reset |

| 7:5     | Unused | Unused                | R    | 0     |

| 4:0     | dev_id | Device ID.            | RO   | 01    |

|         |        | 5'h01: ZL40240        |      |       |