Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Flexible 512 Channel DX with Enhanced

Data Sheet

**Features**

- 512 channel x 512 channel non-blocking switch at 2.048 Mbps, 4.096 Mbps or 8.192 Mbps operation

- Rate conversion between the ST-BUS inputs and ST-BUS outputs

- Integrated Digital Phase-Locked Loop (DPLL) meets Telcordia GR-1244-CORE Stratum 4 enhanced specifications

- DPLL provides automatic reference switching, jitter attenuation, holdover and free run functions

- Per-stream ST-BUS input with data rate selection of 2.048 Mbps, 4.096 Mbps or 8.192 Mbps

- Per-stream ST-BUS output with data rate selection of 2.048 Mbps, 4.096 Mbps or 8.192 Mbps; the output data rate can be different than the input data rate

- Per-stream high impedance control output for every ST-BUS output with fractional bit advancement

- Per-stream input channel and input bit delay programming with fractional bit delay

September 2011

#### **Ordering Information**

ZL50010/GDC 144 Ball LBGA Trays

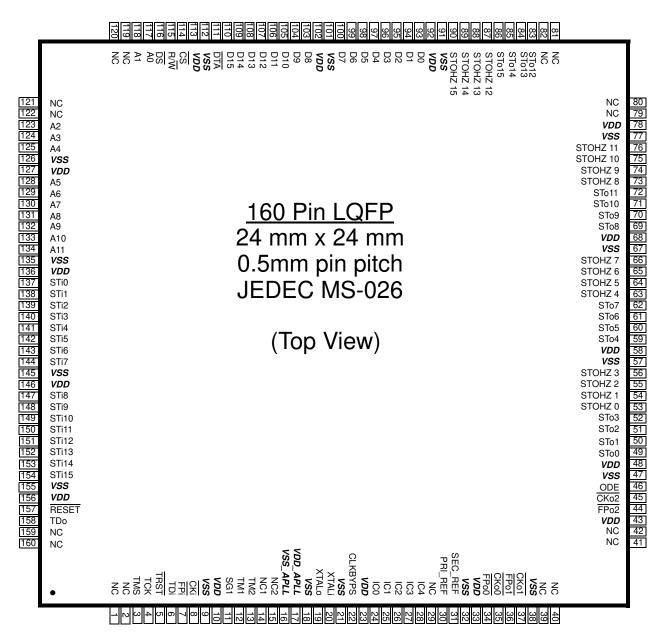

ZL50010QCG1 160 Pin LQFP\* Trays, Bake & Drypack

ZL50010GDG2 144 Ball LBGA\*\* Trays, Bake & Drypack

\*Pb Free Matte Tin

\*\*Pb Free Tin/Silver/Coppoer

-40°C to +85°C

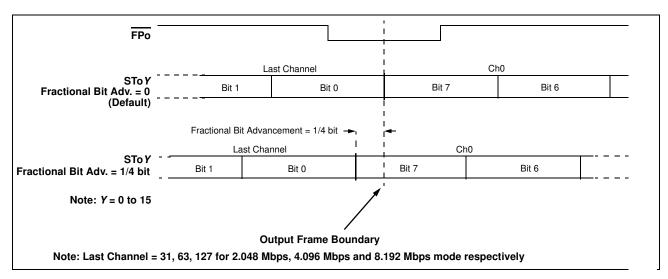

- Per-stream output channel and output bit delay programming with fractional bit advancement

- Multiple frame pulse outputs and reference clock outputs

- Per-channel constant throughput delay

- Per-channel high impedance output control

- · Per-channel message mode

- Per-channel Pseudo Random Bit Sequence (PRBS) pattern generation and bit error detection

- Control interface compatible to Motorola nonmultiplexed CPUs

- Connection memory block programming capability

- IEEE-1149.1 (JTAG) test port

- 3.3 V I/O with 5 V tolerant input

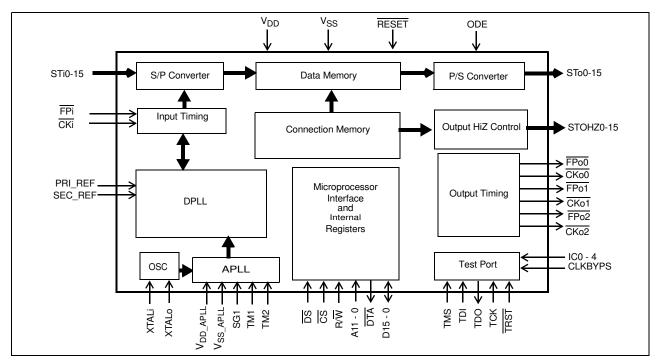

Figure 1 - ZL50010 Functional Block Diagram

Zarlink Semiconductor US Patent No. 5,602,884, UK Patent No. 0772912, France Brevete S.G.D.G. 0772912; Germany DBP No. 69502724.7-08

### **Applications**

- Small and medium digital switching platforms

- Access Servers

- Time Division Multiplexers

- Computer Telephony Integration

- Digital Loop Carriers

### **Description**

The device has 16 ST-BUS inputs (STi0-15) and 16 ST-BUS outputs (STo0-15). It is a non-blocking digital switch with 512 64 kbps channels and performs rate conversion between the ST-BUS inputs and ST-BUS outputs. The ST-BUS inputs accept serial input data streams with the data rate of 2.048 Mbps, 4.096 Mbps or 8.192 Mbps on a per-stream basis. The ST-BUS outputs deliver serial output data streams with the data rate of 2.048 Mbps, 4.096 Mbps or 8.192 Mbps on a per-stream basis. The device also provides 16 high impedance control outputs (STOHZ 0-15) to support the use of external high impedance control buffers.

The ZL50010 has features that are programmable on a per-stream or per-channel basis including message mode, input bit delay, output bit advancement, constant throughput delay and high impedance output control.

The on-chip DPLL meets Telcordia GR-1244-CORE Stratum 4 enhanced specifications (Stratum 4E). It accepts two dedicated timing reference inputs at either 8 kHz, 1.544 MHz or 2.048 MHz. Alternatively, one reference can be replaced by an internal 8 kHz signal derived from the ST-BUS input frame boundary. The DPLL provides automatic reference switching, jitter attenuation, holdover and free run functions. It can be used as a system's ST-BUS timing source which is synchronized to the network. The DPLL can also be bypassed so that the device operates under system timing.

### ZL50010

# **Table of Contents**

| Features                                                               |    |

|------------------------------------------------------------------------|----|

| Applications                                                           | 2  |

| Description                                                            | 2  |

| Changes Summary                                                        | 8  |

| 1.0 Device Overview                                                    |    |

| 2.0 Functional Description                                             |    |

| 2.1 ST-BUS Input Data Rate and Input Timing                            |    |

| 2.1.1 ST-BUS Input Operation Mode                                      |    |

| 2.1.2 Frame Pulse Input and Clock Input Timing                         |    |

| 2.1.3 ST-BUS Input Timing                                              |    |

| 2.1.4 Improved Input Jitter Tolerance with Frame Boundary Determinator |    |

| 2.2 ST-BUS Output Data Rate and Output Timing                          |    |

| 2.2.1 ST-BUS Output Operation Mode                                     |    |

| 2.2.2 Frame Pulse Output and Clock Output Timing                       |    |

| 2.2.3 ST-BUS Output Timing                                             |    |

| 2.3 Serial Data Input Delay and Serial Data Output Offset              | 23 |

| 2.3.1 Input Channel Delay Programming                                  |    |

| 2.3.2 Input Bit Delay Programming                                      | 23 |

| 2.3.3 Fractional Input Bit Delay Programming                           | 24 |

| 2.3.4 Output Channel Delay Programming                                 |    |

| 2.3.5 Output Bit Delay Programming                                     |    |

| 2.3.6 Fractional Output Bit Advancement Programming                    |    |

| 2.3.7 External High Impedance Control, STOHZ 0 to 15                   |    |

| 2.4 Data Delay Through The Switching Paths                             |    |

| 2.5 Connection Memory Description                                      |    |

| 2.5.1 Connection Memory Block Programming.                             | 29 |

| 2.6 Bit Error Rate (BER) Test                                          | 30 |

| 2.7 Quadrant frame programming                                         |    |

| 2.8 Microprocessor Port                                                |    |

| 2.9 Digital Phase-Locked Loop (DPLL) Operation                         |    |

| 2.9.1 DPLL Master Mode                                                 |    |

| 2.9.1.1 Master Mode Reference Inputs                                   |    |

| 2.9.1.2 Master Mode Reference Switching                                |    |

| 2.9.1.4 Master Mode Output Offset Adjustment                           |    |

| 2.9.2 DPLL Freerun Mode                                                |    |

| 2.9.3 DPLL Bypass Mode                                                 |    |

| 2.10 DPLL Functional Description                                       |    |

| 2.10.1 CKi/FPi Synchronizer and PRI_REF Select Mux Circuits            |    |

| 2.10.2 Reference Select and Frequency Mode Mux Circuits                |    |

| 2.10.3 Skew Control Circuit.                                           |    |

| 2.10.4 Reference Monitor Circuit                                       |    |

| 2.10.5 LOS Control Circuit                                             |    |

| 2.10.6 State Machine Circuit                                           |    |

| 2.10.7 Maximum Time Interval Error (MTIE) Circuit                      |    |

| 2.10.8 Phase-Locked Loop (PLL) Circuit                                 |    |

| 2.11 DPLL Performance                                                  |    |

| 2.11.1 Intrinsic Jitter                                                | 41 |

| 2.11.2 DPLL Jitter Tolerance                                           | 41 |

| 2.11.3 Jitter Transfer.                                                |    |

| 2.11.4 Frequency Accuracy                                              |    |

| 2.11.5 Holdover Accuracy                                               | 43 |

### **Table of Contents**

| 2.11.7 Phase Slope.       43         2.11.8 MTIE.       43         2.11.9 Phase Lock Time.       44         2.12 Alignment Between Input and Output Frame Pulses.       44         3.0 Oscillator Requirements.       45         3.1 External Crystal Oscillator.       45         3.2 External Clock Oscillator.       46         4.0 Device Reset and Initialization.       47         5.0 JTAG Support.       47         5.1 Test Access Port (TAP).       47         5.2 Instruction Register.       48         5.3 Test Data Register.       48         5.4 BSDL.       48         6.0 Register Address Mapping.       49         7.0 Detail Register description.       51         8.0 Memory Address Mappings.       69 | 2.11.6 Locking Range                                 | 43 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|----|

| 2.11.8 MTIE.       43         2.11.9 Phase Lock Time.       44         2.12 Alignment Between Input and Output Frame Pulses.       44         3.0 Oscillator Requirements.       45         3.1 External Crystal Oscillator.       45         3.2 External Clock Oscillator.       46         4.0 Device Reset and Initialization.       47         5.0 JTAG Support.       47         5.1 Test Access Port (TAP).       47         5.2 Instruction Register.       48         5.3 Test Data Register.       48         5.4 BSDL.       48         6.0 Register Address Mapping       49         7.0 Detail Register description       51                                                                                      |                                                      |    |

| 2.11.9 Phase Lock Time       44         2.12 Alignment Between Input and Output Frame Pulses.       44         3.0 Oscillator Requirements       45         3.1 External Crystal Oscillator       45         3.2 External Clock Oscillator       46         4.0 Device Reset and Initialization       47         5.0 JTAG Support       47         5.1 Test Access Port (TAP)       47         5.2 Instruction Register       48         5.3 Test Data Register       48         5.4 BSDL       48         6.0 Register Address Mapping       49         7.0 Detail Register description       51                                                                                                                              |                                                      |    |

| 3.0 Oscillator Requirements       45         3.1 External Crystal Oscillator       45         3.2 External Clock Oscillator       46         4.0 Device Reset and Initialization       47         5.0 JTAG Support       47         5.1 Test Access Port (TAP)       47         5.2 Instruction Register       48         5.3 Test Data Register       48         5.4 BSDL       48         6.0 Register Address Mapping       49         7.0 Detail Register description       51                                                                                                                                                                                                                                             |                                                      |    |

| 3.1 External Crystal Oscillator       45         3.2 External Clock Oscillator       46         4.0 Device Reset and Initialization       47         5.0 JTAG Support       47         5.1 Test Access Port (TAP)       47         5.2 Instruction Register       48         5.3 Test Data Register       48         5.4 BSDL       48         6.0 Register Address Mapping       49         7.0 Detail Register description       51                                                                                                                                                                                                                                                                                          | 2.12 Alignment Between Input and Output Frame Pulses | 44 |

| 3.1 External Crystal Oscillator       45         3.2 External Clock Oscillator       46         4.0 Device Reset and Initialization       47         5.0 JTAG Support       47         5.1 Test Access Port (TAP)       47         5.2 Instruction Register       48         5.3 Test Data Register       48         5.4 BSDL       48         6.0 Register Address Mapping       49         7.0 Detail Register description       51                                                                                                                                                                                                                                                                                          | 3.0 Oscillator Requirements                          | 45 |

| 3.2 External Clock Oscillator       46         4.0 Device Reset and Initialization       47         5.0 JTAG Support       47         5.1 Test Access Port (TAP)       47         5.2 Instruction Register       48         5.3 Test Data Register       48         5.4 BSDL       48         6.0 Register Address Mapping       49         7.0 Detail Register description       51                                                                                                                                                                                                                                                                                                                                           | ·                                                    |    |

| 5.0 JTAG Support.       47         5.1 Test Access Port (TAP).       47         5.2 Instruction Register.       48         5.3 Test Data Register.       48         5.4 BSDL.       48         6.0 Register Address Mapping       49         7.0 Detail Register description       51                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                      |    |

| 5.0 JTAG Support.       47         5.1 Test Access Port (TAP).       47         5.2 Instruction Register.       48         5.3 Test Data Register.       48         5.4 BSDL.       48         6.0 Register Address Mapping       49         7.0 Detail Register description       51                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4.0 Device Reset and Initialization                  | 47 |

| 5.1 Test Access Port (TAP)       47         5.2 Instruction Register       48         5.3 Test Data Register       48         5.4 BSDL       48         6.0 Register Address Mapping       49         7.0 Detail Register description       51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5.0 JTAG Support                                     | 47 |

| 5.2 Instruction Register       48         5.3 Test Data Register       48         5.4 BSDL       48         6.0 Register Address Mapping       49         7.0 Detail Register description       51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                      |    |

| 5.3 Test Data Register.       48         5.4 BSDL.       48         6.0 Register Address Mapping.       49         7.0 Detail Register description.       51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                      |    |

| 5.4 BSDL       48         6.0 Register Address Mapping       49         7.0 Detail Register description       51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                      |    |

| 7.0 Detail Register description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                      |    |

| 7.0 Detail Register description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6.0 Register Address Mapping                         | 49 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                      |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                      |    |

| 9.0 Connection Memory Bit Assignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                      |    |

# **List of Figures**

| Figure 1 - ZL50010 Functional Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | - 4                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Figure 2 - 24 mm x 24 mm LQFP (JEDEC MS-026) Pinout Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 9                                                                                                                             |

| Figure 3 - 13 mm x 13 mm 144 Ball LBGA Pinout Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 10                                                                                                                          |

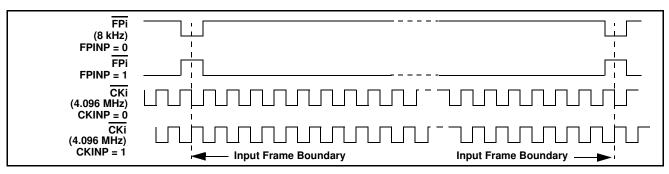

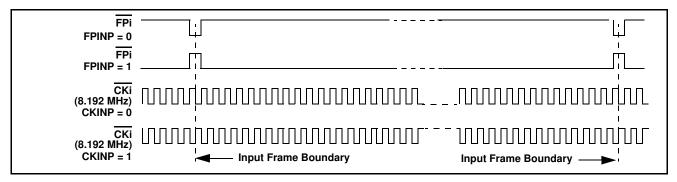

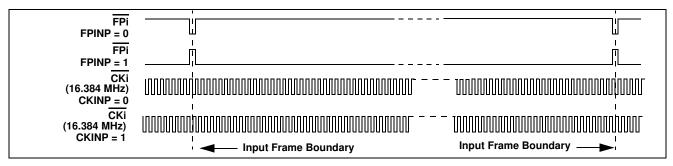

| Figure 4 - Input Timing when (CKIN2 to CKIN0 Bits = 010) in the Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 17                                                                                                                          |

| Figure 5 - Input Timing when (CKIN2 to CKIN0 Bits = 001) in the Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 17                                                                                                                          |

| Figure 6 - Input Timing when (CKIN2 to CKIN0 Bits = 000) in the Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 17                                                                                                                          |

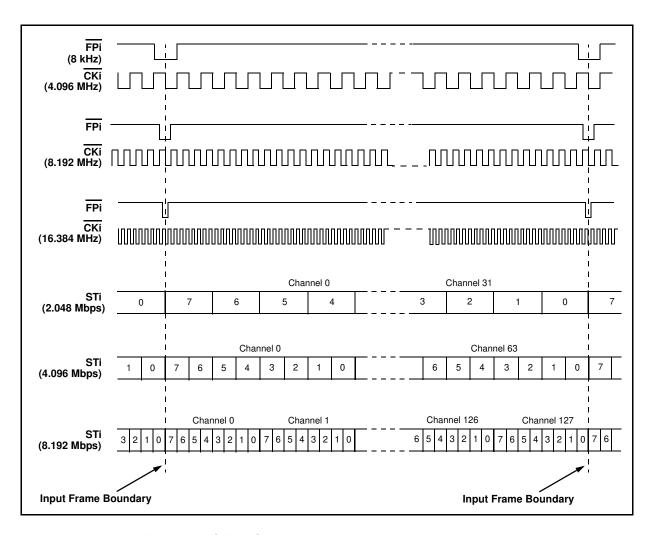

| Figure 7 - ST-BUS Input Timing for Various Input Data Rates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 18                                                                                                                          |

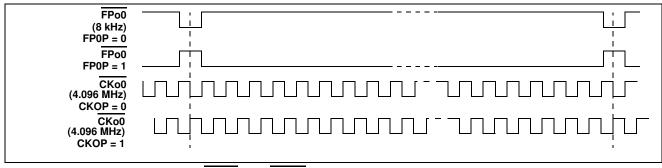

| Figure 8 - FPo0 and CKo0 Output Timing when the CKFP0 Bit = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 20                                                                                                                          |

| Figure 9 - FPo0 and CKo0 Output Timing when the CKFP0 Bit = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 20                                                                                                                          |

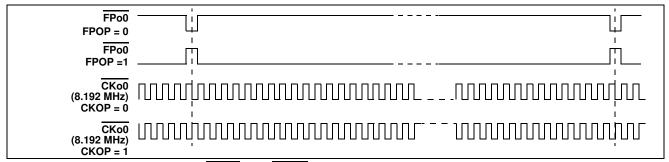

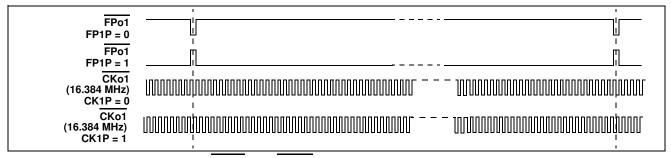

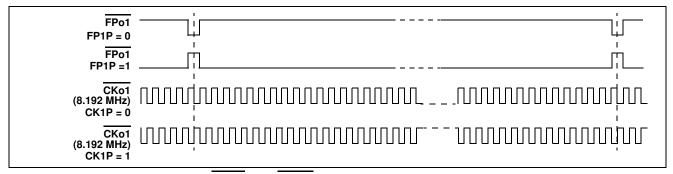

| Figure 10 - FPo1 and CKo1 Output Timing when the CKFP1 Bit = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                               |

| Figure 11 - FPo1 and CKo1 Output Timing when the CKFP1 Bit = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                               |

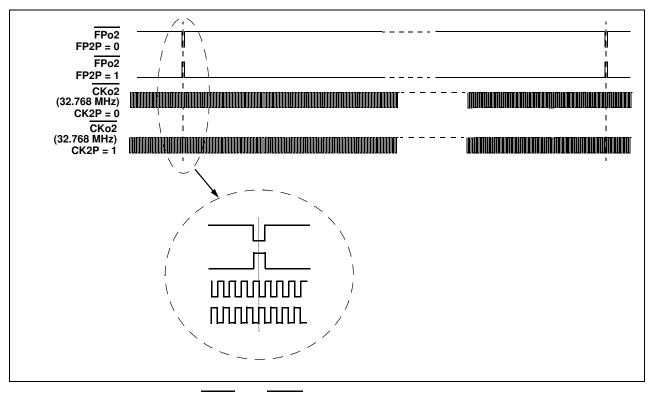

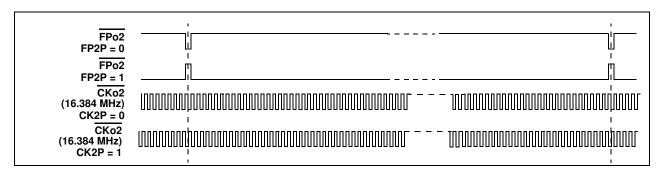

| Figure 12 - FPo2 and CKo2 Output Timing when the CKFP2 Bit = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 21                                                                                                                          |

| Figure 13 - FPo2 and CKo2 Output Timing when the CKFP2 Bit = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                               |

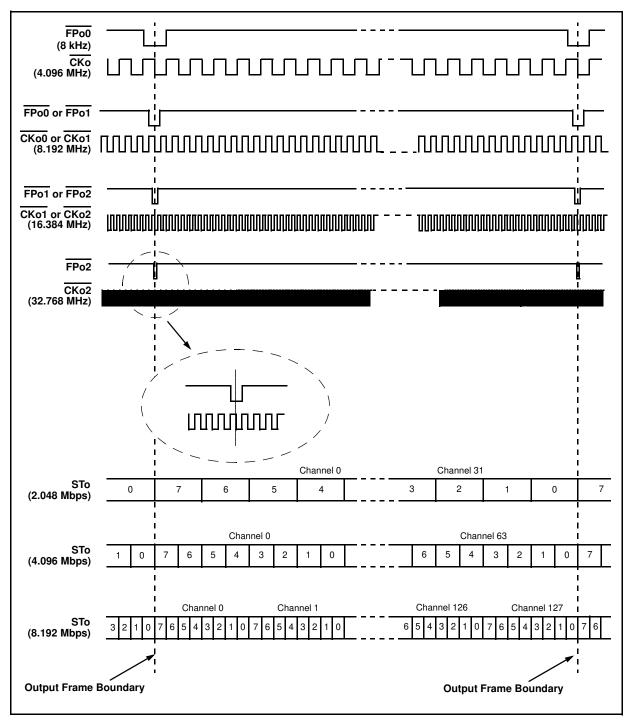

| Figure 14 - ST-BUS Output Timing for Various Output Data Rates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                               |

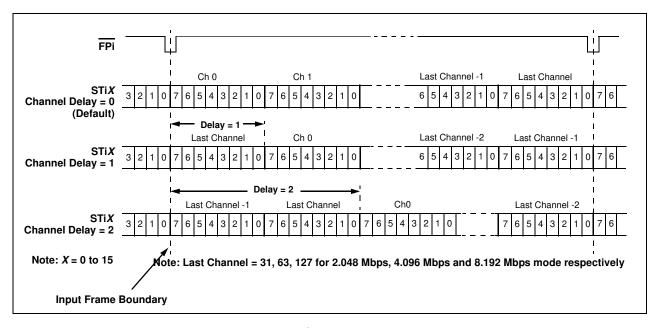

| Figure 15 - Input Channel Delay Timing Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                               |

| Figure 16 - Input Bit Delay Timing Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                               |

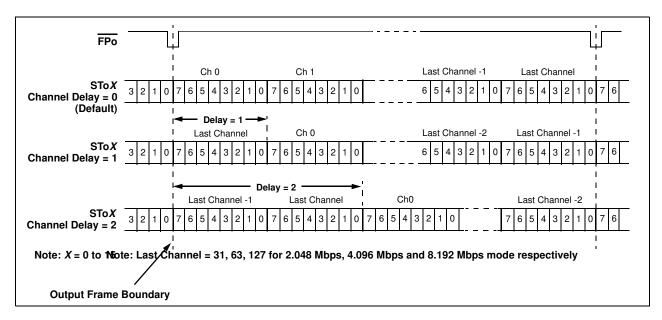

| Figure 17 - Output Channel Delay Timing Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                               |

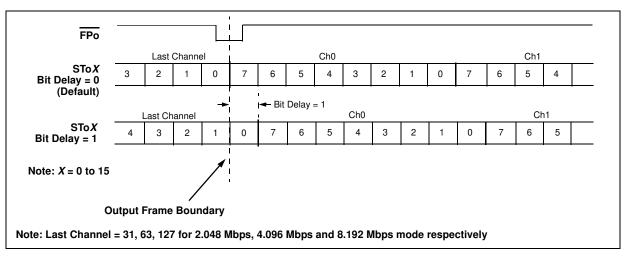

| Figure 18 - Output Bit Delay Timing Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                               |

| Figure 19 - Fractional Output Bit Advancement Timing Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                               |

| Figure 20 - Example: External High Impedance Control Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                               |

| Figure 21 - Data Throughput Delay when Input and Output Channel Delay are Disabled for Input Ch0 Switcher                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                               |

| Output Ch0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                               |

| Figure 22 - Data Throughput Delay when Input Channel Delay is Enabled and Output Channel Delay is Disabl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ed                                                                                                                            |

| for Input Ch0 Switched to Output Ch0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 28                                                                                                                          |

| Figure 23 - Data Throughput Delay when Input Channel Delay is Disabled and Output Channel Delay is Enabl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ed                                                                                                                            |

| for Input Ch0 Switch to Output Ch0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 28                                                                                                                          |

| Figure 24 - Data Throughput Delay when Input and Output Channel Delay are Enabled for Input Ch0 Switched                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | to t                                                                                                                          |

| Output Ch0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 29                                                                                                                          |

| Figure 25 - DPLL Functional Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 36                                                                                                                          |

| Figure 26 - Skew Control Circuit Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 37                                                                                                                          |

| Figure 26 - Skew Control Circuit Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 37<br>. 38                                                                                                                  |

| Figure 26 - Skew Control Circuit Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 37<br>. 38<br>. 39                                                                                                          |

| Figure 26 - Skew Control Circuit Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 37<br>. 38<br>. 39<br>. 42                                                                                                  |

| Figure 26 - Skew Control Circuit Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 37<br>. 38<br>. 39<br>. 42<br>. 42                                                                                          |

| Figure 26 - Skew Control Circuit Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 37<br>. 38<br>. 39<br>. 42<br>. 42                                                                                          |

| Figure 26 - Skew Control Circuit Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 37<br>. 38<br>. 39<br>. 42<br>. 42<br>. 45                                                                                  |

| Figure 26 - Skew Control Circuit Diagram .  Figure 27 - State Machine Diagram .  Figure 28 - Block Diagram of the PLL Module .  Figure 29 - DPLL Jitter Transfer Function Diagram - Wide Range of Frequencies .  Figure 30 - Detailed DPLL Jitter Transfer Function Diagram (Wander Transfer Diagram) .  Figure 31 - Crystal Oscillator Circuit .  Figure 32 - External Clock Oscillator Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 37<br>. 38<br>. 39<br>. 42<br>. 45<br>. 46<br>. 73                                                                          |

| Figure 26 - Skew Control Circuit Diagram .  Figure 27 - State Machine Diagram .  Figure 28 - Block Diagram of the PLL Module .  Figure 29 - DPLL Jitter Transfer Function Diagram - Wide Range of Frequencies .  Figure 30 - Detailed DPLL Jitter Transfer Function Diagram (Wander Transfer Diagram) .  Figure 31 - Crystal Oscillator Circuit .  Figure 32 - External Clock Oscillator Circuit .  Figure 33 - Frame Pulse Input and Clock Input Timing Diagram .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 37<br>. 38<br>. 39<br>. 42<br>. 45<br>. 46<br>. 73                                                                          |

| Figure 26 - Skew Control Circuit Diagram .  Figure 27 - State Machine Diagram .  Figure 28 - Block Diagram of the PLL Module .  Figure 29 - DPLL Jitter Transfer Function Diagram - Wide Range of Frequencies .  Figure 30 - Detailed DPLL Jitter Transfer Function Diagram (Wander Transfer Diagram) .  Figure 31 - Crystal Oscillator Circuit .  Figure 32 - External Clock Oscillator Circuit .  Figure 33 - Frame Pulse Input and Clock Input Timing Diagram .  Figure 34 - Frame Boundary Timing with Input Clock (Cycle-to-Cycle) Variation .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 37<br>. 38<br>. 39<br>. 42<br>. 45<br>. 46<br>. 73<br>. 74                                                                  |

| Figure 26 - Skew Control Circuit Diagram .  Figure 27 - State Machine Diagram .  Figure 28 - Block Diagram of the PLL Module .  Figure 29 - DPLL Jitter Transfer Function Diagram - Wide Range of Frequencies .  Figure 30 - Detailed DPLL Jitter Transfer Function Diagram (Wander Transfer Diagram) .  Figure 31 - Crystal Oscillator Circuit .  Figure 32 - External Clock Oscillator Circuit .  Figure 33 - Frame Pulse Input and Clock Input Timing Diagram .  Figure 34 - Frame Boundary Timing with Input Clock (Cycle-to-Cycle) Variation .  Figure 35 - Frame Boundary Timing with Input Frame Pulse (Cycle-to-Cycle) Variation .  Figure 36 - XTALi Input Timing Diagram when Clock Oscillator is Connected                                                                                                                                                                                                                                                                                                                                                                                                                | . 37<br>. 38<br>. 39<br>. 42<br>. 42<br>. 45<br>. 46<br>. 73<br>. 73                                                          |

| Figure 26 - Skew Control Circuit Diagram .  Figure 27 - State Machine Diagram .  Figure 28 - Block Diagram of the PLL Module .  Figure 29 - DPLL Jitter Transfer Function Diagram - Wide Range of Frequencies .  Figure 30 - Detailed DPLL Jitter Transfer Function Diagram (Wander Transfer Diagram) .  Figure 31 - Crystal Oscillator Circuit .  Figure 32 - External Clock Oscillator Circuit .  Figure 33 - Frame Pulse Input and Clock Input Timing Diagram .  Figure 34 - Frame Boundary Timing with Input Clock (Cycle-to-Cycle) Variation .  Figure 35 - Frame Boundary Timing with Input Frame Pulse (Cycle-to-Cycle) Variation .  Figure 36 - XTALi Input Timing Diagram when Clock Oscillator is Connected .  Figure 37 - Reference Input Timing Diagram when the Input Frequency = 8 kHz .                                                                                                                                                                                                                                                                                                                               | . 37<br>. 38<br>. 39<br>. 42<br>. 45<br>. 45<br>. 73<br>. 73<br>. 74                                                          |