Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Enhanced 1 K Digital Switch with Stratum 4E DPLL

Data Sheet

**Features**

1024 channel x 1024 channel non-blocking digital Time Division Multiplex (TDM) switch at 4.096, 8.192 and 16.384 Mbps or using a combination of ports running at 2.048, 4.096, 8.192 and 16.384 Mbps

- 16 serial TDM input, 16 serial TDM output streams

- Integrated Digital Phase-Locked Loop (DPLL) exceeds Telcordia GR-1244-CORE Stratum 4E specifications

- Output clocks have less than 1 ns of jitter (except for the 1.544 MHz output)

- DPLL provides holdover, freerun and jitter attenuation features with four independent reference source inputs

- Exceptional input clock cycle to cycle variation tolerance (20 ns for all rates)

September 2011

#### **Ordering Information**

ZL50015GAC 256 Ball PBGA Trays ZL50015QCC1 256 Lead LQFP\* Trays ZL50015GAG2 256 Ball PBGA\*\* Trays

\*Pb Free Matte Tin

\*\*Pb Free Tin/SilverCopper

-40°C to +85°C

- Output streams can be configured as bidirectional for connection to backplanes

- Per-stream input and output data rate conversion selection at 2.048 Mbps, 4.096 Mbps, 8.192 Mbps or 16.384 Mbps. Input and output data rates can differ

- Per-stream high impedance control outputs (STOHZ) for 8 output streams

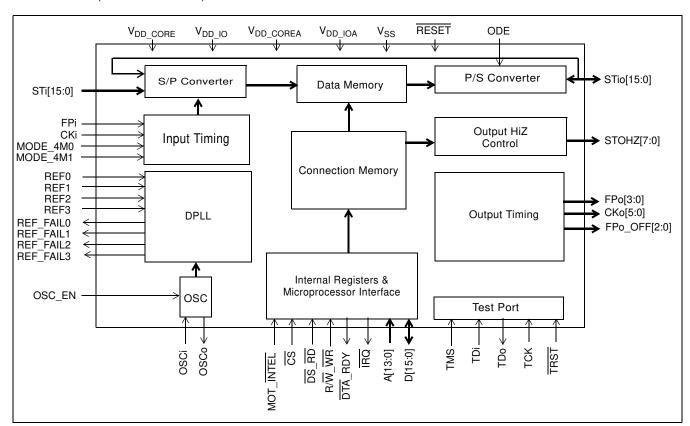

Figure 1 - ZL50015 Functional Block Diagram

Zarlink Semiconductor US Patent No. 5,602,884, UK Patent No. 0772912, France Brevete S.G.D.G. 0772912; Germany DBP No. 69502724.7-08

- Per-stream input bit delay with flexible sampling point selection

- · Per-stream output bit and fractional bit advancement

- Per-channel ITU-T G.711 PCM A-Law/μ-Law Translation

- · Four frame pulse and six reference clock outputs

- · Three programmable delayed frame pulse outputs

- Input clock: 4.096 MHz, 8.192 MHz, 16.384 MHz

- Input frame pulses: 61 ns, 122 ns, 244 ns

- · Per-channel constant or variable throughput delay for frame integrity and low latency applications

- Per Stream (16) Bit Error Rate Test circuits complying to ITU-O.151

- · Per-channel high impedance output control

- · Per-channel message mode

- · Control interface compatible with Intel and Motorola 16-bit non-multiplexed buses

- · Connection memory block programming

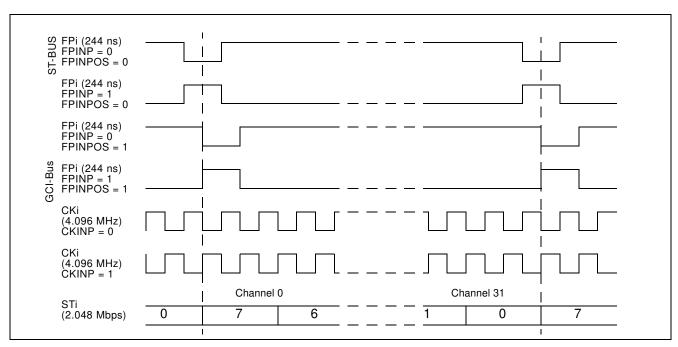

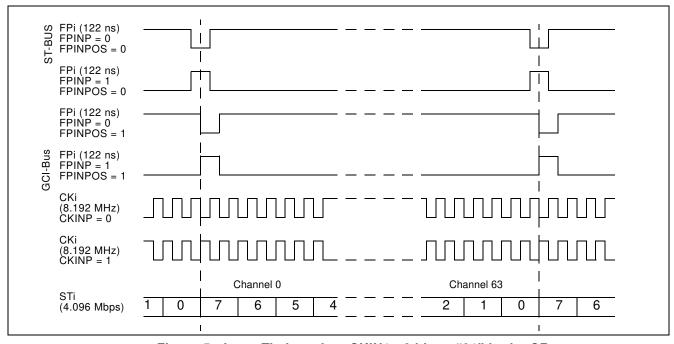

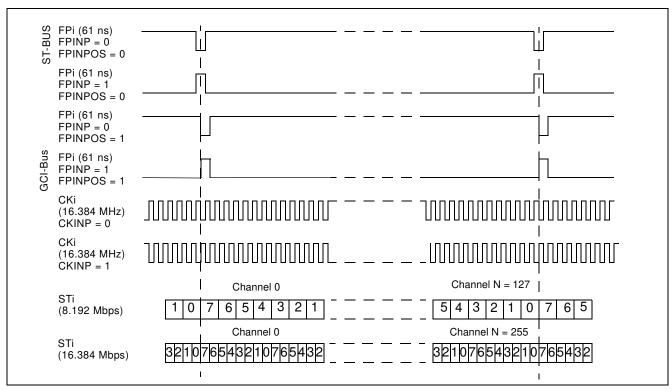

- Supports ST-BUS and GCI-Bus standards for input and output timing

- IEEE-1149.1 (JTAG) test port

- 3.3 V I/O with 5 V tolerant inputs; 1.8 V core voltage

### **Applications**

- PBX and IP-PBX

- Small and medium digital switching platforms

- · Remote access servers and concentrators

- · Wireless base stations and controllers

- Multi service access platforms

- Digital Loop Carriers

- · Computer Telephony Integration

### **Description**

The ZL50015 is a maximum 1,024 x 1,024 channel non-blocking digital Time Division Multiplex (TDM) switch. It has sixteen input streams (STi0 - 15) and sixteen output streams (STi00 - 15). The device can switch 64 kbps and Nx64 kbps TDM channels from any input stream to any output stream. Each of the input and output streams can be independently programmed to operate at any of the following data rates: 2.048 Mbps, 4.096 Mbps, 8.192 Mbps or 16.384 Mbps. The ZL50015 provides up to eight high impedance control outputs (STOHZ0 - 7) to support the use of external tristate drivers for the first eight output streams (STi00 - 15). The output streams can be configured to operate in bi-directional mode, in which case STi0 - 15 will be ignored.

The device contains two types of internal memory - data memory and connection memory. There are four modes of operation - Connection Mode, Message Mode, BER mode and high impedance mode. In Connection Mode, the contents of the connection memory define, for each output stream and channel, the source stream and channel (the actual data to be output is stored in the data memory). In Message Mode, the connection memory is used for the storage of microprocessor data. Using Zarlink's Message Mode capability, microprocessor data can be broadcast to the data output streams on a per-channel basis. This feature is useful for transferring control and status information for external circuits or other TDM devices. In BER mode the output channel data is replaced with a pseudorandom bit sequence (PRBS) from one of 16 PRBS generators that generates a 2<sup>15</sup>-1 pattern. On the input side channels can be routed to one of 16 bit error detectors. In high impedance mode the selected output channel can be put into a high impedance state.

When the device is operating as a timing master, the internal digital PLL is in use. In this mode, an external 20.000 MHz crystal is required for the on-chip crystal oscillator. The DPLL is phase-locked to one of four input reference signals (which can be 8 kHz, 1.544 MHz, 2.048 MHz, 4.096 MHz, 8.192 MHz, 16.384 MHz or 19.44 MHz provided on REF0 - 3). The on-chip DPLL operates in normal, holdover or freerun mode and offers jitter attenuation. The jitter attenuation function exceeds the Stratum 4E specification.

The configurable non-multiplexed microprocessor port allows users to program various device operating modes and switching configurations. Users can employ the microprocessor port to perform register read/write, connection memory read/write and data memory read operations. The port is configurable to interface with either Motorola or Intel-type microprocessors.

The device also supports the mandatory requirements of the IEEE-1149.1 (JTAG) standard via the test port.

## **Table of Contents**

| Features                                                   | 1    |

|------------------------------------------------------------|------|

| Applications                                               |      |

| Description                                                |      |

| Changes Summary                                            | . 10 |

| 1.0 Pinout Diagrams                                        | . 11 |

| 1.1 BGA Pinout                                             |      |

| 1.2 QFP Pinout                                             | . 12 |

| 2.0 Pin Description                                        | . 13 |

| 3.0 Device Overview                                        | . 20 |

| 4.0 Data Rates and Timing                                  |      |

| 4.1 External High Impedance Control, STOHZ0 - 7            |      |

| 4.2 Input Clock (CKi) and Input Frame Pulse (FPi) Timing   |      |

| 5.0 ST-BUS and GCI-Bus Timing                              | . 24 |

| 6.0 Output Timing Generation                               |      |

| 7.0 Data Input Delay and Data Output Advancement           |      |

| 7.1 Input Bit Delay Programming.                           |      |

| 7.2 Input Bit Sampling Point Programming                   |      |

| 7.3 Output Advancement Programming                         |      |

| 7.4 Fractional Output Bit Advancement Programming          |      |

| 7.5 External High Impedance Control Advancement            |      |

| 8.0 Data Delay Through the Switching Paths                 | . 33 |

| 8.1 Variable Delay Mode                                    |      |

| 8.2 Constant Delay Mode                                    |      |

| 9.0 Connection Memory Description                          | . 35 |

| 10.0 Connection Memory Block Programming                   |      |

| 10.1 Memory Block Programming Procedure                    |      |

| 11.0 Device Operation in Master Mode and Slave Modes       | . 36 |

| 11.1 Master Mode Operation                                 | . 37 |

| 11.2 Divided Slave Mode Operation                          | . 38 |

| 11.3 Multiplied Slave Mode Operation                       | . 38 |

| 12.0 Overall Operation of the DPLL                         | . 38 |

| 12.1 DPLL Timing Modes                                     |      |

| 12.1.1 Normal Mode                                         |      |

| 12.1.2 Holdover Mode                                       |      |

| 12.1.3 Automatic Mode                                      |      |

| 12.1.3.1 Automatic Reference Switching Without Preferences | . 39 |

| 12.1.3.2 Automatic Reference Switching With Preferences    |      |

| 12.1.4 Freerun Mode                                        |      |

| 13.0 DPLL Frequency Behaviour                              |      |

| 13.1 Input Frequencies                                     |      |

| 13.2 Input Frequencies Selection                           |      |

| 13.3 Output Frequencies                                    |      |

| 13.4 Pull-In/Hold-In Range (also called Locking Range)     |      |

| 14.0 Jitter Performance                                    |      |

| 14.1 Input Clock Cycle to Cycle Timing Variation Tolerance |      |

| 14.2 Input Jitter Acceptance                               |      |

| 14.3 Jitter Transfer Function                              |      |

| 15.0 DPLL Specific Functions and Requirements              |      |

| 15.1 Lock Detector                                         |      |

|                                                            |      |

## **Table of Contents**

| 15.2 Maximum Time Interval Error (MTIE)               | 44 |

|-------------------------------------------------------|----|

| 15.3 Phase Alignment Speed (Phase Slope)              |    |

| 15.4 Reference Monitoring                             |    |

| 15.5 Single Period Reference Monitoring               | 45 |

| 15.6 Multiple Period Reference Monitoring             | 45 |

| 16.0 Microprocessor Port                              | 46 |

| 17.0 Device Reset and Initialization                  | 46 |

| 17.1 Power-up Sequence                                |    |

| 17.2 Device Initialization on Reset                   |    |

| 17.3 Software Reset                                   |    |

| 18.0 Pseudo random Bit Generation and Error Detection | 47 |

| 19.0 PCM A-law/μ-law Translation                      | 48 |

| 20.0 Quadrant Frame Programming                       |    |

| 21.0 JTAG Port                                        |    |

| 21.1 Test Access Port (TAP)                           |    |

| 21.2 Instruction Register                             |    |

| 21.3 Test Data Registers                              |    |

| 21.4 BSDL                                             | 50 |

| 22.0 Register Address Mapping                         | 51 |

| 23.0 Detailed Register Description                    | 53 |

| 24.0 Memory                                           | 86 |

| 24.1 Memory Address Mappings                          |    |

| 24.2 Connection Memory Low (CM_L) Bit Assignment      |    |

| 24.3 Connection Memory High (CM_H) Bit Assignment     |    |

| 25.0 Applications                                     |    |

| 25.1 OSCi Master Clock Requirement                    |    |

| 25.1.1 External Crystal Oscillator                    |    |

| 25.1.2 External Clock Oscillator                      |    |

| 26.0 DC Parameters                                    | 92 |

| 27.0 AC Parameters                                    | 03 |

Data Sheet

## **List of Figures**

| Figure 1 7 F001F Functional Plack Diagram                                         | 4   |

|-----------------------------------------------------------------------------------|-----|

| Figure 1 - ZL50015 Functional Block Diagram                                       |     |

| Figure 2 - ZL50015 256-Ball 17 mm x 17 mm PBGA (as viewed through top of package) |     |

| Figure 3 - ZL50015 256-Lead 28 mm x 28 mm LQFP (top view)                         |     |

| Figure 4 - Input Timing when CKIN1 - 0 bits = "10" in the CR                      |     |

| Figure 5 - Input Timing when CKIN1 - 0 bits = "01" in the CR                      |     |

| Figure 6 - Input Timing when CKIN1 - 0 = "00" in the CR                           |     |

| Figure 7 - Output Timing for CKo0 and FPo0                                        |     |

| Figure 8 - Output Timing for CKo1 and FPo1                                        |     |

| Figure 9 - Output Timing for CKo2 and FPo2                                        |     |

| Figure 10 - Output Timing for CKo3 and FPo3 with CKoFPo3SEL1-0="11"               |     |

| Figure 11 - Output Timing for CKo4                                                |     |

| Figure 12 - Output Timing for CKo5 and FPo5 (FPo_OFF2)                            |     |

| Figure 13 - Input Bit Delay Timing Diagram (ST-BUS)                               |     |

| Figure 14 - Input Bit Sampling Point Programming                                  |     |

| Figure 15 - Input Bit Delay and Factional Sampling Point                          |     |

| Figure 16 - Output Bit Advancement Timing Diagram (ST-BUS)                        |     |

| Figure 17 - Output Fractional Bit Advancement Timing Diagram (ST-BUS)             | 32  |

| Figure 18 - Channel Switching External High Impedance Control Timing              | 33  |

| Figure 19 - Data Throughput Delay for Variable Delay                              |     |

| Figure 20 - Data Throughput Delay for Constant Delay                              | 35  |

| Figure 21 - No Preferred Reference (Round Robin) with Ref 0-3 available           | 39  |

| Figure 22 - Automatic Reference Switching State Diagrams with Preferred Reference | 41  |

| Figure 23 - Crystal Oscillator Circuit                                            | 90  |

| Figure 24 - Clock Oscillator Circuit                                              | 91  |

| Figure 25 - Timing Parameter Measurement Voltage Levels                           |     |

| Figure 26 - Motorola Non-Multiplexed Bus Timing - Read Access                     | 94  |

| Figure 27 - Motorola Non-Multiplexed Bus Timing - Write Access                    | 95  |

| Figure 28 - Intel Non-Multiplexed Bus Timing - Read Access                        | 96  |

| Figure 29 - Intel Non-Multiplexed Bus Timing - Write Access                       | 97  |

| Figure 30 - JTAG Test Port Timing Diagram                                         | 98  |

| Figure 31 - Frame Pulse Input and Clock Input Timing Diagram (ST-BUS)             | 100 |

| Figure 32 - Frame Pulse Input and Clock Input Timing Diagram (GCI-Bus)            | 100 |

| Figure 33 - ST-BUS Input Timing Diagram when Operated at 2 Mbps, 4 Mbps, 8 Mbps   | 101 |

| Figure 34 - ST-BUS Input Timing Diagram when Operated at 16 Mbps                  |     |

| Figure 35 - GCI-Bus Input Timing Diagram when Operated at 2 Mbps, 4 Mbps, 8 Mbps  |     |

| Figure 36 - GCI-Bus Input Timing Diagram when Operated at 16 Mbps                 |     |

| Figure 37 - ST-BUS Output Timing Diagram when Operated at 2, 4, 8 or 16 Mbps      |     |

| Figure 38 - GCI-Bus Output Timing Diagram when Operated at 2, 4, 8 or 16 Mbps     |     |

| Figure 39 - Serial Output and External Control                                    |     |

| Figure 40 - Output Drive Enable (ODE)                                             |     |

| Figure 41 - Input and Output Frame Boundary Offset                                |     |

| Figure 42 - FPo0 and CKo0 or FPo3 and CKo3 (4.096 MHz) Timing Diagram             | 108 |

| Figure 43 - FPo1 and CKo1 or FPo3 and CKo3 (8.192 MHz) Timing Diagram             |     |

| Figure 44 - FPo2 and CKo2 or FPo3 and CKo3 (16.384 MHz) Timing Diagram            |     |

| Figure 45 - FPo3 and CKo3 (32.768 MHz) Timing Diagram                             |     |

| Figure 46 - FPo4 and CKo4 Timing Diagram (1.544/2.048 MHz)                        |     |

| Figure 47 - CKo5 Timing Diagram (19.44 MHz)                                       |     |

| Figure 48 - REF0 - 3 Reference Input/Output Timing                                |     |

| · · · · · · · · · · · · · · · · · · ·                                             |     |

| 7 | L50 | 10      | 15 |

|---|-----|---------|----|

| _ | 느   | $\cdot$ | 10 |

| ata | a Sh | 10 | Δt |

|-----|------|----|----|

|     |      |    |    |

| Lis | t c  | of F | ini | ırΔ | e |

|-----|------|------|-----|-----|---|

| LIO | יו ע | и г  | านเ | uie | 3 |

| Eiguro | 10 (   | Jutout | Timina  | (ST-BUS | Earmat) |    |      |      |      |      |      |      |      |      |      |      | 44  | 6 |

|--------|--------|--------|---------|---------|---------|----|------|------|------|------|------|------|------|------|------|------|-----|---|

| rigure | 49 - ( | Juipui | Hilling | (31-003 | ronnai, | ٠. | <br> | -11 | O |

## **List of Tables**

| Table 1 - CKi and FPi Configurations for Master and Divided Slave Modes   | . 22 |

|---------------------------------------------------------------------------|------|

| Table 2 - CKi and FPi Configurations for Multiplied Slave Mode            | . 22 |

| Table 3 - Output Timing Generation                                        |      |

| Table 4 - Delay for Variable Delay Mode                                   |      |

| Table 5 - Connection Memory Low After Block Programming                   |      |

| Table 6 - Connection Memory High After Block Programming                  |      |

| Table 7 - ZL50015 Operating Modes                                         |      |

| Table 8 - Preferred Reference Selection Options                           |      |

| Table 9 - DPLL Input Reference Frequencies                                |      |

| Table 10 - Generated Output Frequencies                                   |      |

| Table 11 - Values for Single Period Limits                                |      |

| Table 12 - Multi-Period Hysteresis Limits                                 |      |

| Table 13 - Input and Output Voice and Data Coding                         |      |

| Table 14 - Definition of the Four Quadrant Frames                         |      |

| Table 15 - Quadrant Frame Bit Replacement                                 |      |

| Table 16 - Address Map for Registers (A13 = 0)                            |      |

| Table 17 - Control Register (CR) Bits                                     |      |

| Table 18 - Internal Mode Selection Register (IMS) Bits                    |      |

| Table 19 - Software Reset Register (SRR) Bits                             |      |

| Table 20 - Output Clock and Frame Pulse Control Register (OCFCR) Bits     |      |

| Table 21 - Output Clock and Frame Pulse Selection Register (OCFSR) Bits   |      |

| Table 22 - FPo_OFF[n] Register (FPo_OFF[n]) Bits                          |      |

| Table 24 - BER Error Flag Register 0 (BERFR0) Bits - Read Only            |      |

| Table 25 - BER Receiver Lock Register 0 (BERLR0) Bits - Read Only         |      |

| Table 26 - DPLL Control Register (DPLLCR) Bits                            |      |

| Table 27 - Reference Frequency Register (RFR) Bits                        |      |

| Table 28 - Centre Frequency Register - Lower 16 Bits (CFRL)               |      |

| Table 29 - Centre Frequency Register - Upper 10 Bits (CFRU)               |      |

| Table 30 - Frequency Offset Register (FOR) Bits - Read Only               |      |

| Table 31 - Lock Detector Threshold Register (LDTR) Bits                   |      |

| Table 32 - Lock Detector Interval Register (LDIR) Bits                    |      |

| Table 33 - Slew Rate Limit Register (SRLR) Bits                           |      |

| Table 34 - Reference Change Control Register (RCCR) Bits                  |      |

| Table 35 - Reference Change Status Register (RCSR) Bits - Read Only       |      |

| Table 36 - Interrupt Register (IR) Bits - Read Only                       | . 72 |

| Table 37 - Interrupt Mask Register (IMR) Bits                             | . 73 |

| Table 38 - Interrupt Clear Register (ICR) Bits                            | . 73 |

| Table 39 - Reference Failure Status Register (RSR) Bits - Read Only       | . 74 |

| Table 40 - Reference Mask Register (RMR) Bits                             |      |

| Table 41 - Reference Frequency Status Register (RFSR) Bits - Read only    | . 77 |

| Table 42 - Output Jitter Control Register (OJCR) Bits                     |      |

| Table 43 - Stream Input Control Register 0 - 15 (SICR0 - 15) Bits         |      |

| Table 44 - Stream Input Quadrant Frame Register 0 - 15 (SIQFR0 - 15) Bits |      |

| Table 45 - Stream Output Control Register 0 - 15 (SOCR0 - 15) Bits        |      |

| Table 46 - BER Receiver Start Register [n] (BRSR[n]) Bits                 |      |

| Table 47 - BER Receiver Length Register [n] (BRLR[n]) Bits                |      |

| Table 48 - BER Receiver Control Register [n] (BRCR[n]) Bits               | . 85 |

|                                                                           |      |

## **List of Tables**

| Table 49 - BER Receiver Error Register [n] (BRER[n]) Bits - Read Only | . 85 |

|-----------------------------------------------------------------------|------|

| Table 50 - Address Map for Memory Locations (A13 = 1)                 | . 86 |

| Table 51 - Connection Memory Low (CM_L) Bit Assignment when CMM = 0   | . 87 |

| Table 52 - Connection Memory Low (CM_L) Bit Assignment when CMM = 1   | . 88 |

| Table 53 - Connection Memory High (CM, H) Bit Assignment              | 89   |

### **Changes Summary**

The following table captures the changes from the January 2006 issue.

| Page | Item                 | Change                                     |

|------|----------------------|--------------------------------------------|

| 1    | Ordering Information | Removed leaded packages as per PCN notice. |

The following table captures the changes from the October 2004 issue.

| Page       | Item                                                                                                                                    | Change                                                                                                                                                                                                                                                                    |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 38, 70, 72 | Section 12.1, "DPLL Timing Modes" on<br>page 38<br>RCCR Register bits "FDM1 - 0" on page 70<br>RCCR Register bits "DPM1 - 0" on page 72 | The on-chip DPLL's normal, holdover, automatic<br>and freerun modes are now collectively referred<br>to as DPLL timing modes instead of operation<br>modes. This change is to avoid confusion with<br>the two main device operating modes; the<br>master and slave modes. |

| 39         | 12.1.3.1, "Automatic Reference Switching Without Preferences" and 12.1.3.2, "Automatic Reference Switching With Preferences"            | Section 12.1.3.1 and Section 12.1.3.2 added to<br>clarify the DPLL's automatic reference switching<br>with and without preference operations in<br>Automatic Timing Mode.                                                                                                 |

| 68         | Table 31, Lock Detector Threshold Register (LDTR) Bits                                                                                  | Clarified threshold calculations.                                                                                                                                                                                                                                         |

| 70         | Table 34, Reference Change Control<br>Register (RCCR) Bits                                                                              | Added description to clarify that only two<br>consecutive references can be used in<br>automatic timing mode with a preferred<br>reference.                                                                                                                               |

### 1.0 Pinout Diagrams

#### 1.1 BGA Pinout

| 1 | 1               | 2                          | 3                   | 4                          | 5                          | 6                         | 7                         | 8               | 9                          | 10                        | 11                        | 12                 | 13                 | 14                 | 15           | 16              |   |

|---|-----------------|----------------------------|---------------------|----------------------------|----------------------------|---------------------------|---------------------------|-----------------|----------------------------|---------------------------|---------------------------|--------------------|--------------------|--------------------|--------------|-----------------|---|

| Α | V <sub>SS</sub> | NC                         | NC                  | NC                         | NC                         | NC                        | NC                        | NC              | NC                         | NC                        | NC                        | NC                 | NC                 | NC                 | NC           | $V_{SS}$        | Α |

| В | NC              | STi10                      | STi5                | STi4                       | CKo2                       | STi0                      | CKo0                      | REF2            | V <sub>DD</sub> _<br>COREA | FPi                       | CKi                       | IC_Open            | IC_Open            | OSCi               | ODE          | NC              | В |

| С | NC              | STi9                       | V <sub>SS</sub>     | STi7                       | STi6                       | STi1                      | CKo1                      | REF_<br>FAIL2   | V <sub>SS</sub>            | IC_Open                   | IC_Open                   | OSCo               | IC_GND             | V <sub>SS</sub>    | STio15       | NC              | С |

| D | NC              | STi11                      | V <sub>DD_IO</sub>  | STi3                       | STi2                       | CKo4                      | REF3                      | REF1            | REF_<br>FAIL0              | V <sub>SS</sub>           | FPo_<br>OFF1              | OSC_<br>EN         | STio13             | V <sub>DD_IO</sub> | STio14       | NC              | D |

| Е | NC              | STi14                      | STi8                | V <sub>DD_IO</sub>         | V <sub>SS</sub>            | V <sub>DD</sub> _         | REF_<br>FAIL3             | REF_<br>FAIL1   | REF0                       | NC                        | V <sub>DD</sub> _<br>CORE | V <sub>SS</sub>    | V <sub>DD_IO</sub> | STio12             | FPo2         | NC              | E |

| F | NC              | STi15                      | STi12               | STi13                      | V <sub>DD_IO</sub>         | V <sub>DD</sub> _<br>CORE | V <sub>DD</sub> _<br>CORE | V <sub>SS</sub> | V <sub>SS</sub>            | V <sub>DD</sub> _<br>CORE | V <sub>DD</sub> _<br>CORE | V <sub>DD_IO</sub> | IC_Open            | FPo3               | FPo_<br>OFF2 | NC              | F |

| G | NC              | RESET                      | IC_GND              | IC_Open                    | TDo                        | V <sub>DD_IO</sub>        | V <sub>SS</sub>           | V <sub>SS</sub> | V <sub>SS</sub>            | V <sub>SS</sub>           | V <sub>DD_IO</sub>        | A12                | A13                | FPo1               | FPo0         | NC              | G |

| Н | NC              | V <sub>SS</sub>            | V <sub>SS</sub>     | V <sub>DD</sub> _<br>COREA | CKo5                       | V <sub>SS</sub>           | $V_{SS}$                  | V <sub>SS</sub> | V <sub>SS</sub>            | V <sub>SS</sub>           | A7                        | A9                 | A10                | FPo_<br>OFF0       | A11          | NC              | Н |

| J | NC              | V <sub>DD_IOA</sub>        | V <sub>DD_IOA</sub> | V <sub>SS</sub>            | V <sub>SS</sub>            | CKo3                      | V <sub>SS</sub>           | V <sub>SS</sub> | V <sub>SS</sub>            | V <sub>SS</sub>           | А3                        | A4                 | <b>A</b> 5         | A8                 | A6           | NC              | J |

| K | NC              | V <sub>SS</sub>            | TMS                 | V <sub>SS</sub>            | V <sub>DD</sub> _<br>COREA | V <sub>DD_IO</sub>        | $V_{SS}$                  | V <sub>SS</sub> | V <sub>SS</sub>            | V <sub>SS</sub>           | V <sub>DD_IO</sub>        | IC_Open            | A0                 | A2                 | A1           | NC              | K |

| L | NC              | V <sub>DD</sub> _<br>COREA | TRST                | TCK                        | V <sub>DD_IO</sub>         | V <sub>DD</sub> _<br>CORE | V <sub>DD</sub> _<br>CORE | V <sub>SS</sub> | V <sub>SS</sub>            | V <sub>DD</sub> _<br>CORE | V <sub>DD</sub> _<br>CORE | V <sub>DD_IO</sub> | STio10             | STio11             | STio9        | NC              | L |

| М | NC              | NC                         | TDi                 | D0                         | V <sub>SS</sub>            | V <sub>DD</sub> _<br>CORE | V <sub>DD</sub> _<br>CORE | D6              | D10                        | V <sub>DD</sub> _<br>CORE | V <sub>DD</sub> _<br>CORE | V <sub>SS</sub>    | MOT_<br>INTEL      | MODE_<br>4M0       | STio8        | NC              | М |

| N | NC              | NC                         | V <sub>DD_IO</sub>  | STio0                      | STOHZ3                     | D1                        | D5                        | D7              | D11                        | D13                       | R/W<br>_WR                | DTA_<br>RDY        | STio4              | V <sub>DD_IO</sub> | STOHZ5       | NC              | N |

| Р | NC              | NC                         | V <sub>SS</sub>     | STio1                      | STio3                      | STOHZ1                    | D3                        | D8              | D14                        | ĪRQ                       | STio5                     | STOHZ4             | STOHZ6             | V <sub>SS</sub>    | STOHZ7       | NC              | Р |

| R | NC              | NC                         | STOHZ0              | STio2                      | STOHZ2                     | D2                        | D4                        | D9              | D12                        | D15                       | CS                        | DS_RD              | MODE_<br>4M1       | STio6              | STio7        | NC              | R |

| Т | V <sub>SS</sub> | NC                         | NC                  | NC                         | NC                         | NC                        | NC                        | NC              | NC                         | NC                        | NC                        | NC                 | NC                 | NC                 | NC           | V <sub>SS</sub> | Т |

| 1 | 1               | 2                          | 3                   | 4                          | 5                          | 6                         | 7                         | 8               | 9                          | 10                        | 11                        | 12                 | 13                 | 14                 | 15           | 16              |   |

Note: A1 corner identified by metallized marking.

Note: Pinout is shown as viewed through top of package.

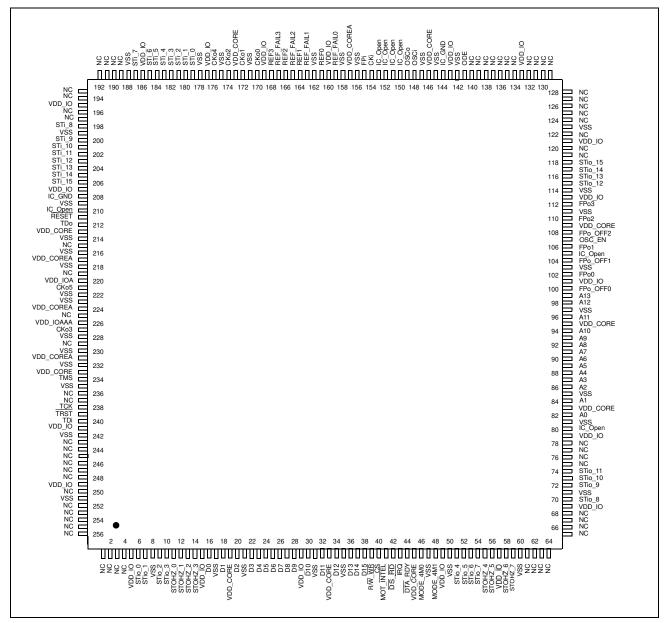

Figure 2 - ZL50015 256-Ball 17 mm x 17 mm PBGA (as viewed through top of package)

#### 1.2 QFP Pinout

Figure 3 - ZL50015 256-Lead 28 mm x 28 mm LQFP (top view)

## 2.0 Pin Description

| PBGA Pin<br>Number                                                                                                                                                                                                         | LQFP Pin<br>Number                                                                                                                                                                                                                         | Pin Name              | Description                                        |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------------------------------------------|--|

| E6, E11, F6,<br>F7, F10,<br>F11, L6, L7,<br>L10, L11,<br>M6, M7,<br>M10, M11                                                                                                                                               | 19, 33,<br>45, 83,<br>95, 109,<br>146, 173,<br>213, 233                                                                                                                                                                                    | V <sub>DD_CORE</sub>  | Power Supply for the core logic: +1.8 V            |  |

| H4, K5, B9,<br>L2                                                                                                                                                                                                          | 217, 231,<br>157, 224                                                                                                                                                                                                                      | V <sub>DD_COREA</sub> | Power Supply for analog circuitry: +1.8 V          |  |

| D3, D14, E4,<br>E13, F5,<br>F12, G6,<br>G11, K6,<br>K11, L5,<br>L12, N3,<br>N14                                                                                                                                            | 5, 15, 29,<br>49, 57,<br>69, 79,<br>101, 113,<br>121, 133,<br>143, 160,<br>169, 177,<br>186, 195,<br>207, 241,<br>249                                                                                                                      | V <sub>DD_IO</sub>    | Power Supply for I/O: +3.3 V                       |  |

| J2, J3                                                                                                                                                                                                                     | 220, 226                                                                                                                                                                                                                                   | V <sub>DD_IOA</sub>   | Power Supply for the CKo5 and CKo3 outputs: +3.3 V |  |

| A1, A16, C3,<br>C9, C14,<br>D10, E5,<br>E12, F8, F9,<br>G7, G8, G9,<br>G10, H2,<br>H3, H6, H7,<br>H8, H9,<br>H10, J4, J5,<br>J7, J8, J9,<br>J10, K2, K4,<br>K7, K8, K9,<br>K10, L8, L9,<br>M5, M12,<br>P3, P14, T1,<br>T16 | 8, 17, 21,<br>31, 35,<br>47, 50,<br>60, 71,<br>81, 85,<br>97, 103,<br>111, 114,<br>123, 142,<br>145, 147,<br>156, 158,<br>162, 171,<br>175, 178,<br>188, 199,<br>209, 214,<br>216, 218,<br>222, 223,<br>228, 230,<br>232, 235,<br>242, 251 | V <sub>SS</sub>       | Ground                                             |  |

| PBGA Pin<br>Number                        | LQFP Pin<br>Number                        | Pin Name | Description                                                                                                                                                                                                                                                                                                                                         |  |

|-------------------------------------------|-------------------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| K3                                        | 234                                       | TMS      | Test Mode Select (5 V-Tolerant Input with Internal Pull-up) JTAG signal that controls the state transitions of the TAP controller. This pin is pulled high by an internal pull-up resistor when it is not driven.                                                                                                                                   |  |

| L4                                        | 238                                       | TCK      | Test Clock (5 V-Tolerant Schmitt-Triggered Input with Internal Pull-up) Provides the clock to the JTAG test logic.                                                                                                                                                                                                                                  |  |

| L3                                        | 239                                       | TRST     | Test Reset (5 V-Tolerant Input with Internal Pull-up) Asynchronously initializes the JTAG TAP controller by putting it in the Test-Logic-Reset state. This pin should be pulsed low during power-up to ensure that the device is in the normal functional mode. When JTAG is not being used, this pin should be pulled low during normal operation. |  |

| M3                                        | 240                                       | TDi      | Test Serial Data In (5 V-Tolerant Input with Internal Pull-up) JTAG serial test instructions and data are shifted in on this pin. This pin is pulled high by an internal pull-up resistor when it is not driven.                                                                                                                                    |  |

| G5                                        | 212                                       | TDo      | Test Serial Data Out (5 V-Tolerant Three-state Output) JTAG serial data is output on this pin on the falling edge of TCK. This pin is held in high impedance state when JTAG is not enabled.                                                                                                                                                        |  |

| B12, B13,<br>C10, C11,<br>F13, G4,<br>K12 | 80, 105,<br>150, 151,<br>152, 153,<br>210 | IC_Open  | Internal Test Mode (5 V-Tolerant Input with Internal Pull-down) These pins may be left unconnected.                                                                                                                                                                                                                                                 |  |

| C13, G3                                   | 144, 208                                  | IC_GND   | Internal Test Mode Enable (5 V-Tolerant Input) These pins MUST be low.                                                                                                                                                                                                                                                                              |  |

| PBGA Pin<br>Number | LQFP Pin<br>Number | Pin Name              | Description                                                                                                                                                                                                                                                                                                                                                       |  |

|--------------------|--------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| A8, A9, A14,       | 61, 62,            | NC                    | No Connect                                                                                                                                                                                                                                                                                                                                                        |  |

| A15, E10,          | 63, 64,            |                       | These pins MUST be left unconnected.                                                                                                                                                                                                                                                                                                                              |  |

| M2, N2, P2,        | 65, 66,            |                       |                                                                                                                                                                                                                                                                                                                                                                   |  |

| P16, R2,           | 67, 68,            |                       |                                                                                                                                                                                                                                                                                                                                                                   |  |

| R16, T6, T7,       | 134, 135,          |                       |                                                                                                                                                                                                                                                                                                                                                                   |  |

| T8, T9, T10,       | 136, 137,          |                       |                                                                                                                                                                                                                                                                                                                                                                   |  |

| T11, T12,          | 138, 139,          |                       |                                                                                                                                                                                                                                                                                                                                                                   |  |

| T13, T14,          | 140, 215,          |                       |                                                                                                                                                                                                                                                                                                                                                                   |  |

| T15, D16,          | 219, 225,          |                       |                                                                                                                                                                                                                                                                                                                                                                   |  |

| E16, C16,          | 229, 236,          |                       |                                                                                                                                                                                                                                                                                                                                                                   |  |

| B16, A13,          | 237, 125,          |                       |                                                                                                                                                                                                                                                                                                                                                                   |  |

| A12, A10,          | 126, 127,          |                       |                                                                                                                                                                                                                                                                                                                                                                   |  |

| A11, N1,           | 128, 129,          |                       |                                                                                                                                                                                                                                                                                                                                                                   |  |

| M1, P1, R1,        | 130, 131,          |                       |                                                                                                                                                                                                                                                                                                                                                                   |  |

| T2, T3, T5,        | 132, 253,          |                       |                                                                                                                                                                                                                                                                                                                                                                   |  |

| T4, N16,           | 254, 255,          |                       |                                                                                                                                                                                                                                                                                                                                                                   |  |

| M16, L16,          | 256, 1, 2,         |                       |                                                                                                                                                                                                                                                                                                                                                                   |  |

| K16, H16,          | 3, 4, 75,          |                       |                                                                                                                                                                                                                                                                                                                                                                   |  |

| J16, G16,          | 76, 77,            |                       |                                                                                                                                                                                                                                                                                                                                                                   |  |

| F16, E1, D1,       | 78, 119,           |                       |                                                                                                                                                                                                                                                                                                                                                                   |  |

| G1, F1, J1,        | 120, 122,          |                       |                                                                                                                                                                                                                                                                                                                                                                   |  |

| H1, K1, L1,        | 124, 243,          |                       |                                                                                                                                                                                                                                                                                                                                                                   |  |

| A7, A5, A6,        | 244, 245,          |                       |                                                                                                                                                                                                                                                                                                                                                                   |  |

| A4, A3, A2,        | 246, 247,          |                       |                                                                                                                                                                                                                                                                                                                                                                   |  |

| C1, B1             | 248, 250,          |                       |                                                                                                                                                                                                                                                                                                                                                                   |  |

|                    | 252, 189,          |                       |                                                                                                                                                                                                                                                                                                                                                                   |  |

|                    | 190, 191,          |                       |                                                                                                                                                                                                                                                                                                                                                                   |  |

|                    | 192, 193,          |                       |                                                                                                                                                                                                                                                                                                                                                                   |  |

|                    | 194, 196,          |                       |                                                                                                                                                                                                                                                                                                                                                                   |  |

|                    | 197                |                       |                                                                                                                                                                                                                                                                                                                                                                   |  |

| M14, R13           | 46, 48             | MODE_4M0,<br>MODE_4M1 | 4 M Input Clock Mode 0 to 1 (5 V-Tolerant Input with internal pull-down) These two pins should be tied together and are typically used to select CKi = 4.096 MHz operation. See Table 7, "7I 50015 Operating Modes" on page 37 for a detailed explanation                                                                                                         |  |

|                    |                    |                       | "ZL50015 Operating Modes" on page 37 for a detailed explanation. See Table 17, "Control Register (CR) Bits" on page 53 for CKi and FPi selection using the CKIN1 - 0 bits.                                                                                                                                                                                        |  |

| D12                | 107                | OSC_EN                | Oscillator Enable (5 V-Tolerant Input with Internal Pull-down) If tied high, this pin indicates that there is a 20 MHz external oscillator interfacing with the device. If tied low, there is no oscillator and CKi will be used for master clock generation. If the device is in master mode, an external oscillator is required and this pin MUST be tied high. |  |

| PBGA Pin<br>Number    | LQFP Pin<br>Number    | Pin Name         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|-----------------------|-----------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| C12                   | 149                   | OSC <sub>0</sub> | Oscillator Clock Output (3.3 V Output)  If OSC_EN = '1', this pin should be connected to a 20 MHz crystal (see Figure 23 on page 90) or left unconnected if a clock oscillator is connected to OSCi pin under normal operation (see Figure 24 on page 91). If OSC_EN = 0, this pin MUST be left unconnected.                                                                                                                                                                                                                                                                                                                                                             |  |

| B14                   | 148                   | OSCi             | Oscillator Clock Input (3.3 V Input)  If OSC_EN = '1', this pin should be connected to a 20 MHz crystal (see Figure 23 on page 90) or to a clock oscillator under normal operation (see Figure 24 on page 91). If OSC_EN = 0, this pin MUST be driven high or low by connecting either to V <sub>DD_IO</sub> or to ground.                                                                                                                                                                                                                                                                                                                                               |  |

| E9, D8, B8,<br>D7     | 161, 164,<br>166, 168 | REF0 - 3         | DPLL Reference Inputs 0 to 3 (5 V-Tolerant Schmitt-Triggered Inputs)  If the device is in Master mode, these input pins accept 8 kHz, 1.544 MHz, 2.048 MHz, 4.096 MHz, 8.192 MHz, 16.384 MHz or 19.44 MHz timing references independently. One of these inputs is defined as the preferred or forced input reference for the DPLL. The Reference Change Control Register (RCCR) selects the control of the preferred reference. These pins are ignored if the device is in slave mode unless SLV_DPLLEN (bit 13) in the Control Register (CR) is set. When these input pins are not in use, they MUST be driven high or low by connecting either to VDD_IO or to ground. |  |

| D9, E8, C8,<br>E7     | 159, 163,<br>165, 167 | REF_FAIL0 - 3    | Failure Indication for DPLL References 0 to 3 (5 V-Tolerant Three-state Outputs)  These output pins are used to indicate input reference failure when the device is in master mode.  If REF0 fails, REF_FAIL0 will be driven high.  If REF1 fails, REF_FAIL1 will be driven high.  If REF2 fails, REF_FAIL2 will be driven high.  If REF3 fails, REF_FAIL3 will be driven high.  If the device is in slave mode, these pins are driven low, unless SLV_DPLLEN (bit 13) in the Control Register (CR) is set.                                                                                                                                                              |  |

| G15, G14,<br>E15, F14 | 102, 106,<br>110, 112 | FPo0 - 3         | SLV_DPLLEN (bit 13) in the Control Register (CR) is set.  ST-BUS/GCI-Bus Frame Pulse Outputs 0 to 3 (5 V-Tolerant Three-state Outputs)  FPo0: 8 kHz frame pulse corresponding to the 4.096 MHz output clock of CKo0.  FPo1: 8 kHz frame pulse corresponding to the 8.192 MHz output clock of CKo1.  FPo2: 8 kHz frame pulse corresponding to 16.384 MHz output clock of CKo2.  FPo3: Programmable 8 kHz frame pulse corresponding to 4.096 MHz, 8.192 MHz, 16.384 MHz, or 32.768 MHz output clock of CKo3.  In Divided Slave modes, the frame pulse width of FPo0 - 3 cannot be narrower than the input frame pulse (FPi) width.                                         |  |

| PBGA Pin<br>Number        | LQFP Pin<br>Number                 | Pin Name               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|---------------------------|------------------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| H14, D11                  | 100, 104                           | FPo_OFF0 - 1           | Generated Offset Frame Pulse Outputs 0 to 1 (5 V-Tolerant Three-state Outputs) Individually programmable 8 kHz frame pulses, offset from the output frame boundary by a programmable number of channels.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| F15                       | 108                                | FPo_OFF2<br>or<br>FPo5 | Generated Offset Frame Pulse Output 2 or 19.44 MHz Frame Pulse Output (5 V-Tolerant Three-state Output)  As FPo_OFF2, this is an individually programmable 8 kHz frame pulse, offset from the output frame boundary by a programmable number of channels.  By programming the FP19EN (bit 10) of FPOFF2 register to high, this signal becomes FPo5, a non-offset frame pulse corresponding to the 19.44 MHz clock presented on CKo5. FPo5 is only available in Master mode or when the SLV_DPLLEN bit in the Control Register is set high while the device is in one of the slave modes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| B7, C7, B5,<br>J6, D6, H5 | 170, 172,<br>174, 227,<br>176, 221 | CKo0 - 5               | ST-BUS/GCI-Bus Clock Outputs 0 to 5 (5 V-Tolerant Three-state Outputs)  CKo0: 4.096 MHz output clock.  CKo1: 8.192 MHz output clock.  CKo2: 16.384 MHz output clock.  CKo3: 4.096 MHz, 8.192 MHz, 16.384 MHz or 32.768 MHz programmable output clock.  CKo4: 1.544 MHz or 2.048 MHz programmable output clock.  CKo5: 19.44 MHz output clock.  See Section 6.0 on page 24 for details. In Divided Slave mode, the frequency of CKo0 - 3 cannot be higher than input clock (CKi).  CKo4 and CKo5 are only available in Master mode or when the SLV_DPLLEN bit in the Control Register is set high while the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| B10                       | 155                                | FPi                    | ST-BUS/GCI-Bus Frame Pulse Input (5 V-Tolerant Schmitt-Triggered Input)  This pin accepts the frame pulse which stays active for 61 ns 122 ns or 244 ns at the frame boundary. The frame pulse frequency is 8 kHz. The frame pulse associated with the highest input or output data rate must be applied to this pin when the device is operating in Divided Slave mode or Master mode. The exception is if the device is operating in Master mode with loopback (i.e., CKi_LP is set in the Control Register). In that case this input must be tied high or low externally. When the device is operating in Multiplied Slave mode, the frame pulse associated with the highest input data rate must be applied to this pin. For al modes (except Master mode with loopback), if the data rate is 16.384 Mbps, a 61 ns wide frame pulse must be used. By default the device accepts a negative frame pulse in ST-BUS format, but it can accept a positive frame pulse instead if the FPINP bit is see high in the Control Register (CR). It can accept a GCI-formatted frame pulse by programming the FPINPOS bit in the Control Register (CR) to high. |  |

| PBGA Pin<br>Number                                                                              | LQFP Pin<br>Number                                                                                  | Pin Name    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B11                                                                                             | 154                                                                                                 | CKi         | ST-BUS/GCI-Bus Clock Input (5 V-Tolerant Schmitt Triggered Input)  This pin accepts a 4.096 MHz, 8.192 MHz or 16.384 MHz clock. The clock frequency associated with twice the highest input or output data rate must be applied to this pin when the device is operating in either Divided Slave mode or Master mode. The exception is if the device is operating in Master mode with loopback (i.e., CKi_LP is set in the Control Register). In that case, this input must be tied high or low externally. The clock frequency associated with twice the highest input data rate must be applied to this pin when the device is operating in Multiplied Slave mode. In all modes of operation (except Master mode with loopback), when data is running at 16.384 Mbps, a 16.384 MHz clock must be used. By default, the clock falling edge defines the input frame boundary, but the device allows the clock rising edge to define the frame boundary by programming the CKINP bit in the Control Register (CR). |

| B6, C6, D5,<br>D4, B4, B3,<br>C5, C4, E3,<br>C2, B2, D2,<br>F3, F4, E2,<br>F2                   | 179, 180,<br>181, 182,<br>183, 184,<br>185, 187,<br>198, 200,<br>201, 202,<br>203, 204,<br>205, 206 | STi0 - 15   | Serial Input Streams 0 to 15 (5 V-Tolerant Inputs with Enabled Internal Pull-downs)  The data rate of each input stream can be selected independently using the Stream Input Control Registers (SICR[n]). In the 2.048 Mbps mode, these pins accept serial TDM data streams at 2.048 Mbps with 32 channels per frame. In the 4.096 Mbps mode, these pins accept serial TDM data streams at 4.096 Mbps with 64 channels per frame. In the 8.192 Mbps mode, these pins accept serial TDM data streams at 8.192 Mbps with 128 channels per frame. In the 16.384 Mbps mode, these pins accept TDM data streams at 16.384 Mbps with 256 channels per frame.                                                                                                                                                                                                                                                                                                                                                            |

| N4, P4, R4,<br>P5, N13,<br>P11, R14,<br>R15, M15,<br>L15, L13,<br>L14, E14,<br>D13, D15,<br>C15 | 6, 7, 9,<br>10, 51,<br>52, 53,<br>54, 70,<br>72, 73,<br>74, 115,<br>116, 117,<br>118                | STio 0 - 15 | Serial Output Streams 0 to 15 (5 V-Tolerant Slew-Rate-Limited Three-state I/Os with Enabled Internal Pull-downs)  The data rate of each output stream can be selected independently using the Stream Output Control Registers (SOCR[n]). In the 2.048 Mbps mode, these pins output serial TDM data streams at 2.048 Mbps with 32 channels per frame. In the 4.096 Mbps mode, these pins output serial TDM data streams at 4.096 Mbps with 64 channels per frame. In the 8.192 Mbps mode, these pins output serial TDM data streams at 8.192 Mbps with 128 channels per frame. In the 16.384 Mbps mode, these pins output serial TDM data streams at 16.384 Mbps with 256 channels per frame. These output streams can be used as bi-directionals by programming BDL (bit 6) of Internal Mode Selection (IMS) register.                                                                                                                                                                                            |

| PBGA Pin<br>Number                                                              | LQFP Pin<br>Number                                                                  | Pin Name    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|---------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| R3, P6, R5,<br>N5, P12,<br>N15, P13,<br>P15                                     | 11, 12,<br>13, 14,<br>55, 56,<br>58, 59                                             | STOHZ 0 - 7 | Serial Output Streams High Impedance Control 0 to 7 (5 V-Tolerant Slew-Rate-Limited Three-state Outputs) These pins are used to enable (or disable) external three-state buffers. When an output channel is in the high impedance state, the STOHZ drives high for the duration of the corresponding output channel. When the STio channel is active, the STOHZ drives low for the duration of the corresponding output channel. STOHZ outputs are available for STio0 - only. |  |

| B15                                                                             | 141                                                                                 | ODE         | Output Drive Enable (5 V-Tolerant Input with Internal Pull-up) This is the output enable control for STio0 - 15 and the output-driven-high control for STOHZ0 - 7. When it is high, STio0 - 15 and STOHZ0 - 7 are enabled. When it is low, STio0 - 15 are tristated and STOHZ0 - 7 are driven high.                                                                                                                                                                            |  |

| M4, N6, R6,<br>P7, R7, N7,<br>M8, N8, P8,<br>R8, M9, N9,<br>R9, N10, P9,<br>R10 | 16, 18,<br>20, 22,<br>23, 24,<br>25, 26,<br>27, 28,<br>30, 32,<br>34, 36,<br>37, 38 | D0 - 15     | Data Bus 0 to 15 (5 V-Tolerant Slew-Rate-Limited Three-state I/Os) These pins form the 16-bit data bus of the microprocessor port.                                                                                                                                                                                                                                                                                                                                             |  |

| N12                                                                             | 44                                                                                  | DTA_RDY     | Data Transfer Acknowledgment_Ready (5 V-Tolerant Three-state Output) This active low output indicates that a data bus transfer is complete for the Motorola interface. For the Intel interface, it indicates a transfer is completed when this pin goes from low to high. An external pull-up resistor MUST hold this pin at HIGH level for the Motorola mode. An external pull-down resistor MUST hold this pin at LOW level for the Intel mode.                              |  |