Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# 32 K Channel Digital Switch with High Jitter Tolerance, Rate Conversion per Group of 4 Streams (8, 16, 32 or 64 Mbps), and 128 Inputs and 128 Outputs

**Data Sheet**

January 2006

**Features**

- 32,768 channel x 32,768 channel non-blocking digital Time Division Multiplex (TDM) switch at 65.536 Mbps, 32.768 Mbps and 16.384 Mbps or using a combination of rates

- 16,384 channel x 16,384 channel non-blocking digital TDM switch at 8.192 Mbps

- High jitter tolerance with multiple input clock sources and frequencies

- Up to 128 serial TDM input streams, divided into 32 groups with 4 input streams per group

- Up to 128 serial TDM output streams, divided into 32 groups with 4 output streams per group

- Per-group input and output data rate conversion selection at 65.536 Mbps, 32.768 Mbps, 16.384 Mbps and 8.192 Mbps. Input and output data group rates can differ

- Per-group input bit delay for flexible sampling point selection

- · Per-group output fractional bit advancement

- Four sets of output timing signals for interfacing additional devices

- Per-channel A-Law/μ-Law Translation

daring Information

#### **Ordering Information**

ZL50073GAC 484 Ball PBGA Trays ZL50073GAG2 484 Ball PBGA\*\* Trays \*\*Pb Free Tin/Silver/Copper

-40°C to +85°C

- Per-channel constant or variable throughput delay for frame integrity and low latency applications

- Per-stream Bit Error Rate (BER) test circuits

- · Per-channel high impedance output control

- · Per-channel force high output control

- · Per-channel message mode

- Control interface compatible with Intel and Motorola Selectable 32 bit and 16 bit nonmultiplexed buses

- · Connection Memory block programming

- Supports ST-BUS and GCI-Bus standards for input and output timing

- IEEE 1149.1 (JTAG) test port

- 3.3 V I/O with 5 V tolerant inputs; 1.8 V core voltage

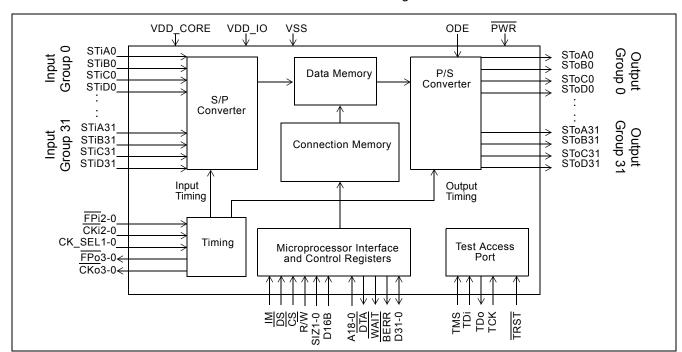

Figure 1 - ZL50073 Functional Block Diagram

#### **Applications**

- · Large Switching Platforms

- · Central Office Switches

- · Wireless Base Stations

- Multi-service Access Platforms

- · Media Gateways

#### **Description**

The ZL50073 is a non-blocking Time Division Multiplex (TDM) switch with maximum 32,768 x 32,768 channels. The device can switch 64 kbps and Nx64 kbps TDM channels from any input stream to any output stream. With a number of enhanced features, the ZL50073 is designed for high capacity voice and data switching applications.

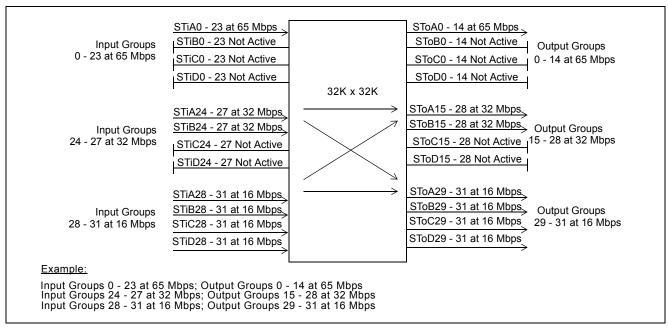

The ZL50073 has 128 input and 128 output data streams which can operate at 8.192 Mbps, 16.384 Mbps, 32.768 Mbps or 65.536 Mbps. The large number of inputs and outputs maintains full 32 K x 32 K channel switching capacity at bit rates of 65 Mbps, 32 Mbps and 16 Mbps. Up to 32 input and output data streams may operate at 65 Mbps. Up to 64 input and output data streams may operate at 32 Mbps. Up to 128 input and output data streams may operate at 16 Mbps or 8 Mbps. The data rate can be independently set in groups of 4 input or output streams. In this way it is possible to provide rate conversion from input data channel to output data channel.

The ZL50073 uses a master clock (CKi0) and frame pulse (FPi0) to define the TDM data stream frame boundary and timing. A high speed system clock is derived internally from CKi0 and FPi0. The input and output data streams can independently reference their timings to one of the input clocks or to the internal system clock.

The ZL50073 has a variety of user configurable options designed to provide flexibility when data streams are connected to multiple TDM components or circuits. These include:

- Two additional programmable reference inputs, CKi2 1 and FPi2 1, which can be used to provide alternative sources for input and output stream timing

- Variable input bit delay and output advancement, to accommodate delays and frame offsets of streams connected through different data paths

- Four timing outputs, CKo3 0 and FPo3 0, which can be configured independently to provide a variety of clock and frame pulse options

- · Support of both ST-BUS and GCI-Bus formats

The ZL50073 also has a number of value added features for voice and data applications:

- Per-channel variable delay mode for low latency applications and constant delay mode for frame integrity applications

- Per-channel A-Law/μ-Law Conversions for both voice and data

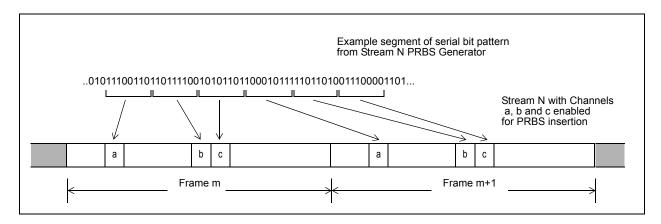

- 128 separate Pseudo-random Bit Sequence (PRBS) test circuits; one per stream. This provides an integrated Bit Error Rate (BER) test capability to facilitate data path integrity checking

The ZL50073 has two major modes of operation: Connection Mode (normal) and Message Mode. In Connection Mode, data bytes received at the TDM inputs are switched to timeslots in the output data streams, with mapping controlled by the Connection Memories. Using Zarlink's Message Mode capability, microprocessor data can be broadcast to the output data streams on a per-channel basis. This feature is useful for transferring control and status information to external circuits or other TDM devices.

A non-multiplexed microprocessor port provides access to the internal Data Memory, Connection Memory and Control Registers used to program ZL50073 options. The port is configurable to interface with either Motorola or Intel-type microprocessors and is selectable to be either 32 bit or 16 bit.

The mandatory requirements of IEEE 1149.1 standard are supported via the dedicated Test Access Port.

# **Table of Contents**

| Features                                                   |      |

|------------------------------------------------------------|------|

| Applications                                               | 2    |

| Description                                                | 2    |

| Change Summary                                             | 7    |

| 1.0 Functional Description                                 |      |

| 1.1 Overview                                               |      |

| 1.2 Switch Operation                                       | . 15 |

| 1.3 Stream Provisioning                                    |      |

| 1.4 Input and Output Rate Selection                        |      |

| 1.4.1 Per Group Rate Selection                             |      |

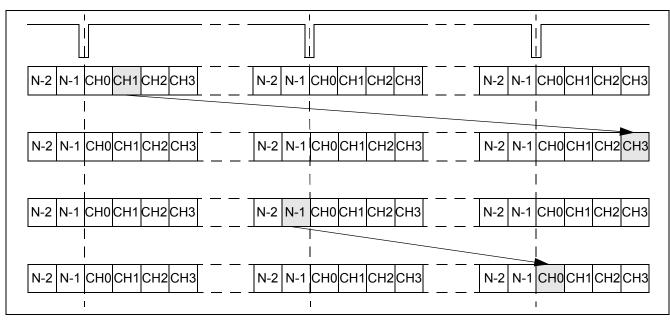

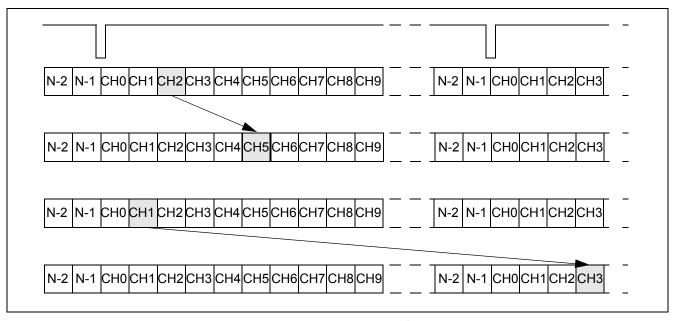

| 1.5 Rate Conversion                                        |      |

| 2.0 Input Clock (CKi) and Input Frame Pulse (FPi) Timing   |      |

| 3.0 Output Clock (CKo) and Output Frame Pulse (FPo) Timing | . 19 |

| 4.0 Output Channel Control                                 | . 19 |

| 5.0 Data Input Delay and Data Output Advancement           | . 19 |

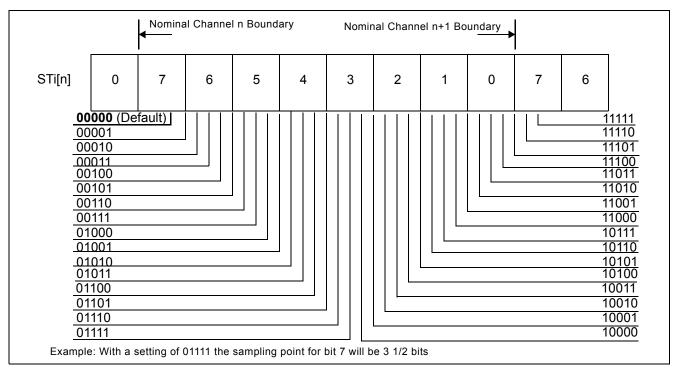

| 5.1 Input Sampling Point Delay Programming                 |      |

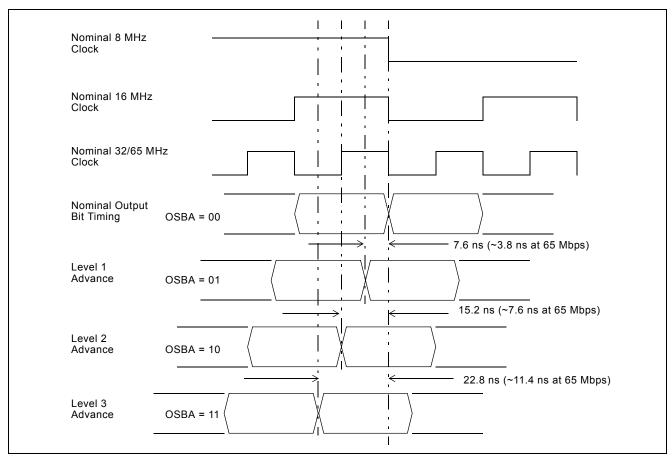

| 5.2 Fractional Bit Advancement on Output                   |      |

| 6.0 Message Mode                                           |      |

| 6.1 Data Memory Read                                       |      |

| 6.2 Connection Memory Block Programming                    |      |

| 7.0 Data Delay Through the Switching Paths                 |      |

| 7.1 Constant Delay Mode                                    |      |

| 7.2 Variable Delay Mode                                    |      |

| 8.0 Per-Channel A-Law/m-Law Translation                    |      |

| 9.0 Bit Error Rate Tester                                  |      |

| 10.0 Microprocessor Port                                   |      |

| 10.1 Addressing.                                           |      |

| 10.2 32 bit Bus Operation                                  |      |

| 10.3 16 Bit Bus Operation                                  |      |

| 10.4 Bus Operation                                         |      |

| 10.4.1 Read Cycle                                          |      |

| 10.4.2 Write Cycle                                         |      |

| 11.0 Power-up and Initialization of the ZL50073            | . 30 |

| 11.1 Device Reset and Initialization                       |      |

| 11.2 Power Supply Sequencing                               |      |

| 11.3 Initialization                                        |      |

| 12.0 IEEE 1149.1 Test Access Port                          |      |

| 12.1 Test Access Port (TAP)                                |      |

| 12.2 Instruction Register                                  |      |

| 12.3 Test Data Register                                    |      |

| 12.4 Boundary Scan Description Language (BSDL)             |      |

| 13.0 Memory Map of ZL50073                                 |      |

| 14.0 Detailed Memory and Register Descriptions             |      |

| 14.1 Connection Memory                                     |      |

| 14.1.1 Connection Memory Bit Functions                     |      |

| 14.1.2 Connection Memory LSB                               |      |

| 14.2 Data Memory                                           |      |

| 14.3 BER Control Memory and Error Counters                 |      |

| 14.3.1 Input BER Enable Control Memory                     |      |

| 14.3.2 BER Counters                                        | . 42 |

ZL50073

# **Table of Contents**

|    | 14.4 Group Control Registers       | . 43      |

|----|------------------------------------|-----------|

|    | 14.5 Input Clock Control Register  | . 47      |

|    | 14.6 Output Clock Control Register |           |

|    | 14.7 Block Init Register           | . 52      |

|    | 14.8 Block Init Enable Register    | . 52      |

| 15 | O DC/AC Electrical Characteristics | <b>53</b> |

# ZL50073

# **List of Figures**

| Figure 1 - ZL50073 Functional Block Diagram                                              | 1    |

|------------------------------------------------------------------------------------------|------|

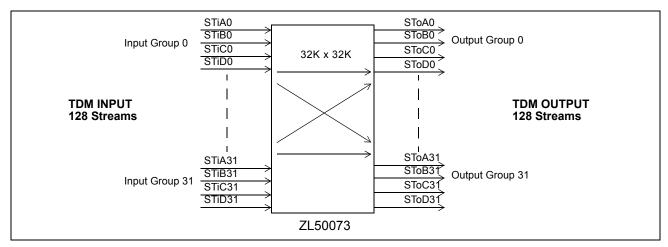

| Figure 2 - 32 K x 32 K Channel Basic Switch Configuration                                | . 15 |

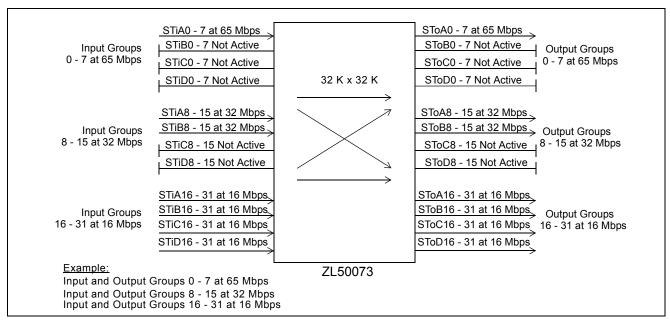

| Figure 3 - ZL50073 32 K x 32 K Channel and Stream Provisioning Example at Multiple Rates | . 17 |

| Figure 4 - Input and Output Data Rate Conversion Example                                 | . 18 |

| Figure 5 - Input Sampling Point Delay Programming                                        | . 20 |

| Figure 6 - Output Bit Advancement Timing                                                 | . 21 |

| Figure 7 - Data Throughput Delay for Constant Delay                                      | . 23 |

| Figure 8 - Data Throughput Delay for Variable Delay                                      | . 23 |

| Figure 9 - Example PRBS Timeslot Insertion                                               | . 25 |

| Figure 10 - Read Cycle Operation                                                         | . 29 |

| Figure 11 - Write Cycle Operation                                                        | . 30 |

| Figure 12 - Frame Pulse Input and Clock Input                                            | . 55 |

| Figure 13 - Frame Skew Timing Diagram                                                    | . 56 |

| Figure 14 - ST-Bus Frame Pulse and Clock Output Timing                                   | . 58 |

| Figure 15 - GCI Frame Pulse and Clock Output Timing                                      | . 58 |

| Figure 16 - Serial Data Timing to CKi                                                    | . 60 |

| Figure 17 - Serial Data Timing to CKo                                                    | . 62 |

| Figure 18 - CKo to other CKo Skew                                                        | . 63 |

| Figure 19 - Microprocessor Bus Interface Timing                                          | . 65 |

| Figure 20 - Intel Mode Timing                                                            | . 65 |

| Figure 21 - IEEE 1149.1 Test Port & PWR Reset Timing                                     | . 66 |

# ZL50073

# **List of Tables**

| Table 1 - Data Rate and Maximum Switch Size                                        | 15 |

|------------------------------------------------------------------------------------|----|

| Table 2 - TDM Stream Bit Rates                                                     |    |

| Table 3 - CKi0 and FPi0 Setting via CK_SEL1 - 0                                    | 18 |

| Table 4 - Input and Output Voice and Data Coding                                   | 24 |

| Table 5 - Example of Address and Byte Significance                                 | 26 |

| Table 6 - 32 Bit Motorola Mode Byte Addressing                                     | 26 |

| Table 7 - 32 Bit Motorola Mode Access Transfer Size                                | 26 |

| Table 8 - 32 bit Intel Mode Bus Enable Signals                                     | 26 |

| Table 9 - Byte Enable Signals                                                      | 27 |

| Table 10 - 16 Bit Mode Word Alignment                                              | 27 |

| Table 11 - 16 Bit Mode Example Byte Address                                        | 28 |

| Table 12 - Memory Map                                                              | 32 |

| Table 13 - Connection Memory Group Address Mapping                                 | 33 |

| Table 14 - Connection Memory Stream Address Offset at Various Output Rates         | 34 |

| Table 15 - Connection Memory Timeslot Address Offset Range                         | 34 |

| Table 16 - Connection Memory Bits (CMB)                                            | 35 |

| Table 17 - Connection Memory LSB Group Address Mapping                             | 37 |

| Table 18 - Connection Memory LSB Stream Address Offset at Various Output Rates     | 39 |

| Table 19 - Data Memory Group Address Mapping                                       | 40 |

| Table 20 - Data Memory Stream Address Offset at Various Output Rates               | 40 |

| Table 21 - BER Enable Control Memory Group Address Mapping                         | 41 |

| Table 22 - BER Enable Control Memory Stream Address Offset at Various Output Rates | 42 |

| Table 23 - BER Counter Group and Stream Address Mapping                            | 43 |

| Table 24 - Group Control Register Addressing                                       | 43 |

| Table 25 - Group Control Register                                                  | 44 |

| Table 26 - Input Clock Control Register                                            | 47 |

| Table 27 - Output Clock Control Register                                           | 48 |

| Table 28 - Block and Power-up Initialization Status Bits                           | 52 |

# **Change Summary**

The following table captures the changes from the April 2005 issue.

| Page | Item                                                    | Item Change                                               |  |  |  |  |  |  |

|------|---------------------------------------------------------|-----------------------------------------------------------|--|--|--|--|--|--|

| 28   | 10.4.1, "Read Cycle"                                    | Clarified WAIT signal description in Read Cycle.          |  |  |  |  |  |  |

| 29   | Figure 10 "Read Cycle Operation"                        | Corrected WAIT signal tristate timing in Read Cycle.      |  |  |  |  |  |  |

| 29   | 10.4.2, "Write Cycle"                                   | Clarified WAIT signal description in Write Cycle.         |  |  |  |  |  |  |

| 30   | Figure 11 "Write Cycle Operation"                       | Corrected WAIT signal tristate timing in write Cycle.     |  |  |  |  |  |  |

| 43   | Table 23 "BER Counter Group and Stream Address Mapping" | Corrected BER Counter Group and Stream Mapping Addresses. |  |  |  |  |  |  |

The following table captures the changes from the July 2004 issue.

| Page | Item                                                                                                                                                                                                                                                                                                               | Change                                                                                                                                                                                                                                                                    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12   | "Pin Description" - CKo0-3                                                                                                                                                                                                                                                                                         | Added special requirement for using output clock at 65.536 MHz.                                                                                                                                                                                                           |

| 13   | "Pin Description" - DTA, WAIT                                                                                                                                                                                                                                                                                      | Added more detailed description to the DTA and WAIT pins.                                                                                                                                                                                                                 |

| 54   | "AC Electrical Characteristics1 - FPi0-2 and CKi0-2 Timing"                                                                                                                                                                                                                                                        | Added t <sub>FPIS</sub> , t <sub>FPIH</sub> (input frame pulse setup and hold) maximum values.                                                                                                                                                                            |

| 56   | Figure 13 "Frame Skew Timing Diagram"                                                                                                                                                                                                                                                                              | Added FPi1,2 frame pulse to Figure "Frame Skew Timing Diagram" to clarify frame boundary skew.                                                                                                                                                                            |

| 57   | (1) "AC Electrical Characteristics1 - FPO0-3 and CKO0-3 (65.536 MHz) Timing" (2) "AC Electrical Characteristics1 - FPO0-3 and CKO0-3 (32.768 MHz) Timing" (3) "AC Electrical Characteristics1 - FPO0-3 and CKO0-3 (16.384 MHz) Timing" (4) "AC Electrical Characteristics1 - FPO0-3 and CKO0-3 (8.192 MHz) Timing" | Added CKO0-3 and FPO0-3 setup and hold parameters for all different clock rates.                                                                                                                                                                                          |

| 58   | "AC Electrical Characteristics - Output Clock Jitter Generation"                                                                                                                                                                                                                                                   | Added this table to specify CKO0-3 jitter generation.                                                                                                                                                                                                                     |

| 59   | "AC Electrical Characteristics1 - Serial<br>Data Timing2 to CKi"                                                                                                                                                                                                                                                   | (1) Values of parameters t <sub>SIPS</sub> , t <sub>SIPH</sub> , t <sub>SINS</sub> , t <sub>SINH</sub> , t <sub>SINV</sub> , t <sub>SIPZ</sub> and t <sub>SINZ</sub> are revised. (2) Separated parameter t <sub>CKD</sub> into t <sub>CKDP</sub> and t <sub>CKDN</sub> . |

| 60   | Figure 16 "Serial Data Timing to CKi"                                                                                                                                                                                                                                                                              | Added more detail to figure.                                                                                                                                                                                                                                              |

| 61   | "AC Electrical Characteristics - Serial Data Timing1 to CKo2"                                                                                                                                                                                                                                                      | Values of parameters t <sub>SOPS</sub> , t <sub>SOPH</sub> , t <sub>SONS</sub> , t <sub>SONH</sub> , t <sub>SOPZ</sub> and t <sub>SONZ</sub> are revised.                                                                                                                 |

| 62   | Figure 17 "Serial Data Timing to CKo"                                                                                                                                                                                                                                                                              | Added more detail to figure.                                                                                                                                                                                                                                              |

| 63   | "AC Electrical Characteristics - CKo to Other CKo Skew1"                                                                                                                                                                                                                                                           | Added CKO skew parameters, t <sub>CKOS</sub> .                                                                                                                                                                                                                            |

| 63   | Figure 18 "CKo to other CKo Skew"                                                                                                                                                                                                                                                                                  | Added figure to show t <sub>CKOS</sub> .                                                                                                                                                                                                                                  |

## Pin Diagram - ZL50073 23 mm x 23 mm 484 Ball PBGA (as viewed through top of package)

A1 corner identified by metallized marking.

| \  | 1            | 2               | 3            | 4            | 5            | 6                         | 7                         | 8                         | 9                         | 10                        | 11                | 12                        | 13                        | 14                | 15                        | 16                        | 17                        | 18           | 19           | 20           | 21           | 22           |

|----|--------------|-----------------|--------------|--------------|--------------|---------------------------|---------------------------|---------------------------|---------------------------|---------------------------|-------------------|---------------------------|---------------------------|-------------------|---------------------------|---------------------------|---------------------------|--------------|--------------|--------------|--------------|--------------|

| Α  | CKo<br>[0]   | STiA<br>[0]     | D[30]        | D[25]        | D[20]        | D[16]                     | D[15]                     | D[11]                     | D[7]                      | D[4]                      | D[0]              | A[18]                     | A[14]                     | A[10]             | A[7]                      | A[2]                      | A[1]                      | IC           | DTA          | PWR          | SToA<br>[31] | TCK          |

| В  | SToB<br>[1]  | STiD<br>[1]     | SToA<br>[0]  | D[31]        | D[26]        | D[21]                     | D16B                      | D[13]                     | D[9]                      | D[5]                      | D[3]              | A[17]                     | A[11]                     | A[8]              | A[6]                      | A[0]                      | BERR                      | SIZ[0]       | SToB<br>[31] | STiA<br>[31] | TDo          | STiA<br>[30] |

| С  | STiA<br>[2]  | STiA<br>[3]     | STiB<br>[1]  | STiD<br>[0]  | IM           | D[27]                     | D[22]                     | D[19]                     | D[12]                     | D[6]                      | D[1]              | A[15]                     | A[9]                      | A[3]              | R/W                       | CS                        | FPo<br>[3]                | STiD<br>[31] | TRST         | SToD<br>[30] | STiB<br>[30] | STiD<br>[29] |

| D  | STiC<br>[3]  | STiD<br>[2]     | SToC<br>[1]  | SToD<br>[0]  | SToB<br>[0]  | STiC<br>[0]               | D[28]                     | D[23]                     | D[17]                     | D[8]                      | A[16]             | A[13]                     | A[5]                      | DS                | WAIT                      | SToD<br>[31]              | STiB<br>[31]              | TDi          | SToB<br>[30] | STiC<br>[30] | SToA<br>[29] | SToD<br>[28] |

| E  | STiD<br>[4]  | SToB<br>[3]     | STiC<br>[2]  | SToA<br>[1]  | STiA<br>[1]  | SToC<br>[0]               | STiB<br>[0]               | D[24]                     | D[18]                     | D[14]                     | D[2]              | A[12]                     | A[4]                      | CKo<br>[3]        | SIZ[1]                    | STiC<br>[31]              | TMS                       | SToC<br>[30] | STiD<br>[30] | SToD<br>[29] | STiA<br>[29] | STiB<br>[28] |

| F  | SToB<br>[4]  | SToC<br>[3]     | SToB<br>[2]  | SToD<br>[1]  | STIC<br>[1]  | $V_{SS}$                  | V <sub>DD</sub> _<br>CORE | D[29]                     | V <sub>DD</sub> _         | V <sub>DD</sub> _<br>CORE | D[10]             | V <sub>DD</sub> _         | V <sub>DD</sub> _<br>CORE | SToC<br>[31]      | V <sub>DD</sub> _         | V <sub>SS</sub>           | V <sub>DD</sub> _<br>CORE | SToA<br>[30] | SToC<br>[29] | STiC<br>[29] | SToB<br>[28] | STiA<br>[28] |

| G  | SToD<br>[4]  | SToD<br>[3]     | SToD<br>[2]  | STiB<br>[2]  | FPo<br>[0]   | V <sub>DD</sub> _         | $V_{SS}$                  | V <sub>SS</sub>           | V <sub>DD</sub> _<br>CORE | V <sub>DD</sub> _         | $V_{SS}$          | V <sub>DD</sub> _<br>CORE | V <sub>DD</sub> _         | V <sub>SS</sub>   | V <sub>DD</sub> _<br>CORE | V <sub>DD</sub> _         | V <sub>SS</sub>           | SToB<br>[29] | STiB<br>[29] | STiC<br>[28] | CKi<br>[2]   | STiD<br>[27] |

| н  | STiA<br>[5]  | STiA<br>[4]     | STiD<br>[3]  | SToC<br>[2]  | SToA<br>[2]  | V <sub>DD</sub> _<br>CORE | V <sub>DD</sub> _         | V <sub>SS</sub>           | V <sub>SS</sub>           | V <sub>DD</sub> _<br>CORE | V <sub>DD</sub> _ | V <sub>SS</sub>           | V <sub>DD</sub> _<br>CORE | V <sub>DD</sub> _ | $V_{SS}$                  | V <sub>DD</sub> _<br>CORE | SToA<br>[28]              | SToC<br>[28] | STiD<br>[28] | SToD<br>[27] | STiC<br>[27] | STiA<br>[27] |

| J  | STiB<br>[5]  | CKi<br>[1]      | STiC<br>[4]  | SToA<br>[3]  | STiB<br>[3]  | V <sub>DD</sub> _         | V <sub>DD</sub> _<br>CORE | V <sub>DD</sub> _         | V <sub>SS</sub>           | V <sub>SS</sub>           | $V_{SS}$          | V <sub>SS</sub>           | V <sub>SS</sub>           | V <sub>SS</sub>   | V <sub>DD</sub> _         | $V_{SS}$                  | V <sub>DD</sub> _         | SToB<br>[27] | SToC<br>[27] | STiB<br>[27] | IC           | SToC<br>[26] |

| κ  | SToB<br>[5]  | STiD<br>[5]     | FPi<br>[1]   | SToC<br>[4]  | SToA<br>[4]  | STiB<br>[4]               | $V_{SS}$                  | V <sub>DD</sub> _<br>CORE | V <sub>SS</sub>           | $V_{SS}$                  | $V_{SS}$          | V <sub>SS</sub>           | V <sub>SS</sub>           | V <sub>SS</sub>   | V <sub>DD</sub> _<br>CORE | V <sub>DD</sub> _         | V <sub>DD</sub> _<br>CORE | SToA<br>[27] | FPi<br>[2]   | SToA<br>[26] | SToB<br>[26] | STiD<br>[26] |

| L  | ODE          | SToD<br>[5]     | SToC<br>[5]  | STiD<br>[6]  | STIC<br>[5]  | V <sub>DD</sub> _<br>CORE | V <sub>DD</sub> _         | V <sub>SS</sub>           | V <sub>SS</sub>           | $V_{SS}$                  | $V_{SS}$          | V <sub>SS</sub>           | V <sub>SS</sub>           | $V_{SS}$          | $V_{SS}$                  | V <sub>DD</sub> _<br>CORE | SToD<br>[26]              | STiC<br>[26] | STiB<br>[26] | STiA<br>[26] | SToD<br>[25] | SToC<br>[25] |

| M  | STiA<br>[6]  | STiB<br>[6]     | STiC<br>[6]  | STiC<br>[7]  | SToA<br>[5]  | V <sub>DD</sub> _         | V <sub>DD</sub> _<br>CORE | V <sub>DD</sub> _         | V <sub>SS</sub>           | V <sub>SS</sub>           | V <sub>SS</sub>   | V <sub>SS</sub>           | V <sub>SS</sub>           | V <sub>SS</sub>   | V <sub>DD</sub> _         | V <sub>SS</sub>           | V <sub>DD</sub> _         | STiA<br>[25] | STiD<br>[25] | SToB<br>[25] | SToA<br>[25] | IC           |

| N  | SToB<br>[6]  | SToC<br>[6]     | SToD<br>[6]  | SToA<br>[7]  | SToA<br>[6]  | V <sub>SS</sub>           | V <sub>SS</sub>           | V <sub>DD</sub> _<br>CORE | V <sub>SS</sub>           | V <sub>SS</sub>           | V <sub>SS</sub>   | V <sub>SS</sub>           | V <sub>SS</sub>           | V <sub>SS</sub>   | V <sub>DD</sub> _<br>CORE | V <sub>DD</sub> _         | SToD<br>[23]              | SToC<br>[24] | STiD<br>[24] | SToB<br>[24] | STiB<br>[25] | STiC<br>[25] |

| Р  | STiA<br>[7]  | STiB<br>[7]     | SToB<br>[7]  | STiA<br>[8]  | SToA<br>[8]  | V <sub>DD</sub> _<br>CORE | V <sub>DD</sub> _         | V <sub>DD</sub> _         | V <sub>SS</sub>           | V <sub>SS</sub>           | V <sub>SS</sub>   | V <sub>SS</sub>           | V <sub>SS</sub>           | V <sub>SS</sub>   | V <sub>DD</sub> _         | V <sub>DD</sub> _<br>CORE | V <sub>DD</sub> _<br>CORE | SToA<br>[23] | STiC<br>[23] | STiB<br>[24] | SToA<br>[24] | SToD<br>[24] |

| R  | STiD<br>[7]  | SToC<br>[7]     | IC           | SToB<br>[8]  | STiB<br>[8]  | V <sub>DD</sub> _         | V <sub>DD</sub> _<br>CORE | V <sub>SS</sub>           | V <sub>SS</sub>           | V <sub>DD</sub> _<br>CORE | V <sub>DD</sub> _ | V <sub>SS</sub>           | V <sub>DD</sub> _<br>CORE | V <sub>DD</sub> _ | $V_{SS}$                  | $V_{SS}$                  | V <sub>DD</sub> _         | CKo<br>[2]   | STiD<br>[22] | STiB<br>[23] | STiA<br>[24] | STiC<br>[24] |

| Т  | SToD<br>[7]  | V <sub>SS</sub> | SToC<br>[8]  | STiD<br>[9]  | STiB<br>[10] | SToD<br>[9]               | $V_{SS}$                  | V <sub>SS</sub>           | V <sub>DD</sub> _<br>CORE | V <sub>DD</sub> _         | $V_{SS}$          | V <sub>DD</sub> _<br>CORE | V <sub>SS</sub>           | V <sub>SS</sub>   | V <sub>DD</sub> _<br>CORE | V <sub>DD</sub> _         | V <sub>SS</sub>           | SToA<br>[21] | FPo<br>[2]   | SToC<br>[22] | STiD<br>[23] | SToC<br>[23] |

| U  | STiC<br>[8]  | SToD<br>[8]     | STiC<br>[9]  | STiA<br>[10] | SToC<br>[10] | V <sub>SS</sub>           | V <sub>DD</sub> _         | SToC<br>[12]              | V <sub>DD</sub> _         | V <sub>DD</sub> _<br>CORE | STiA<br>[16]      | V <sub>DD</sub> _         | V <sub>DD</sub> _<br>CORE | SToA<br>[18]      | V <sub>DD</sub> _         | STiC<br>[19]              | V <sub>DD</sub> _<br>CORE | SToC<br>[20] | STiD<br>[21] | STiC<br>[22] | SToD<br>[22] | SToB<br>[23] |

| ٧  | STiD<br>[8]  | STiB<br>[9]     | SToC<br>[9]  | SToB<br>[10] | SToD<br>[10] | SToB<br>[11]              | STiC<br>[12]              | STiB<br>[13]              | SToA<br>[13]              | STiC<br>[15]              | SToB<br>[16]      | SToC<br>[16]              | IC                        | CK_<br>SEL[1]     | STiB<br>[18]              | SToA<br>[19]              | STiA<br>[20]              | SToB<br>[20] | SToD<br>[20] | SToC<br>[21] | SToA<br>[22] | STiA<br>[23] |

| w  | STiA<br>[9]  | SToB<br>[9]     | STiD<br>[10] | STiA<br>[11] | SToA<br>[11] | STiB<br>[12]              | SToD<br>[12]              | STiC<br>[13]              | STiA<br>[14]              | SToD<br>[14]              | SToC<br>[15]      | CKi<br>[0]                | IC                        | SToB<br>[17]      | CK_<br>SEL[0]             | SToC<br>[18]              | STiD<br>[19]              | SToD<br>[19] | STiD<br>[20] | STiC<br>[21] | STiA<br>[22] | SToB<br>[22] |

| Y  | SToA<br>[9]  | SToA<br>[10]    | STiB<br>[11] | SToC<br>[11] | SToA<br>[12] | FPo<br>[1]                | STiD<br>[13]              | STiB<br>[14]              | SToB<br>[14]              | STiD<br>[15]              | SToD<br>[15]      | SToD<br>[16]              | IC                        | STiC<br>[17]      | SToC<br>[17]              | STiA<br>[18]              | SToB<br>[18]              | STiB<br>[19] | STiB<br>[20] | SToA<br>[20] | SToB<br>[21] | STiB<br>[22] |

| AA | STiC<br>[10] | STiC<br>[11]    | SToD<br>[11] | STiD<br>[12] | STiA<br>[13] | SToB<br>[13]              | SToD<br>[13]              | SToA<br>[14]              | STiA<br>[15]              | SToA<br>[15]              | STiB<br>[16]      | SToA<br>[16]              | FPi<br>[0]                | STiA<br>[17]      | SToA<br>[17]              | IC                        | IC                        | SToD<br>[18] | SToB<br>[19] | SToC<br>[19] | STiA<br>[21] | SToD<br>[21] |

| АВ | STiD<br>[11] | STiA<br>[12]    | SToB<br>[12] | CKo<br>[1]   | SToC<br>[13] | STiC<br>[14]              | STiD<br>[14]              | SToC<br>[14]              | STiB<br>[15]              | SToB<br>[15]              | STiC<br>[16]      | STiD<br>[16]              | NC                        | NC                | STiB<br>[17]              | STiD<br>[17]              | SToD<br>[17]              | STiC<br>[18] | STiD<br>[18] | STiA<br>[19] | STiC<br>[20] | STiB<br>[21] |

## **Pin Description**

| Pin                                                                                                                                                                                                                                                                                                                      | Name                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                          |                      | TDM Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| F7, F10, F13, F17, G9, G12,<br>G15, H6, H10, H13, H16, J7,<br>K8, K15, K17, L6, L16, M7,<br>N8, N15, P6, P16, P17, R7,<br>R10, R13, T9, T12, T15,<br>U10, U13, U17                                                                                                                                                       | V <sub>DD_CORE</sub> | Power Supply for the Core Logic: +1.8 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| F9, F12, F15, G6, G10, G13, G16, H7, H11, H14, J6, J8, J15, J17, K16, L7, M6, M8, M15, M17, N16, P7, P8, P15, R6, R11, R14, R17, T10, T16, U7, U9, U12, U15                                                                                                                                                              | V <sub>DD_IO</sub>   | Power Supply for the I/O: +3.3 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| F6, F16, G7, G8, G11, G14, G17, H8, H9, H12, H15, J9, J10, J11, J12, J13, J14, J16, K7, K9, K10, K11, K12, K13, K14, L8, L9, L10, L11, L12, L13, L14, L15, M9, M10, M11, M12, M13, M14, M16, N6, N7, N9, N10, N11, N12, N13, N14, P9, P10, P11, P12, P13, P14, R8, R9, R12, R15, R16, T2, T7, T8, T11, T13, T14, T17, U6 | V <sub>SS</sub>      | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| A2, E5, C1, C2, H2, H1, M1,<br>P1, P4, W1, U4, W4, AB2,<br>AA5, W9, AA9, U11, AA14,<br>Y16, AB20, V17, AA21,<br>W21, V22, R21, M18, L20,<br>H22, F22, E21, B22, B20                                                                                                                                                      | STiA0-31             | Serial TDM Input Data 'A' Streams (5 V Tolerant Input with Internal Pull-down) The data rate of these input streams can be selected in a group of 4 to be either 8.192 Mbps, 16.384 Mbps, 32.678 Mbps or 65.536 Mbps. Refer to Section 1.4 for rate programming options. The data streams can be selected to be either inverted or non-inverted, programmed by the Group Control Registers (Section 14.4). Unused inputs are pulled low by internal pull-down resistors and may be left unconnected.                                                      |

| E7, C3, G4, J5, K6, J1, M2, P2, R5, V2, T5, Y3, W6, V8, Y8, AB9, AA11, AB15, V15, Y18, Y19, AB22, Y22, R20, P20, N21, L19, J20, E22, G19, C21, D17                                                                                                                                                                       | STiB0-31             | Serial TDM Input Data 'B' Streams (5 V Tolerant Input with Internal Pull-down)  The data rate of these input streams can be selected in a group of 4 to be either 8.192 Mbps, 16.384 Mbps or 32.678 Mbps. The stream is unused when its input group rate is 65.536 Mbps. Refer to Section 1.4 for rate programming options.  The data streams can be selected to be either inverted or non-inverted, programmed by the Group Control Registers (Section 14.4).  Unused inputs are pulled low by internal pull-down resistors and may be left unconnected. |

| Pin                                                                                                                                                                  | Name     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D6, F5, E3, D1, J3, L5, M3, M4, U1, U3, AA1, AA2, V7, W8, AB6, V10, AB11, Y14, AB18, U16, AB21, W20, U20, P19, R22, N22, L18, H21, G20, F20, D20, E16                | STiC0-31 | Serial TDM Input Data 'C' Streams (5 V Tolerant Input with Internal Pull-down)  The data rate of these input streams can be selected in a group of 4 to be either 8.192 Mbps or 16.384 Mbps. The stream is unused when its input group rate is 65.536 Mbps or 32.678 Mbps. Refer to Section 1.4 for rate programming options.  The data streams can be selected to be either inverted or non-inverted, programmed by the Group Control Registers (Section 14.4).  Unused inputs are pulled low by internal pull-down resistors and may be left unconnected. |

| C4, B2, D2, H3, E1, K2, L4,<br>R1, V1, T4, W3, AB1, AA4,<br>Y7, AB7, Y10, AB12, AB16,<br>AB19, W17, W19, U19, R19,<br>T21, N19, M19, K22, G22,<br>H19, C22, E19, C18 | STiD0-31 | Serial TDM Input Data 'D' Streams (5 V Tolerant Input with Internal Pull-down)  The data rate of these input streams can be selected in a group of 4 to be either 8.192 Mbps or 16.384 Mbps. The stream is unused when its input group rate is 65.536 Mbps or 32.678 Mbps. Refer to Section 1.4 for rate programming options.  The data streams can be selected to be either inverted or non-inverted, programmed by the Group Control Registers (Section 14.4).  Unused inputs are pulled low by internal pull-down resistors and may be left unconnected. |

| B3, E4, H5, J4, K5, M5, N5, N4, P5, Y1, Y2, W5, Y5, V9, AA8, AA10, AA12, AA15, U14, V16, Y20, T18, V21, P18, P21, M21, K20, K18, H17, D21, F18, A21                  | SToA0-31 | Serial TDM Output Data 'A' Streams (5 V Tolerant, 3.3 V Tri-state Slew-Rate Controlled Outputs)  The data rate of these output streams can be selected in a group of 4 to be either 8.192 Mbps, 16.384 Mbps, 32.678 Mbps or 65.536 Mbps. Refer to Section 1.4 for rate programming options. The data streams can be selected to be either inverted or non-inverted, programmed by the Group Control Registers (Section 14.4).                                                                                                                               |

| D5, B1, F3, E2, F1, K1, N1,<br>P3, R4, W2, V4, V6, AB3,<br>AA6, Y9, AB10, V11, W14,<br>Y17, AA19, V18, Y21, W22,<br>U22, N20, M20, K21, J18,<br>F21, G18, D19, B19   | SToB0-31 | Serial TDM Output Data 'B' Streams (5 V Tolerant, 3.3 V Tri-state Slew-Rate Controlled Outputs)  The data rate of these output streams can be selected in a group of 4 to be either 8.192 Mbps, 16.384 Mbps or 32.678 Mbps. The stream is unused when its output group rate is 65.536 Mbps. Refer to Section 1.4 for rate programming options.  The data streams can be selected to be either inverted or non-inverted, programmed by the Group Control Registers (Section 14.4).  Unused outputs are tristated and may be left unconnected.                |

| E6, D3, H4, F2, K4, L3, N2,<br>R2, T3, V3, U5, Y4, U8,<br>AB5, AB8, W11, V12, Y15,<br>W16, AA20, U18, V20, T20,<br>T22, N18, L22, J22, J19,<br>H18, F19, E18, F14    | SToC0-31 | Serial TDM Output Data 'C' Streams (5 V Tolerant, 3.3 V Tri-state Slew-Rate Controlled Outputs)  The data rate of these output streams can be selected in a group of 4 to be either 8.192 Mbps or 16.384 Mbps. The stream is unused when its output group rate is 65.536 Mbps or 32.678 Mbps. Refer to Section 1.4 for rate programming options.  The data streams can be selected to be either inverted or non-inverted, programmed by the Group Control Registers (Section 14.4).  Unused outputs are tristated and may be left unconnected.              |

| Pin                                                                                                                                                                  | Name     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D4, F4, G3, G2, G1, L2, N3,<br>T1, U2, T6, V5, AA3, W7,<br>AA7, W10, Y11, Y12, AB17,<br>AA18, W18, V19, AA22,<br>U21, N17, P22, L21, L17,<br>H20, D22, E20, C20, D16 | SToD0-31 | Serial TDM Output Data 'D' Streams (5 V Tolerant, 3.3 V Tri-state Slew-Rate Controlled Outputs)  The data rate of these output streams can be selected in a group of 4 to be either 8.192 Mbps or 16.384 Mbps. The stream is unused when its output group rate is 65.536 Mbps or 32.678 Mbps. Refer to Section 1.4 for rate programming options.  The data streams can be selected to be either inverted or non-inverted, programmed by the Group Control Registers (Section 14.4).  Unused outputs are tristated and may be left unconnected. |

| W12                                                                                                                                                                  | CKi0     | ST-BUS/GCI-Bus Clock Input (5 V Tolerant Schmitt-Triggered Input)  This pin accepts an 8.192 MHz, 16.384 MHz, 32.678 MHz or 65.536 MHz clock. This clock must be provided for correct operation of the ZL50073. The frequency of the CKi0 input is selected by the CK_SEL1-0 inputs. The active clock edge may be either rising or falling, programmed by the Input Clock Control Register (Section 14.5).                                                                                                                                     |

| AA13                                                                                                                                                                 | FPi0     | ST-BUS/GCI-Bus Frame Pulse Input (5 V Tolerant Input) This pin accepts the 8 kHz frame pulse which marks the frame boundary of the TDM data streams. The pulse width is nominally one CKi0 clock period (assuming ST-BUS mode) selected by the CK_SEL1-0 inputs. The active state of the frame pulse may be either high or low, programmed by the Input Clock Control Register (Section 14.5).                                                                                                                                                 |

| J2, G21                                                                                                                                                              | CKi1-2   | ST-BUS/GCI-Bus Clock Inputs (5 V Tolerant Schmitt Triggered Inputs) These optional TDM clock inputs are at 8.192 MHz, 16.384 MHz, 32.678 MHz or 65.536 MHz. The frequency of each clock input is automatically detected by the ZL50073. Refer to Section 2.0 for TDM timing options. The active clock edge may be either rising or falling, programmed by the Input Clock Control Register (Section 14.5). Unused inputs must be connected to a defined logic level.                                                                           |

| K3, K19                                                                                                                                                              | FPi1-2   | ST-BUS/GCI-Bus Frame Pulse Inputs (5 V Tolerant Inputs) These 8 kHz input pulses correspond to the optional CKi2-1 clock inputs. The frame pulses mark the frame boundary of the TDM data streams. Refer to Section 2.0 for TDM timing options. Each pulse width is nominally one CKi clock period (assuming ST-BUS mode). The active state of the frame pulse may be either high or low, programmed by the Input Clock Control Register (Section 14.5). Unused inputs must be connected to a defined logic level.                             |

| Pin                                                                                                                                                  | Name      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1, AB4, R18, E14                                                                                                                                    | CKo0-3    | ST-BUS/GCI-Bus Clock Outputs (3.3 V Outputs with Slew-Rate Control)  These clock outputs can be programmed to generate 8.192 MHz, 16.384 MHz, 32.678 MHz or 65.536 MHz TDM clock outputs. The active edge can be programmed to be either rising or falling. The source of the clock outputs can be derived from either the CKi2-0 inputs or the internal system clock. The frequency, active edge and source of each clock output can be programmed independently by the Output Clock Control Register (Section 14.6). For 65.536 MHz output clock, the total loading on the output should not be larger than 10pF. |

| G5, Y6, T19, C17                                                                                                                                     | FPo0-3    | ST-BUS/GCI-Bus Frame Pulse Outputs (3.3 V Outputs with Slew-Rate Control)  These 8 kHz output pulses mark the frame boundary of the TDM data streams. The pulse width is nominally one clock period of the corresponding CKo output. The active state of each frame pulse may be either high or low, independently programmed by the Output Clock Control Register (Section 14.6).                                                                                                                                                                                                                                  |

| W15, V14                                                                                                                                             | CK_SEL0-1 | Master Clock Input Select (5 V Tolerant Inputs) Inputs used to select the frequency and frame alignment of CKi0 and FPi0: CK_SEL1 = 0, CK_SEL0 = 0, 8.192 MHz CK_SEL1 = 0, CK_SEL0 = 1, 16.384 MHz CK_SEL1 = 1, CK_SEL0 = 0, 32.768 MHz CK_SEL1 = 1, CK_SEL0 = 1, 65.536 MHz                                                                                                                                                                                                                                                                                                                                        |

| L1                                                                                                                                                   | ODE       | Output Drive Enable (5 V Tolerant Input with Internal Pull-up) This is the asynchronous output enable control for the output streams. When it is high, the streams are enabled. When it is low, the output streams are tristated.                                                                                                                                                                                                                                                                                                                                                                                   |

| A18, J21, M22, R3, V13,<br>W13, Y13, AA16, AA17                                                                                                      | IC        | Internal Connections In normal mode these pins MUST be connected low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| AB13, AB14                                                                                                                                           | NC        | No Connection In normal mode these pins MUST be left unconnected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                      | Micr      | oprocessor Port and Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| A11, C11, E11, B11, A10,<br>B10, C10, A9, D10, B9, F11,<br>A8, C9, B8, E10, A7, A6, D9,<br>E9, C8, A5, B6, C7, D8, E8,<br>A4, B5, C6, D7, F8, A3, B4 | D0-31     | Microprocessor Port Data Bus (5 V Tolerant Bi-directional with Slew-Rate Output Control) 32 or 16 bit bidirectional data bus. Used for microprocessor access to internal memories and registers. When 16 bit mode is selected (D16B is logic 1), D31-16 are unused and must be connected to defined logic levels.                                                                                                                                                                                                                                                                                                   |

| B16, A17, A16, C14, E13,<br>D13, B15, A15, B14, C13,<br>A14, B13, E12, D12, A13,<br>C12, D11, B12, A12                                               | A0-18     | Microprocessor Port Address Bus (5 V Tolerant Inputs) 19 bit address bus for the internal memories and registers. In 16 bit bus mode (D16B is logic 1), please note A0 is not used and must be connected to a defined logic level. In Intel 32 bit mode: A1 = BE <sub>3</sub> , A0 = BE <sub>2</sub>                                                                                                                                                                                                                                                                                                                |

| Pin      | Name   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C16      | CS     | Chip Select Input (5 V Tolerant Input) Active low input used with DS to enable read and write access to the ZL50073.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| D14      | DS     | Data Strobe Input (5 V Tolerant Input) Active low input used with CS to enable read and write access to the ZL50073.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| C15      | R/W    | Read/Write Input (5 V Tolerant Input) This input controls the direction of the data bus lines (D31 - 0) during a microprocessor access. This pin is set high and low for the read and write access respectively.                                                                                                                                                                                                                                                                                                                           |

| A19      | DTA    | Data Transfer Acknowledge (5 V Tolerant, 3.3 V Tri-state Output with Slew-Rate)  This active low output indicates that a data bus transfer is complete. Usually used with a Motorola interface. An external pull-up resistor is required to hold this pin HIGH when output is high-impedance.                                                                                                                                                                                                                                              |

| B17      | BERR   | Transfer Bus Error Output with Slew Rate Control (5 V Tolerant, 3.3 V Tri-state Outputs with Slew-Rate Control)  This pin goes low whenever the microprocessor attempts to access an invalid memory space inside the device. In Motorola bus mode, if this bus error signal is activated, the data transfer acknowledge signal, DTA, will not be generated. In Intel bus mode, the generation of the DTA is not affected by this BERR signal. An external pull-up resistor is required to hold a HIGH level when output is high-impedance. |

| D15      | WAIT   | Data Transfer Wait Output (5 V Tolerant, 3.3 V Tri-state Output with Slew Rate) Active low wait signal output. It indicates that a data bus transfer is complete when it goes from low to high. Usually used with an Intel interface. An external pull-up resistor is required to hold this pin HIGH when output is high-impedance                                                                                                                                                                                                         |

| B18, E15 | SIZ0-1 | Data Transfer Size/Upper and Lower Data Strobe Inputs (5 V Tolerant Inputs)  Motorola 32-bit mode - signals indicate data transfer size, refer to Section 10.0.  Motorola 16-bit mode:SIZO - LDS, SIZ1 - UDS.  Active low upper and lower data strobes, UDS and LDS, indicate whether the upper byte, D15 - 8, and/or lower byte, D7 - 0, is being accessed.  Intel 32/16-bit mode: SIZ0 - BEO, SIZ1 - BE1.  Active low Intel type bus-enable signals, BE1 and BEO                                                                         |

| C5       | IM     | Microprocessor Port Bus Mode Select (5 V Tolerant Input) Control input: 0 = Motorola mode 1 = Intel mode                                                                                                                                                                                                                                                                                                                                                                                                                                   |

#### **Pin Description (continued)**

| Pin                                | Name | Description                                                                                                                                                                                                                                                                                                                                                       |  |

|------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| В7                                 | D16B | Microprocessor Port Bus 16/32 Bit Mode Select (5 V Tolerant Input with Internal Pull-down) Control input: 0 = 32 bit data bus 1 = 16 bit data bus                                                                                                                                                                                                                 |  |

| A20                                | PWR  | Device Reset (5 V Tolerant Schmitt-Triggered Input) Asynchronous reset input used to initialize the ZL50073.  0 = Reset 1 = Normal See Section 11.0, Power-up and Initialization of the ZL50073 for detailed description of Reset state.                                                                                                                          |  |

| IEEE 1149.1 Test Access Port (TAP) |      |                                                                                                                                                                                                                                                                                                                                                                   |  |

| D18                                | TDi  | Test Data (5 V Tolerant Input with Internal Pull-up) Serial test data input. When not used, this input may be left unconnected.                                                                                                                                                                                                                                   |  |

| B21                                | TDo  | Test Data (3.3 V Output) Serial test data output.                                                                                                                                                                                                                                                                                                                 |  |

| A22                                | TCK  | Test Clock (5 V Tolerant Schmitt-Triggered Input with Internal Pull-up) Provides the clock to the JTAG test logic                                                                                                                                                                                                                                                 |  |

| C19                                | TRST | Test Reset (5 V Tolerant Schmitt-Triggered Input with International) Asynchronously initializes the JTAG TAP controller by putting it in the Test-Logic-Reset state. This pin should be pulsed low during power-up to ensure that the device is in the normal functional mode. When JTAG is not being used, this pin should be pulled to during normal operation. |  |

| E17                                | TMS  | Test Mode Select (5 V Tolerant Input with Internal Pull-up) JTAG signal that controls the state transitions of the TAP controller. When not used, this pin is pulled high by an internal pull-up resistor and may be left unconnected.                                                                                                                            |  |

#### 1.0 Functional Description

#### 1.1 Overview

The device has 128 ST-BUS/GCI-Bus inputs (STiA0 - 31, STiB0 - 31, STiC0 - 31, STiD0 - 31) and 128 ST-BUS/GCI-Bus outputs (SToA0 - 31, SToB0 - 31, SToC0 - 31, SToD0 - 31). It is a non-blocking digital switch with 32,768 64 kbps channels and is capable of performing rate conversion between groups of 4 inputs and 4 outputs. The inputs accept serial input data streams with data rates of 8.192 Mbps, 16.384 Mbps, 32.768 Mbps or 65.536 Mbps. There are 32 input groups with each group consisting of 4 streams ('A', 'B', 'C' and 'D'). Each group can be set to any of the data rates. The outputs deliver serial data streams with data rates of 8.192 Mbps, 16.384 Mbps, 32.768 Mbps or 65.536 Mbps. There are 32 output groups with each group consisting of 4 streams ('A', 'B', 'C' and 'D'). Each group can be set to any of the data rates.

By using Zarlink's message mode capability, the microprocessor can store data in the connection memory which can be broadcast to the output streams on a per-channel basis. This feature is useful for transferring control and status information for external circuits or other ST-BUS/GCI-Bus devices.

The ZL\_50073 uses the ST-BUS/GCI-Bus master input frame pulse (FPi0) and the ST-BUS/GCI-Bus master input clock (CKi0) to define the input frame boundary and timing for sampling the ST-BUS/GCI-Bus input streams with various data rates (8.192 Mbps, 16.384 Mbps, 32.768 Mbps or 65.536 Mbps). The rate of the input clock is defined by setting the CK\_SEL1 - 0 pins. In addition, two more frame pulses and clocks can be accepted. The frequencies of these signals are automatically detected by the ZL50073.

A selectable Motorola or Intel compatible non-multiplexed microprocessor port allows users to program the device to operate in various modes under different switching configurations. Users can use the microprocessor port to perform internal register and memory read and write operations. The microprocessor port can be selectable to be either a 32 bit or 16 bit data bus and to have either a 19 bit or 17 bit address bus. This is selected by setting the D16B pin. There are seven control signals (CS, DS, R/W, DTA, WAIT, BERR and IM).

The device supports the mandatory requirements for the IEEE 1149.1 (JTAG) standard via the test port.

#### 1.2 Switch Operation

The ZL50073 switches 64 kbps and Nx64 kbps data and voice channels from the TDM input streams, to timeslots in the TDM output streams. The device is non-blocking; all 32 K input channels can be switched through to the outputs. Any input channel can be switched to any available output channel.

Figure 2 - 32 K x 32 K Channel Basic Switch Configuration

The maximum channel switching capacity is determined by the number of streams and their rate of operation, as shown in Table 1.

| TDM Group<br>Data Rate | Maximum Number of Input TDM Data Streams | Maximum Number<br>of Output TDM<br>Data Streams | Number of<br>64 kbps Channels<br>per Stream | Maximum Switch Capacity <sup>†</sup> (streams x channels = total) |

|------------------------|------------------------------------------|-------------------------------------------------|---------------------------------------------|-------------------------------------------------------------------|

| 65.536 Mbps            | 32                                       | 32                                              | 1024                                        | 32 x 1024 = 32,768                                                |

| 32.768 Mbps            | 64                                       | 64                                              | 512                                         | 64 x 512 = 32,768                                                 |

| 16.384 Mbps            | 128                                      | 128                                             | 256                                         | 128 x 256 = 32,768                                                |

| 8.192 Mbps             | 128                                      | 128                                             | 128                                         | 128 x 128 = 16,384 <sup>‡</sup>                                   |

Table 1 - Data Rate and Maximum Switch Size

<sup>†</sup> The maximum capacity shown is when all streams are at the same rate, and none are operating at 8.192 Mbps.

<sup>‡</sup> Switch capacity is limited to less than 32 K channels, only when streams are provisioned at 8 Mbps. The maximum switch capacity in this case is given by 32,768 - (N x 128), where N is the number of 8 Mbps input or output streams.

#### 1.3 Stream Provisioning

The ZL50073 is a large switch with a comprehensive list of user configurable, 'per-group' programmable features. In order to facilitate ease of use, the ZL50073 offers a simple programming model. Streams are grouped in sets of four, with each group sharing the same configured characteristics. In this way it is possible to reduce programming complexity, while still maintaining flexible 'per-group' configuration options:

- Input and output rate selection; see Section 1.4

- Input stream clock source selection; see Section 2.0

- Output stream clock source selection; see Section 2.0

- Input stream sampling point selection; see Section 5.1

- Output stream fractional bit advance; see Section 5.2

- Input and output stream inversion control; see Section 14.4

The streams are grouped, one from the TDM 'A' streams, combined with the corresponding 'B', 'C' and 'D' streams. For example, input stream group #12 is STiA12, STiB12, STiC12, STiD12, and output stream group #4 is SToA4, SToB4, SToC4, SToD4. There are 32 input and 32 output groups. Depending on the data rate set for the group there will be between 1 and 4 streams activated. If the data rate is set for 65.536 Mbps, the 'A' stream will be activated and the 'B', 'C' and 'D' streams will not be activated. If the data rate is set for 32.768 Mbps, the 'A' and 'B' streams will be activated and the 'C' and 'D' streams will not be activated. If the data rate is set for either 16.384 Mbps or 8.192 Mbps all of the streams, 'A', 'B', 'C' and 'D' will be activated. The maximum channel capacity of a group is 1024 channels when operating at any data rate except for 8.192 Mbps, in which case the maximum operating channel capacity decreases to 512 channels.

#### 1.4 Input and Output Rate Selection

Table 1 shows the maximum number of streams available at different bit rates. The ZL50073 deactivates unused streams when operating at the higher bit rates as shown in Table 2.

| Input or Output Group n<br>(n = 0 - 31) | 65 Mbps    | 32 Mbps    | 16 Mbps | 8 Mbps |