# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## PSD3XX ZPSD3XX ZPSD3XXV PSD3XXR ZPSD3XXR ZPSD3XXRV

## Low Cost Field Programmable Microcontroller Peripherals

#### **FEATURES SUMMARY**

- Single Supply Voltage:

- 5 V±10% for PSD3xx, ZPSD3xx, PSD3xxR, ZPSD3xxR

- 2.7 to 5.5 V for ZPSD3xxV, ZPSD3xxRV

- Up to 1 Mbit of EPROM

- Up to 16 Kbit SRAM

- Input Latches

- Programmable I/O ports

- Page Logic

- Programmable Security

### **PSD3XX Family** PSD3XX ZPSD3XX ZPSD3XXV PSD3XXR ZPSD3XXR ZPSD3XXRV Low Cost Microcontroller Peripherals

### Table of Contents

| 1  | Introd | uction                                                       | 1  |

|----|--------|--------------------------------------------------------------|----|

| 2  | Notati | on                                                           | 2  |

| 3  | Key F  | eatures                                                      | 4  |

| 4  | PSD3   | XX Family Feature Summary                                    | 5  |

| 5  | Partia | I Listing of Microcontrollers Supported                      | 6  |

| 6  | Applic | ations                                                       | 6  |

| 7  | ZPSD   | Background                                                   | 6  |

|    | 7.1    | Integrated Power Management <sup>TM</sup> Operation          | 7  |

| 8  | Opera  | ting Modes (MCU Configurations)                              | 10 |

| 9  | Progra | ammable Address Decoder (PAD)                                | 12 |

| 10 | I/O Po | rt Functions                                                 | 15 |

|    | 10.1   | CSIOPORT Registers                                           | 15 |

|    | 10.2   | Port A (PA0-PA7)                                             | 16 |

|    |        | 10.2.1 Port A (PA0-PA7) in Multiplexed Address/Data Mode     |    |

|    |        | 10.2.2 Port A (PA0-PA7) in Non-Multiplexed Address/Data Mode | 17 |

|    | 10.3   | Port B (PB0-PB7)                                             | 18 |

|    |        | 10.3.1 Port B (PA0-PA7) in Multiplexed Address/Data Mode     | 18 |

|    |        | 10.3.2 Port B (PA0-PA7) in Non-Multiplexed Address/Data Mode | 19 |

|    | 10.4   | Port C (PC0-PC2)                                             |    |

|    | 10.5   | ALE/AS Input Pin                                             |    |

| 11 | PSD N  | Aemory                                                       | 21 |

|    | 11.1   | EPROM                                                        | 21 |

|    | 11.2   | SRAM (Optional)                                              | 21 |

|    | 11.3   | Page Register (Optional)                                     | 21 |

|    | 11.4   | Programming and Erasure                                      | 21 |

| 12 | Contro | bl Signals                                                   |    |

|    | 12.1   | ALE or AS                                                    |    |

|    | 12.2   | WR or R/W                                                    |    |

|    | 12.3   | RD/E/DS (DS option not available on 3X1 devices)             |    |

|    | 12.4   | PSEN or PSEN                                                 |    |

|    | 12.5   | A19/CSI                                                      |    |

|    | 12.6   | Reset Input                                                  |    |

| 13 |        | am/Data Space and the 8031                                   |    |

| 14 |        | ns Applications                                              |    |

| 15 | Secur  | ity Mode                                                     | 30 |

| 16 | Power  | Management                                                   | 30 |

|    | 16.1   | CSI Input                                                    | 30 |

|    | 16.2   | CMiser Bit                                                   |    |

|    | 16.3   | Turbo Bit (ZPSD Only)                                        |    |

|    | 16.4   | Number of Product Terms in the PAD Logic                     |    |

|    | 16.5   | Composite Frequency of the Input Signals to the PAD Logic    | 32 |

|    | 16.6   | Loading on I/O Pins                                          |    |

| 17 | Calcu  | ating Power                                                  | 34 |

### **PSD3XX Family** PSD3XX ZPSD3XX ZPSD3XXV PSD3XXR ZPSD3XXR ZPSD3XXRV Low Cost Microcontroller Peripherals Table of Contents (cont.)

| 18             | Specifications                                                | 37 |

|----------------|---------------------------------------------------------------|----|

|                | 18.1 Absolute Maximum Ratings                                 | 37 |

|                | 18.2 Operating Range                                          | 37 |

|                | 18.3 Recommended Operating Conditions                         | 37 |

|                | 18.4 Pin Capacitance                                          | 37 |

|                | 18.5 AC/DC Characteristics – PSD3XX/ZPSD3XX (All 5 V devices) | 38 |

|                | 18.6 AC/DC Characteristics – PSD3XXV (3 V devices only)       | 39 |

|                | 18.7 Timing Parameters – PSD3XX/ZPSD3XX (All 5 V devices)     |    |

|                | 18.8 Timing Parameters – ZPSD3XXV (3 V devices only)          |    |

|                | 18.9 Timing Diagrams for PSD3XX Parts                         |    |

|                | 18.10 AC Testing                                              |    |

| 19             | Pin Assignments                                               |    |

| 20             | Package Information                                           |    |

| 21             | Package Drawings                                              | 68 |

| 22             | PSD3XX Product Ordering Information                           |    |

|                | 22.1 PSD3XX Selector Guide                                    | 72 |

|                |                                                               | 73 |

|                | 22.2 Part Number Construction                                 | 73 |

| 23             | Data Sheet Revision History                                   | 80 |

|                | 22.2 Part Number Construction                                 |    |

| O <sub>k</sub> | )~                                                            |    |

## Programmable Peripheral **PSD3XX** Family Field-Programmable Microcontroller Peripheral

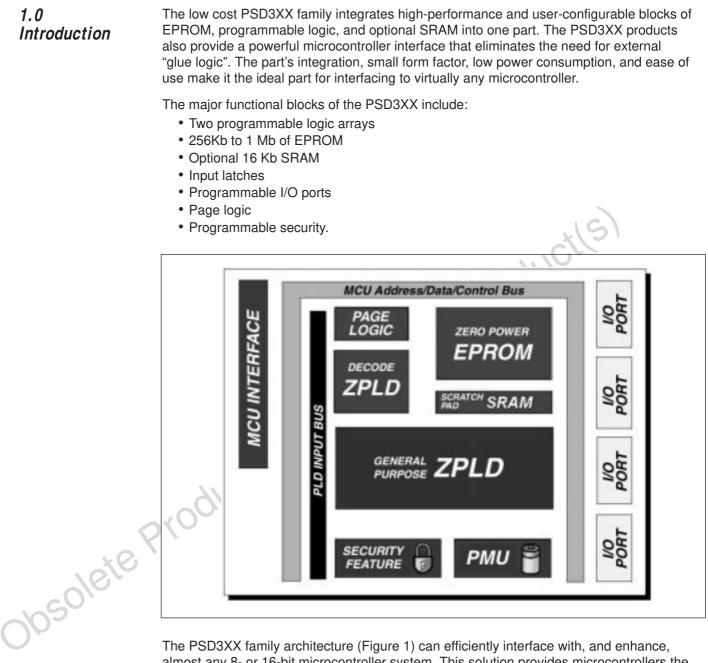

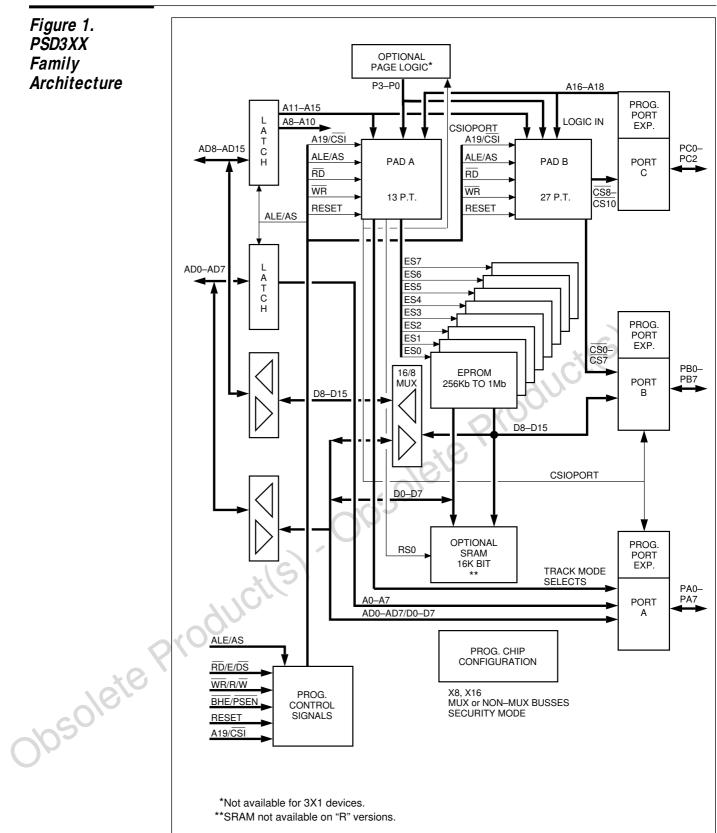

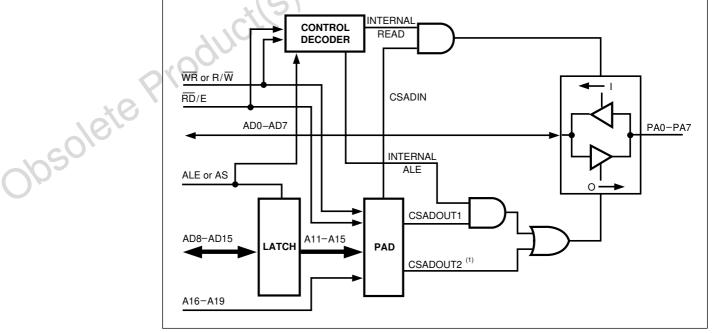

The PSD3XX family architecture (Figure 1) can efficiently interface with, and enhance, almost any 8- or 16-bit microcontroller system. This solution provides microcontrollers the following:

- · Chip-select logic, control logic, and latched address signals that are otherwise implemented discretely

- Port expansion (reconstructs lost microcontroller I/O)

- Expanded microcontroller address space (up to 16 times)

- An EPROM (with security) and optional SRAM

- Compatible with 8031-type architectures that use separate Program and Data Space

- Interface to shared external resources.

| 1.0<br>Introduction<br>(cont.) | The PSD3XX I/O po<br>Standard I/O p<br>Programmable<br>Address inputs<br>Demultiplexed<br>A data bus por<br>A data bus "rep<br>external device | orts<br>chip select<br>address ou<br>t for non-mi<br>peater" port | outputs<br>tputs<br>ultiplexed M                             |                                                        |                                        | MCU data bu   | us with      |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------|----------------------------------------|---------------|--------------|

|                                | Implementing your<br>development suite.<br>• Configure your<br>• Specify what you<br>Hardware Deso<br>• Simulate your<br>• Download your       | Using PSD<br>PSD3XX to<br>ou want imp<br>cription Lan<br>design   | soft, you can<br>b work with v<br>blemented ir<br>guage (HDL | n do the follo<br>virtually any<br>1 the program<br>.) | owing:<br>microcontrol<br>mmable logic | ler           |              |

| 2.                             | For a complete proc                                                                                                                            | duct compa                                                        | rison, refer t                                               | o Table 1.                                             |                                        |               |              |

| Notation                       | <b>PSD3XX</b> references general-purpose en                                                                                                    |                                                                   |                                                              |                                                        | XX family, wł                          | nich are idea | Lfor         |

|                                | PSD3XXR SRAM-le                                                                                                                                |                                                                   |                                                              | •                                                      |                                        | the 16 Kb S   | RAM or       |

|                                | <b>ZPSD3XX</b> has impr<br>bit. Excellent if you                                                                                               |                                                                   |                                                              |                                                        |                                        |               | ng the Turbo |

|                                | ZPSD3XXR SRAM                                                                                                                                  | less versio                                                       | n of the ZPS                                                 | D3XX.                                                  |                                        |               |              |

|                                | <b>ZPSD3XXV</b> 2.7 V to applications.                                                                                                         | o 5.5 V ope                                                       | ration, ideal                                                | for very low                                           | -power and I                           | ow-voltage    |              |

|                                | <b>ZPSD3XXRV</b> SRAM                                                                                                                          | ∕I-less versi                                                     | on of the ZF                                                 | SD3XXV.                                                |                                        |               |              |

|                                | Throughout this dat<br>references also cov<br>"3X1 only" cover all<br>to determine what r                                                      | er the entire<br>parts that h                                     | e family. Exc<br>nave a 301 c                                | eptions will<br>or 311 in the                          | be noted. Re part number               | eferences, si | uch as       |

|                                | Reference                                                                                                                                      | PSD3XX                                                            | PSD3XXR                                                      | ZPSD3XX                                                | ZPSD3XXR                               | ZPSD3XXV      | ZPSD3XXRV    |

| Obsole                         | PSD3XX<br>PSD                                                                                                                                  | х                                                                 | x                                                            | Х                                                      | x                                      | х             | x            |

| 005                            | PSD3XX only                                                                                                                                    | Х                                                                 | Х                                                            |                                                        |                                        |               |              |

|                                | Non-ZPSD                                                                                                                                       | Х                                                                 | Х                                                            |                                                        |                                        |               |              |

|                                | ZPSD only<br>ZPSD3XX                                                                                                                           |                                                                   |                                                              | х                                                      | x                                      | х             | x            |

|                                | Non-V versions                                                                                                                                 | Х                                                                 | Х                                                            | Х                                                      | Х                                      |               |              |

|                                | V versions only<br>V suffix<br>ZPSD3XXV only                                                                                                   |                                                                   |                                                              |                                                        |                                        | х             | x            |

|                                | SRAM-less<br>Non-R                                                                                                                             | х                                                                 |                                                              | x                                                      |                                        | х             |              |

3.0 Key Features

□ Single-chip programmable peripheral for microcontroller-based applications

□ 256K to 1 Mbit of UV EPROM with the following features:

- Configurable as 32, 64, or 128 K x 8; or as 16, 32, or 64 K x 16

- Divided into eight equally-sized mappable blocks for optimized address mapping

- As fast as 70 ns access time, which includes address decoding

- □ Optional 16 Kbit SRAM is configurable as 2K x 8 or 1K x 16. The access time can be as quick as 70 ns, including address decoding.

- □ 19 I/O pins that can be individually configured for :

- Microcontroller I/O port expansion

- Programmable Address decoder (PAD) I/O

- Latched address output

- Open-drain or CMOS output

- Two Programmable Arrays (PAD A and PAD B) replace your PLD or decoder, and have the following features:

- Up to 18 Inputs and 24 outputs

- 40 Product terms (13 for PAD A and 27 for PAD B)

- Ability to decode up to 1 MB of address without paging

- Microcontroller logic that eliminates the need for external "glue logic" has the following features:

- · Ability to interface to multiplexed and non-multiplexed buses

- Built-in address latches for multiplexed address/data bus

- ALE and Reset polarity are programmable (Reset polarity not programmable on V-versions)

- · Multiple configurations are possible for interface to many different microcontrollers

- Optional built-in page logic expands the MCU address space by up to 16 times

- □ Programmable power management with standby current as low as 1µA for low-voltage version

- CMiser bit—programmable option to reduce AC power consumption in memory

- Turbo Bit (ZPSD only)—programmable bit to reduce AC and DC power consumption in the PADs.

- Track Mode that allows other microcontrollers or host processors to share access to the local data bus

- Built-in security locks the device and PAD decoding configuration

- J Wide Operating Voltage Range

- V-versions: 2.7 to 5.5 volts

- Others: 4.5 to 5.5 volts

- Available in a variety of packaging (44-pin PLDCC, CLDCC, TQFP, and PQFP)

- □ Simple, menu-driven software (PSDsoft) allows configuration and design entry on a PC.

)psole

#### 4.0 **PSD3XX** Family Feature Summary

Use the following table to determine which PSD product will fit your needs. Refer back to this page whenever there is confusion as to which part has what features.

| Feature<br>Summary | Part                                           | # PLD<br>Inputs | EPROM<br>Size    | SRAM<br>Size   | Page<br>Reg | Voltage        | Turbo<br>Bit  | Bus<br>Width    | Typical<br>Standby<br>Current |

|--------------------|------------------------------------------------|-----------------|------------------|----------------|-------------|----------------|---------------|-----------------|-------------------------------|

|                    | PSD301R<br>PSD311R                             | 14<br>14        | 256 Kb<br>256 Kb |                |             | 5 V<br>5 V     |               | x8 or x16<br>x8 | 50 μA<br>50 μA                |

|                    | PSD302R<br>PSD312R                             | 18<br>18        | 512 Kb<br>512 Kb |                | X<br>X      | 5 V<br>5 V     |               | x8 or x16<br>x8 | 50 μA<br>50 μA                |

|                    | PSD303R<br>PSD313R                             | 18<br>18        | 1 Mb<br>1 Mb     |                | X<br>X      | 5 V<br>5 V     |               | x8 or x16<br>x8 | 50 μA<br>50 μA                |

|                    | ZPSD301R<br>ZPSD311R                           | 14<br>14        | 256 Kb<br>256 Kb |                |             | 5 V<br>5 V     | X<br>X        | x8 or x16<br>x8 | 10 μΑ<br>10 μΑ                |

|                    | ZPSD302R<br>ZPSD312R                           | 18<br>18        | 512 Kb<br>512 Kb |                | X<br>X      | 5 V<br>5 V     | X<br>X        | x8 or x16<br>x8 | 10 μΑ<br>10 μΑ                |

|                    | ZPSD303R<br>ZPSD313R                           | 18<br>18        | 1 Mb<br>1 Mb     |                | X<br>X      | 5 V<br>5 V     | X<br>X        | x8 or x16       | 10 μΑ<br>10 μΑ                |

|                    | PSD301<br>PSD311                               | 14<br>14        | 256 Kb<br>256 Kb | 16 Kb<br>16 Kb |             | 5 V<br>5 V     |               | x8 or x16<br>x8 | 50 μA<br>50 μA                |

|                    | PSD302<br>PSD312                               | 18<br>18        | 512 Kb<br>512 Kb | 16 Kb<br>16 Kb | X<br>X      | 5 V<br>5 V     |               | x8 or x16<br>x8 | 50 μA<br>50 μA                |

|                    | PSD303<br>PSD313                               | 18<br>18        | 1 Mb<br>1 Mb     | 16 Kb<br>16 Kb | xx          | 5 V<br>5 V     |               | x8 or x16<br>x8 | 50 μA<br>50 μA                |

|                    | ZPSD301<br>ZPSD311                             | 14<br>14        | 256 Kb<br>256 Kb | 16 Kb<br>16 Kb |             | 5 V<br>5 V     | X<br>X        | x8 or x16<br>x8 | 10 μΑ<br>10 μΑ                |

|                    | ZPSD302<br>ZPSD312                             | 18<br>18        | 512 Kb<br>512 Kb | 16 Kb<br>16 Kb | X<br>X      | 5 V<br>5 V     | X<br>X        | x8 or x16<br>x8 | 10 μA<br>10 μA                |

|                    | ZPSD303<br>ZPSD313                             | 18<br>18        | 1 Mb<br>1 Mb     | 16 Kb<br>16 Kb | X<br>X      | 5 V<br>5 V     | X<br>X        | x8 or x16<br>x8 | 10 μΑ<br>10 μΑ                |

|                    | ZPSD301V <sup>1</sup><br>ZPSD311V <sup>1</sup> | 14<br>14        | 256 Kb<br>256 Kb | 16 Kb<br>16 Kb |             | 2.7 V<br>2.7 V | X<br>X        | x8 or x16<br>x8 | 1 μΑ<br>1 μΑ                  |

| 0                  | ZPSD302V <sup>1</sup><br>ZPSD312V <sup>1</sup> | 18<br>18        | 512 Kb<br>512 Kb | 16 Kb<br>16 Kb | X<br>X      | 2.7 V<br>2.7 V | X<br>X        | x8 or x16<br>x8 | 1 μΑ<br>1 μΑ                  |

| ×er                | ZPSD303V <sup>1</sup><br>ZPSD313V <sup>1</sup> | 18<br>18        | 1 Mb<br>1 Mb     | 16 Kb<br>16 Kb | X<br>X      | 2.7 V<br>2.7 V | X<br>X        | x8 or x16<br>x8 | 1 μΑ<br>1 μΑ                  |

| )bsolete P         | NOTES: 1. Low pow                              | er versions     | of the ZPS       | D3XX (ZPS      | SD3XXV) ca  | in only acce   | ept an active | e-low level Res | set input.                    |

|                    |                                                |                 |                  |                |             |                |               |                 |                               |

| 5.0<br>Partial Listing        | <b>Motorola family:</b> 68HC11, 68HC16, M68000/10/20, M68008, M683XX, 68HC05C0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| of                            | ☐ Intel family: 80C31, 80C51, 80C196/198, 80C186/188                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Microcontrollers<br>Supported | Philips family: 80C31 and 80C51 based MCUs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Supported                     | <b>Zilog:</b> Z8, Z80, Z180                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                               | <b>National:</b> HPC16000, HPC46400                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                               | ❑ Echelon/Motorola/Toshiba: NEURON <sup>®</sup> 3150 <sup>™</sup> Chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 6.0<br>Applications           | <ul> <li>Telecommunications:</li> <li>Cellular phone</li> <li>Digital PBX</li> <li>Digital speech</li> <li>FAX</li> <li>Digital Signal Processing (DSP)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                               | <ul> <li>Portable Industrial Equipment:</li> <li>Industrial control</li> <li>Measurement meters</li> <li>Data recorders</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                               | <ul> <li>Digital Signal Processing (DSP)</li> <li>Portable Industrial Equipment: <ul> <li>Industrial control</li> <li>Measurement meters</li> <li>Data recorders</li> </ul> </li> <li>Instrumentation <ul> <li>Medical Instrumentation:</li> <li>Hearing aids</li> <li>Monitoring equipment</li> <li>Diagnostic tools</li> </ul> </li> <li>Computers—notebooks, portable PCs, and palm-top computers:</li> </ul>                                                                                                                                                                                                                                                                                                                                                                     |

|                               | <ul> <li>Computers—notebooks, portable PCs, and palm-top computers:</li> <li>Peripheral control (fixed disks, laser printers, etc.)</li> <li>Modem Interface</li> <li>MCU peripheral interface</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 7.0<br>ZPSD<br>Background     | Portable and battery-powered systems have recently become major embedded control application segments. As a result, the demand for electronic components having extremely low power consumption has increased dramatically. Recognizing this trend, ST developed a new lower power 3XX part, denoted ZPSD3XX. The Z stands for Zero-power because ZPSD products virtually eliminate the DC component of power consumption, reducing it to standby levels. Virtual elimination of the DC component is the basis for the words "Zero-power" in the ZPSD name. ZPSD products also minimize the AC power component when the chip is changing states. The result is a programmable microcontroller peripheral family that replaces discrete circuit components, while drawing less power. |

7.0 ZPSD Background (cont.)

#### Integrated Power Management<sup>™</sup> Operation

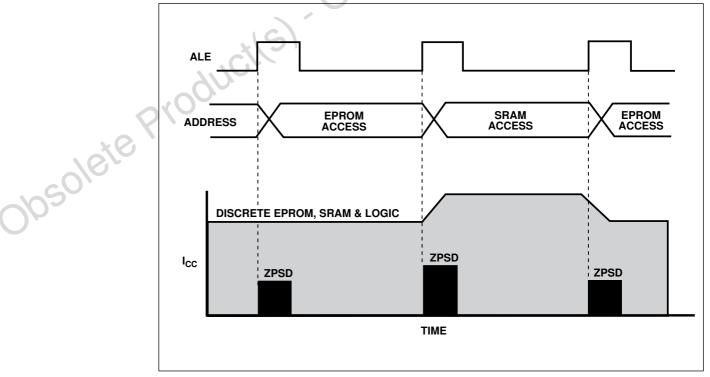

Upon each address or logic input change to the ZPSD, the device powers up from low power standby for a short time. Then the ZPSD consumes only the necessary power to deliver new logic or memory data to its outputs as a response to the input change. After the new outputs are stable, the ZPSD latches them and automatically reverts back to standby mode. The  $I_{CC}$  current flowing during standby mode and during DC operation is identical and is only a few microamperes.

The ZPSD automatically reduces its DC current drain to these low levels and does not require controlling by the CSI (Chip Select Input). Disabling the CSI pin unconditionally forces the ZPSD to standby mode independent of other input transitions.

The only significant power consumption in the ZPSD occurs during AC operation.

The ZPSD contains the first architecture to apply zero power techniques to memory and logic blocks.

Figure 2 compares ZPSD zero power operation to the operation of a discrete solution. A standard microcontroller (MCU) bus cycle usually starts with an ALE (or AS) pulse and the generation of an address. The ZPSD detects the address transition and powers up for a short time. The ZPSD then latches the outputs of the PAD, EPROM and SRAM to the new values. After finishing these operations, the ZPSD shuts off its internal power, entering standby mode. The time taken for the entire cycle is less than the ZPSD's "access time."

The ZPSD will stay in standby mode while its inputs are not changing between bus cycles. In an alternate system implementation using discrete EPROM, SRAM, and other discrete components, the system will consume operating power during the entire bus cycle. This is because the chip select inputs on the memory devices are usually active throughout the entire cycle. The AC power consumption of the ZPSD may be calculated using the composite frequency of the MCU address and control signals, as well as any other logic inputs to the ZPSD.

#### Figure 2. ZPSD Power Operation vs. Discrete Implementation

| Table 2.<br>PSD3XX Pin | Name                                                 | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------------|------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Descriptions           | BHE/<br>PSEN                                         | I    | When the data bus is 8 bits:<br>This pin is for 8031 or compatible MCUs that use $\overrightarrow{PSEN}$ to<br>separate program space from data space. In this case, $\overrightarrow{PSEN}$ is<br>used for reads from the EPROM. Note: if your MCU does not<br>output a $\overrightarrow{PSEN}$ signal, pull up this pin to V <sub>CC</sub> .<br>When the data bus is 16 bits:<br>This pin is BHE. When low, D8-D15 are read from or written to.<br>Note: in programming mode, this pin is pulsed between V <sub>PP</sub> and 0 V.                                                 |

|                        | WR/V <sub>PP</sub><br>_or<br>R/W/V <sub>PP</sub>     | I    | <ul> <li>The following control signals can be connected to this port, based on your MCU (and the way you configure the PSD in PSDsoft):</li> <li>1. WR—active-low write pulse.</li> <li>2. R/W—active-high read/active-low write input.</li> <li>Note: in programming mode, this pin must be tied to V<sub>PP</sub>.</li> </ul>                                                                                                                                                                                                                                                     |

|                        | RD/E/DS                                              | I    | <ul> <li>The following control signals can be connected to this port, based on your MCU (and the way you configure the PSD in PSDsoft):</li> <li>1. RD—active-low read input.</li> <li>2. E—E clock input.</li> <li>3. DS—active-low data strobe input (3X2/3X3 devices only)</li> </ul>                                                                                                                                                                                                                                                                                            |

|                        | A19/CSI                                              | I    | <ol> <li>The following control signals can be connected to this port:</li> <li>1. CSI—Active-low chip select input. If your MCU supports a chip select output, and you want the PSD to save power when not selected, use this pin as a chip select input.</li> <li>2. If you don't wish to use the CSI feature, you may use this pin as an additional input (logic or address) to the PAD. A19 can be latched (with ALE/AS), or a transparent logic input.</li> </ol>                                                                                                               |

|                        | Reset                                                |      | PSD3XX/ZPSD3XX:<br>This pin is user-programmable and can be configured to reset on a<br>high- or low-level input. Reset must be applied for at least 100 ns.<br>ZPSD3XXV:<br>This pin is <b>not</b> configurable, and the chip will only reset on an<br>active-low level input. Reset must be applied for at least 500 ns,<br>and no operations may take place for an additional 500 ns minimum.<br>(See Figure 8.)                                                                                                                                                                 |

| obsolete               | ALE/AS                                               | 1    | If you use an MCU that has a multiplexed bus:<br>Connect ALE or AS to this pin. The polarity of this pin is configurable.<br>The trailing edge of ALE/AS latches all multiplexed address inputs<br>(and BHE where applicable).<br>If you use an MCU that does not have a multiplexed bus:<br>If your MCU uses ALE/AS, connect the signal to this pin.<br>Otherwise, use this pin for a generic logic input to the PAD.<br>(Non-3X1 devices only.)                                                                                                                                   |

|                        | PA0<br>PA1<br>PA2<br>PA3<br>PA4<br>PA5<br>PA6<br>PA7 | I/O  | <ul> <li>These pins make up Port A. These port pins are configurable, and can have the following functions: (see Figure 5A and 5B)</li> <li>1. Track AD7-AD0. This feature repeats the MCU address and data bus on all Port A pins.</li> <li>2. MCU I/O—in this mode, the direction of the pin is defined by its direction bit, which resides in the direction register.</li> <li>3. Latched address output.</li> <li>4. CMOS or open-drain output.</li> <li>5. If your MCU is non-multiplexed: data bus input—connect your data bus (D0-7) to these pins. See Figure 3.</li> </ul> |

*Legend:* The Type column abbreviations are: I = input only; I/O = input/output; P = power.

| PSD3XX Pin              | Name                                                                                     | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------------|------------------------------------------------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Descriptions<br>(cont.) | PB0<br>PB1<br>PB2<br>PB3<br>PB4<br>PB5<br>PB6<br>PB7                                     | I/O  | <ul> <li>These pins make up Port B. These port pins are configurable, and can have the following functions: (see Figure 6)</li> <li>MCU I/O—in this mode, the direction of the pin is defined by its direction bit, which resides in the direction register.</li> <li>Chip select output—each of PB0-3 has four product terms available per pin, while PB4-7 have 2 product terms each. See Figure 4.</li> <li>CMOS or open-drain.</li> <li>If your MCU is non-multiplexed, and the data bus width is 16 bits: data bus input—connect your data bus (D8-D15) to these pins. See Figure 3.</li> </ul> |

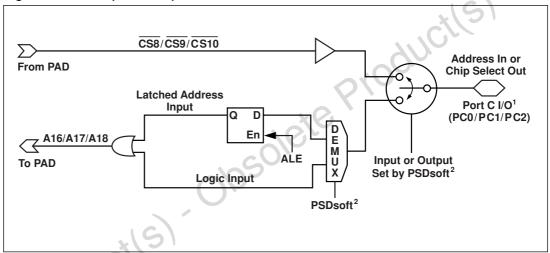

|                         | PC0<br>PC1<br>PC2                                                                        | I/O  | <ul> <li>These pins make up Port C. These port pins are configurable, and can have the following functions (see Figure 7):</li> <li>1. PAD input—when configured as an input, a bit individually becomes an address or a logic input, depending on your PSDsoft design file. When declared as an address, the bit(s) can be latched with ALE/AS.</li> <li>2. PAD output—when configured as an output (i.e. there is an equation written for it in your PSDsoft design file), there is one product term available to it.</li> </ul>                                                                   |

|                         | AD0/A0<br>AD1/A1<br>AD2/A2<br>AD3/A3<br>AD4/A4<br>AD5/A5<br>AD6/A6<br>AD7/A7             | I/O  | If your MCU is multiplexed:<br>These pins are the multiplexed, low-order address/data byte<br>(AD0-AD7). As inputs, address information is latched by the ALE/AS<br>signal and used internally by the PSD. The pins also serve as MCU<br>data bus inputs or outputs, depending on the MCU control signals<br>(RD, WR, etc.).<br>If your MCU is non-multiplexed:<br>These pins are the low-order address inputs (A0-A7)                                                                                                                                                                               |

| Q                       | AD8/A8<br>AD9/A9<br>AD10/A10<br>AD11/A11<br>AD12/A12<br>AD13/A13<br>AD14/A14<br>AD15/A15 | 1/0  | <b>If your MCU is multiplexed with a 16-bit data bus:</b><br>These pins are the multiplexed, high-order address/data byte<br>(AD8-AD15). As inputs, address information is latched by the<br>ALE/AS signal and used internally the PSD. The pins also<br>serve as MCU data bus inputs or outputs, depending on the MCU<br>control signals (RD, WR, etc.).<br><b>If your MCU is non-multiplexed or has a 8-bit data bus:</b><br>These pins are the high-order address inputs (A8-A15).                                                                                                                |

| )bsoleter               | GND                                                                                      | Р    | Ground Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                         | V <sub>CC</sub>                                                                          | Р    | Supply voltage input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

#### 8.0 Operating Modes (MCU Configurations)

The PSD3XX's four operating modes enable it to interface directly to most 8- and 16-bit microcontrollers with multiplexed and non-multiplexed address/data busses. The 16-bit modes are not available to some devices; see Table 1. The following are the four operating modes available:

- Multiplexed 8-bit address/data bus

- Multiplexed 16-bit address/data bus

- Non-multiplexed 8-bit data bus

- Non-multiplexed 16-bit data bus

Please read the section below that corresponds to your type of MCU. Then check the appropriate Figure (3A/3B/3C/3D) to determine your pin connections. Table 3 lists the Port connections in tabular form.

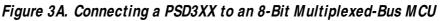

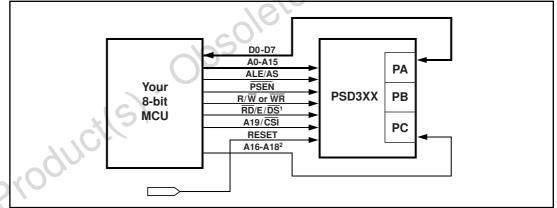

#### Multiplexed 8-bit address/data bus (Figure 3A)

This mode is used to interface to microcontrollers with a multiplexed 8-bit data bus. Since the low-order address and data are multiplexed together, your MCU will output an ALE or AS signal. The PSD3XX contains a transparent latch to demultiplex the address/data lines internally. All you have to do is connect the ALE/AS signal and select 8-bit multiplexed bus mode in PSDsoft. If your MCU outputs more than 16 bits of address, and you wish to connect them to the PSD, connect A16-A18 to Port C and A19 to A19/CSI, where applicable.

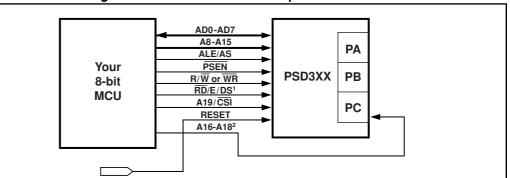

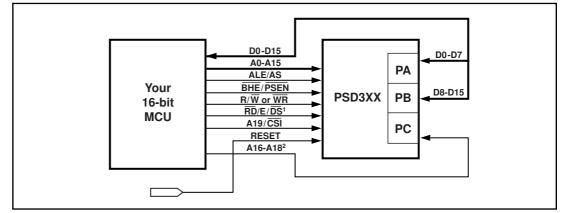

#### Multiplexed 16-bit address/data bus (Figure 3B)

This mode is used to interface to microcontrollers with a multiplexed 16-bit data bus. Since the low address bytes and data are multiplexed together, your MCU will output an ALE or AS signal. The PSD3XX contains a transparent latch to demultiplex the address/data lines internally. All you have to do is connect the ALE/AS signal and select 8-bit multiplexed bus mode in PSDsoft. If your MCU outputs more than 16 bits of address, and you wish to connect them to the PSD, connect A16-A18 to Port C and A19 to A19/CSI, where applicable.

#### Non-multiplexed 8-bit data bus (Figure 3C)

This mode is used to interface to microcontrollers with a non-multiplexed 8-bit data bus. Connect the MCU's address bus to AD0/A0-AD15/A15 on the PSD. Connect the data bus signals of your MCU to Port A of the PSD. If your MCU outputs more than 16 bits of address, and you wish to connect them to the PSD, connect A16-A18 to Port C and A19 to A19/ $\overline{\text{CSI}}$ , where applicable.

#### Non-multiplexed 16-bit data bus (Figure 3D)

This mode is used to interface to microcontrollers with a non-multiplexed 16-bit data bus. Connect the MCU's address bus to AD0/A0-AD15/A15 on the PSD. Connect the low byte data bus signals of your MCU to Port A, and the high byte data output of your MCU to Port B of the PSD. If your MCU outputs more than 16 bits of address, and you wish to connect them to the PSD, connect A16-A18 to Port C and A19 to A19/CSI, where applicable.

For users with multiplexed MCUs that have data multiplexed on address lines other than A0-A7 note: You can still use the PSD3XX, but you will have to connect your data to Port A (and Port B where required), as shown in Figure 3C or 3D. That is, you will be connecting it as if you were using a non-multiplexed MCU. In this case, you must connect the ALE/AS signal so that the address will still be properly latched. This option is not available on the 3X1 versions.

ipsol

8.0 Operating Modes (MCU Configurations) (cont.)

Obsolete

Figure 3C. Connecting a PSD3XX to an 8-Bit Non-Multiplexed-Bus MCU

Figure 3D. Connecting a PSD3XX to a 16-Bit Non-Multiplexed-Bus MCU

**NOTES:** 1.  $\overline{DS}$  is a valid input on 3X2/3X3 and devices only.

2. Connect A16-A18 to Port C if your MCU outputs more than 16 bits of address.

| perating<br>Iodes (MCU |                 | Multiplexed Address/Data                                                        | Non-Multiplexed Address/Data                                 |

|------------------------|-----------------|---------------------------------------------------------------------------------|--------------------------------------------------------------|

| Configurations)        | 8-bit Data Bus  |                                                                                 |                                                              |

| cont.)                 | Port A          | I/O or low-order address<br>lines or Low-order multiplexed<br>address/data byte | D0–D7 data bus byte                                          |

|                        | Port B          | I/O and/or $\overline{CS0}$ – $\overline{CS7}$                                  | I/O and/or $\overline{\text{CS0}}$ – $\overline{\text{CS7}}$ |

|                        | AD0/A0-AD7/A7   | Low-order multiplexed address/data byte                                         | Low-order address bus byte                                   |

|                        | AD8/A8-AD15/A15 | High-order address bus byte                                                     | High-order address bus byte                                  |

|                        | 16-bit Data Bus |                                                                                 |                                                              |

|                        | Port A          | I/O or low-order address<br>lines or low-order multiplexed<br>address/data byte | Low-order data bus byte                                      |

|                        | Port B          | I/O and/or $\overline{CS0}$ – $\overline{CS7}$                                  | High-order data bus byte                                     |

|                        | AD0/A0-AD7/A7   | Low-order multiplexed address/data byte                                         | Low-order address bus byte                                   |

|                        | AD8/A8-AD15/A15 | High-order multiplexed address/data byte                                        | High-order address bus byte                                  |

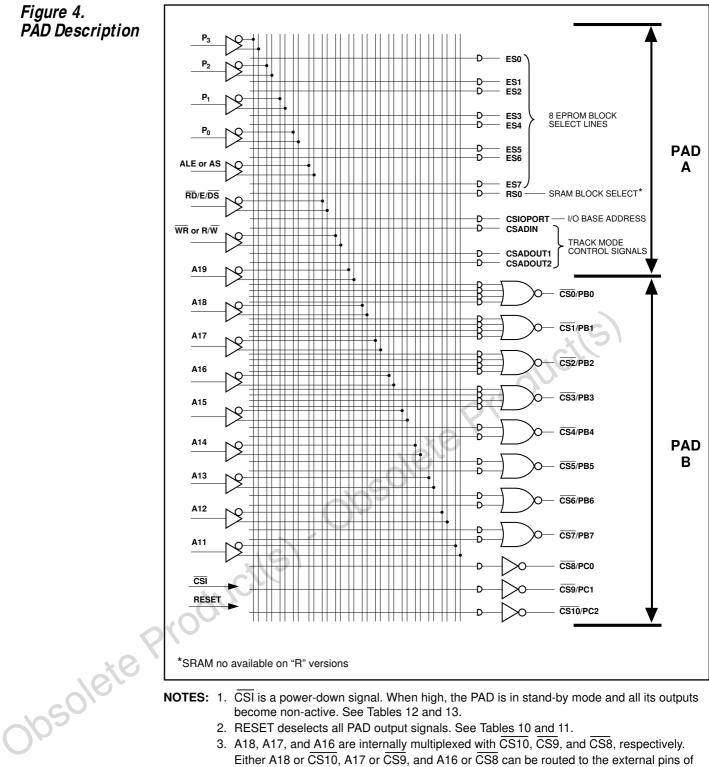

#### 9.0 Programmable Address Decoder (PAD)

3050lete

The PSD3XX contains two programmable arrays, referred to as PAD A and PAD B (Figure 4). PAD A is used to generate chip select signals derived from the input address to the internal EPROM blocks, SRAM, I/O ports, and Track Mode signals.

vO.

PAD B outputs to Ports B and C for off-chip usage. PAD B can also be used to extend the decoding to select external devices or as a random logic replacement.

PAD A and PAD B receive the same inputs. The PAD logic is configured by PSDsoft based on the designer's input. The PAD's non-volatile configuration is stored in a re-programmable CMOS EPROM. Windowed packages are available for erasure by the user. See Table 4 for a list of PAD A and PAD B functions.

Figure 4. PAD Description

NOTES: 1. CSI is a power-down signal. When high, the PAD is in stand-by mode and all its outputs become non-active. See Tables 12 and 13.

- 2. RESET deselects all PAD output signals. See Tables 10 and 11.

- 3. A18, A17, and A16 are internally multiplexed with  $\overline{CS10}$ ,  $\overline{CS9}$ , and  $\overline{CS8}$ , respectively. Either A18 or CS10, A17 or CS9, and A16 or CS8 can be routed to the external pins of Port C. Port C pins can be configured as either input or output, individually.

- 4. P<sub>0</sub>–P<sub>3</sub> are not included on 3X1 devices.

- 5. DS is not available on 3X1 devices.

| Table 4.                                 |                                     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------------------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PSD3XX                                   | PAD A and PAD                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| <i>PAD A and<br/>PAD B<br/>Functions</i> | A19/CSI                             | When the PSD is configured to use $\overline{CSI}$ and while $\overline{CSI}$ is a logic 1, the PAD deselects all of its outputs and enters a power-down mode (see Tables 12 and 13). When the PSD is configured to use A19, this signal is another input to the PAD.                                                                                                                                                                                                          |

|                                          | A16–A18                             | These are general purpose inputs from Port C. See Figure 4, Note 3.                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                          | A11–A15                             | These are address inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                          | P0-P3                               | These are inputs from the page register (not available on 3X1 versions).                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                          | RD/E/DS                             | This is the read pulse or strobe input. ( $\overline{DS}$ not available on 3X1 versions).                                                                                                                                                                                                                                                                                                                                                                                      |

|                                          | $\overline{WR}$ or $R/\overline{W}$ | This is the write pulse or $R/\overline{W}$ select signal.                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                          | ALE/AS                              | This is the ALE or AS input to the chip. Use to demultiplex address and data.                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                          | RESET                               | This deselects all outputs from the PAD; it can not be used in product term equations. See Tables 10 and 11.                                                                                                                                                                                                                                                                                                                                                                   |

|                                          | PAD A Outputs                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                          | ES0-ES7                             | These are internal chip-selects to the 8 EPROM banks. Each bank can be located on any boundary that is a function of one product term of the PAD address inputs.                                                                                                                                                                                                                                                                                                               |

|                                          | RS0                                 | This is an internal chip-select to the SRAM. Its base address location is a function of one term of the PAD address inputs.                                                                                                                                                                                                                                                                                                                                                    |

|                                          | CSIOPORT                            | This internal chip-select selects the I/O ports. It can be placed on any boundary that is a function of one product term of the PAD inputs. See Tables 5A and 5B.                                                                                                                                                                                                                                                                                                              |

|                                          | CSADIN                              | This internal chip-select, when Port A is configured as a low-order<br>address/data bus in the track mode controls the input direction of Port A.<br>CSADIN is gated externally to the PAD by the internal read signal. When<br>CSADIN and a read operation are active, <b>data presented on Port A</b><br><b>flows out of AD0/A0–AD7/A7</b> . This chip-select can be placed on any<br>boundary that is a function of one product term of the PAD inputs.<br>See Figure 5B.   |

| ×                                        | CSADOUT1                            | This internal chip-select, when Port A is configured as a low-order<br>address/data bus in track mode, controls the output direction of Port A.<br>CSADOUT1 is gated externally to the PAD by the ALE signal. When<br>CSADOUT1 and the ALE signal are active, the <b>address presented on</b><br><b>AD0/A0–AD7/A7 flows out of Port A</b> . This chip-select can be placed on<br>any boundary that is a function of one product term of the PAD inputs.<br>See Figure 5B.      |

| obsolet                                  | CSADOUT2                            | This internal chip-select, when Port A is configured as a low-order<br>address/data bus in the track mode, controls the output direction of Port A.<br>CSADOUT2 must include the write-cycle control signals as part of its<br>product term. When CSADOUT2 is active, the <b>data presented on</b><br><b>AD0/A0–AD7/A7 flows out of Port A</b> . This chip-select can be placed on<br>any boundary that is a function of one product term of the PAD inputs.<br>See Figure 5B. |

|                                          | PAD B Outputs                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                          | CS0–CS3                             | These chip-select outputs can be routed through Port B. Each of them is a function of up to four product terms of the PAD inputs.                                                                                                                                                                                                                                                                                                                                              |

|                                          | CS4–CS7                             | These chip-select outputs can be routed through Port B. Each of them is a function of up to two product terms of the PAD inputs.                                                                                                                                                                                                                                                                                                                                               |

|                                          | CS8–CS10                            | These chip-select outputs can be routed through Port C. See Figure 4, Note 3. Each of them is a function of one product term of the PAD inputs.                                                                                                                                                                                                                                                                                                                                |

10.0 I/O Port Functions The PSD3XX has three I/O ports (Ports A, B, and C) that are configurable at the bit level. This permits great flexibility and a high degree of customization for specific applications. The next section describes the control registers for the ports. Following that are sections that describe each port. Figures 5 through 7 show the structure of Ports A through C, respectively.

Note: any unused input should be connected directly to ground or pulled up to V<sub>CC</sub> (using a  $10K\Omega$  to  $100K\Omega$  resistor).

#### 10.1 CSIOPORT Registers

Control of the ports is primarily handled through the CSIOPORT registers. There are 24 bytes in the address space, starting at the base address labeled CSIOPORT. Since the PSD3XX uses internal address lines A15-A8 for decoding, the CSIOPORT space will occupy 2 Kbytes of memory, on a 2 Kbyte boundary. This resolution can be improved to reduce wasted address space by connecting lower order address lines (A7 and below) to Port C. Using this method, resolution down to 256 Kbytes may be achieved. The CSIOPORT space must be defined in your PSDsoft design file. The following tables list the registers located in the CSIOPORT space.

#### 16-Bit Users Note

When referring to Table 5B, realize that Ports A and B are still accessible on a byte basis. Note: When accessing Port B on a 16-bit data bus, BHE must be low.

|                                | Register Name                         | <i>Offset (in hex)<br/>from CSIOPORT<br/>Base Address</i> | Type of<br>Access<br>Allowed |

|--------------------------------|---------------------------------------|-----------------------------------------------------------|------------------------------|

| Port A Pin R                   | egister                               | +2                                                        | Read                         |

| Port A Direc                   | ion Register                          | +4                                                        | Read/Write                   |

| Port A Data                    | Register                              | +6                                                        | Read/Write                   |

| Port B Pin R                   | egister                               | +3                                                        | Read                         |

| Port B Direc                   | ion Register                          | +5                                                        | Read/Write                   |

| Port B Data                    | Register                              | +7                                                        | Read/Write                   |

| Power Mana                     | gement Register (Note 1)              | +10                                                       | Read/Write                   |

| Page Regist                    | er                                    | +18                                                       | Read/Write                   |

| NOTE: 1. ZPSD<br>Table 5B. CSI | only.<br>OPORT Registers for 16-Bit L | Data Busses                                               |                              |

| ,                              | Register Name                         | Offset (in hex)<br>from CSIOPORT<br>Base Address          | Type of<br>Access<br>Allowed |

| Table 5A. | CSIOPORT I | Registers for | 8-Bit Data | Busses | ( |

|-----------|------------|---------------|------------|--------|---|

|-----------|------------|---------------|------------|--------|---|

| Table 5B. CSIOPORT Registers for 16-Bit Data Busses |

|-----------------------------------------------------|

|-----------------------------------------------------|

| Register Name                      | <i>Offset (in hex)<br/>from CSIOPORT<br/>Base Address</i> | Type of<br>Access<br>Allowed |

|------------------------------------|-----------------------------------------------------------|------------------------------|

| Port A/B Pin Register              | +2                                                        | Read                         |

| Port A/B Direction Register        | +4                                                        | Read/Write                   |

| Port A/B Data Register             | +6                                                        | Read/Write                   |

| Power Management Register (Note 1) | +10                                                       | Read/Write                   |

| Page Register                      | +18                                                       | Read/Write                   |

NOTE: 1. ZPSD only.

10.0 I/O Port Functions (cont.)

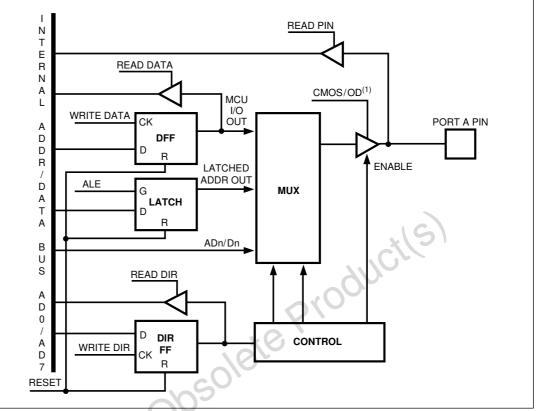

#### 10.2 Port A (PA0-PA7)

The control registers of Port A are located in CSIOPORT space; see Table 5.

#### 10.2.1 Port A (PA0-PA7) in Multiplexed Address/Data Mode

Each pin of Port A can be individually configured. The following table summarizes what the control registers (in CSIOPORT space) for Port A do:

| Register Name             | 0 Value                             | 1 Value                             | Default<br>Value<br>(Note 1) |

|---------------------------|-------------------------------------|-------------------------------------|------------------------------|

| Port A Pin Register       | Sampled logic level<br>at pin = '0' | Sampled logic level<br>at pin = '1' | х                            |

| Port A Direction Register | Pin is configured<br>as input       | Pin is configured<br>as output      | 0                            |

| Port A Data Register      | Data in DFF = '0'                   | Data in DFF = '1'                   | 0                            |

NOTE: 1. Default value is the value after reset.

#### MCU I/O Mode

The default configuration of Port A is MCU I/O. In this mode, every pin can be set (at runtime) as an input or output by writing to the respective pin's direction flip-flop (DIR FF, Figure 5A). As an output, the pin level can be controlled by writing to the respective pin's data flip-flop (DFF, Figure 5A). The Pin Register can be read to determine logic level of the pin. The contents of the Pin Register indicate the true state of the PSD driving the pin through the DFF or an external source driving the pin. Pins can be configured as CMOS or open-drain using ST's PSDsoft software. Open-drain pins require external pull-up resistors.

#### Latched Address Output Mode

Alternatively, any bit(s) of Port A can be configured to output low-order demultiplexed address bus bit. The address is provided by the internal PSD address latch, which latches the address on the trailing edge of ALE/AS. Port A then outputs the desired demultiplexed address bits. This feature can eliminate the need for an external latch (for example: 74LS373) if you have devices that require low-order latched address bits. Although any pin of Port A may output an address signal, the pin is position-dependent. In other words, pin PA0 of Port A may only pass A0, PA1 only A1, and so on.

#### Track Mode

10501e

Track Mode sets the entire port to track the signals on AD0/A0-AD7/A7, depending on specific address ranges defined by the PAD's CSADIN, CSADOUT1, and CSADOUT2 signals. This feature lets the user interface the microcontroller to shared external resources without requiring external buffers and decoders. In Track Mode, Port A effectively operates as a bi-directional buffer, allowing external MCUs or host processors to access the local data bus. Keep the following information in mind when setting up Track Mode:

□ The direction is controlled by:

- ALE/AS

- RD/E or RD/E/DS (DS on non-3X1 devices only)

- $\overline{WR}$  or  $R/\overline{W}$

- PAD outputs CSADOUT1, CSADOUT2, and CSADIN defined in PSDsoft design.

- □ When CSADOUT1 and ALE/AS are true, the address on AD0/A0-AD7/A7 is output on Port A. Note: carefully check the generation of CSADOUT1 to ensure that it is stable during the ALE/AS pulse.

- □ When CSADOUT2 is active and a write operation is performed, the data on the AD0/A0-AD7/A7 input pins flows out through Port A.

- □ When CSADIN is active and a read operation is performed, the data on Port A flows out through the AD0/A0-AD7/A7 pins.

- Dert A is tri-stated when none of the above conditions exist.

10.0 I/O Port Functions (cont.)

#### 10.2.2 Port A (PA0-PA7) in Non-Multiplexed Address/Data Mode

In this mode, Port A becomes the low-order data bus byte of the chip. When reading an internal location, data is presented on Port A pins to the MCU. When writing to an internal location, data present on Port A pins from the MCU is written to the desired location.

#### Figure 5A. Port A Pin Structure

NOTE: 1. CMOS/OD determines whether the output is open drain or CMOS.

#### Figure 5B. Port A Track Mode

**NOTE:** 1. The expression for CSADOUT2 must include the following write operation cycle signals: For CRRWR = 0, CSADOUT2 must include  $\overline{WR} = 0$ . For CRRWR = 1, CSADOUT2 must include E = 1 and R/W = 0.

10. I/O Port Functions (cont.)

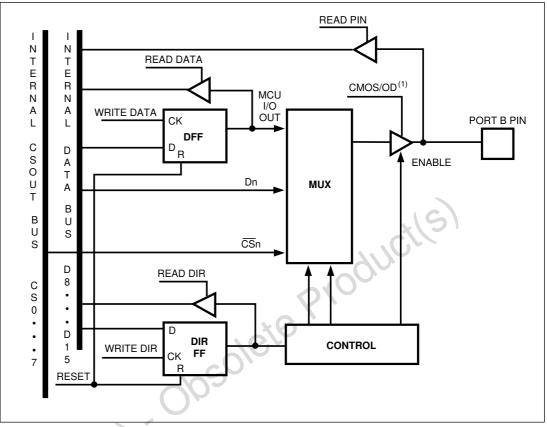

#### 10.3 Port B (PB0-PB7)

The control registers of Port B are located in CSIOPORT space; see Table 5A and 5B.

#### 10.3.1 Port B (PB0-PB7) in Multiplexed Address/Data Mode

Each pin of Port B can be individually configured. The following table summarizes what the control registers (in CSIOPORT space) for Port B do:

| Register Name             | 0 Value                             | 1 Value                             | Default<br>Value<br>(Note 1) |

|---------------------------|-------------------------------------|-------------------------------------|------------------------------|

| Port B Pin Register       | Sampled logic level<br>at pin = '0' | Sampled logic level<br>at pin = '1' | х                            |

| Port B Direction Register | Pin is configured<br>as input       | Pin is configured<br>as output      | 0                            |

| Port B Data Register      | Data in DFF = '0'                   | Data in DFF = '1'                   | 0                            |

NOTE: 1. Default value is the value after reset.

#### MCU I/O Mode

The default configuration of Port B is MCU I/O. In this mode, every pin can be set (at run-time) as an input or output by writing to the respective pin's direction flip-flop (DIR FF, Figure 6). As an output, the pin level can be controlled by writing to the respective pin's data flip-flop (DFF, Figure 6). The Pin Register can be read to determine logic level of the pin. The contents of the Pin Register indicate the true state of the PSD driving the pin through the DFF or an external source driving the pin. Pins can be configured as CMOS or open-drain using ST's PSDsoft software. Open-drain pins require external pull-up resistors.

#### Chip Select Output

Alternatively, each bit of Port B can be configured to provide a chip-select output signal from PAD B. PB0-PB7 can provide CS0-CS7, respectively. The functionality of these pins is not limited to chip selects only; they can be used for generic combinatorial logic as well. Each of the CS0-CS3 signals is comprised of four product terms, and each of the CS4-CS7 signals is comprised of two product terms.

10. I/O Port Functions (cont.)

#### 10.3.2 Port B (PB0-PB7) in 16-bit Multiplexed Address/Data Mode